# VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

BRNO UNIVERSITY OF TECHNOLOGY

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ ÚSTAV MIKROELEKTRONIKY

FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION DEPARTMENT OF MICROELECTRONICS

## UNCONVENTIONAL CIRCUIT ELEMENTS FOR LADDER FILTER DESIGN

DOKTORSKÁ PRÁCE DOCTORAL THESIS

AUTOR PRÁCE AUTHOR ING. MAHMOUD SHAKTOUR

VEDOUCÍ PRÁCE SUPERVISOR PROF. ING. DALIBOR BIOLEK, CSc.

BRNO 2011

### ABSTRACT

Frequency filters are linear electric circuits that are used in wide area of electronics. They are also the basic building blocks in analogue signal processing.

In the last decade, a huge number of active building blocks for analogue signal processing were introduced. However, there is still the need to develop new active elements that offer new possibilities and better parameters. The current-, voltage-, or mixed-mode analog circuits and their various aspects are discussed in the thesis. This work reflects the trend of low-power (LP) low-voltage (LV) circuits for portable electronic and mobile communication systems and the problems of their design. The need for high-performance LV circuits encourages the analog designers to look for new circuit architectures and new LV techniques.

This thesis presents various active elements such as Operational Transconductance Amplifier (OTA), Current Conveyor of Second Generation (CCII), and Current Differencing Transconductance Amplifier (CDTA), and introduces novel ones, such as Voltage Differencing Transconductance Amplifier (VDTA) and Voltage Differencing Voltage Transconductance Amplifier (VDVTA). All the above active elements were also designed in CMOS bulk-driven technology for LP LV applications.

This thesis is also focused on replacement of conventional inductors by synthetic ones in passive LC ladder filters. These replacements can lead to the synthesis of active filters with interesting parameters.

#### **KEYWORDS**

Analog signal processing, current-mode, voltage-mode, frequency filter, first-order allpass filter, universal filter, KHN, active floating inductance simulator, OTA, CCII, CDTA, DVCC, VDTA, VDVTA.

## ANOTACE

Kmitočtové filtry jsou lineární elektrické obvody, které jsou využívány v různých oblastech elektroniky. Současně tvoří základní stavební bloky pro analogové zpracování signálů.

V poslední dekádě bylo zavedeno množství aktivních stavebních bloků pro analogové zpracování signálů. Stále však existuje potřeba vývoje nových aktivních součástek, které by poskytovaly nové možnosti a lepší parametry. V práci jsou diskutovány různé aspekty obvodů pracujících v napěťovém, proudovém a smíšném módu. Práce reaguje na dnešní potřebu nízkovýkonových aplikací pro přenosné přístroje a mobilní komunikační systémy a na problémy jejich návrhu. Potřeba těchto výkonných nízkonapěťových zařízení je výzvou návrhářů k hledání nových obvodových topologií a nových nízkonapěťových technik.

V práci je popsána řada aktivních prvků, jako například operační transkonduktanční zesilovač (OTA), proudový konvejor II. generace (CCII) a CDTA (Current Differencing Transconductance Amplifier). Dále jsou navrženy nové prvky, jako jsou VDTA (Voltage Differencing Transconductance Amplifier) a VDVTA (Voltage Differencing Voltage Transconductance Amplifier). Všechny prvky byly rovněž tyto implementovány pomocí "bulk-driven" techniky CMOS s cílem realizace nízkonapěťových aplikací.

Tato práce je rovněž zaměřena na náhrady klasických induktorů syntetickými induktory v pasivních LC příčkových filtrech. Tyto náhrady pak mohou vést k syntéze aktivních filtrů se zajímavými vlastnostmi.

## KLÍČOVÁ SLOVA

Analogové zpracování signálů, proudový mód, napěťový mód, kmitočtový filtr, fázovací článek 1. řádu, univerzální filtr, KHN, simulátor plovoucího induktoru, OTA, CCII, CDTA, DVCC, VDTA, VDVTA.

SHAKTOUR, M. *Unconventional Circuit Elements for Ladder Filter Design:* doctoral thesis. Brno: Brno University of Technology, Faculty of Electrical Engineering and Communication, Department of Microelectronics, 2011. 108 p. Supervised by prof. Ing. Dalibor Biolek, CSc.

## DECLARATION

I declare that I have elaborated my doctoral thesis on the theme of "Unconventional Circuit Elements for Ladder Filter Design" independently, under the supervision of the doctoral thesis supervisor and with the use of technical literature and other sources of information which are all quoted in the thesis and detailed in the list of literature at the end of the thesis.

As the author of the doctoral thesis I furthermore declare that, concerning the creation of this doctoral thesis, I have not infringed any copyright. In particular, I have not unlawfully encroached on anyone's personal copyright and I am fully aware of the consequences in the case of breaking Regulation § 11 and the following of the Copyright Act No 121/2000 Vol., including the possible consequences of criminal law resulted from Regulation § 152 of Criminal Act No 140/1961 Vol.

Brno, 06. 04. 2011.

(author's signature)

## Acknowledgments

I would like to express my gratitude to my supervisor, Prof. Dalibor Biolek, whose expertise, understanding, and patience, added considerably to my graduate experience. No teacher in my career has had a larger influence on my development than Prof. Dalibor Biolek. He has always had an open door for questions, comments, or

discussions.

My thanks also goes to all those who have provided me with advice and assistance throughout my four years of doctoral study at the Brno University of Technology.

Finally, I thank my family, especially my mother and father, my wife, Zayneb for their support during this process and throughout my life. Everything that I have and will accomplish is a direct reflection of their unending love and encouragement.

## LIST OF ABBREVIATIONS

| ABB     | Active Building Block                                   |

|---------|---------------------------------------------------------|

| AP      | All-Pass                                                |

| BJT     | Bipolar Junction Transistor                             |

| ВОТА    | Balanced-Output Operational Transconductance Amplifier  |

| BP      | Band-Pass                                               |

| BS      | Band-Stop                                               |

| CCII    | Second-generation Current Conveyor                      |

| CCII+/- | Dual-Output Second-generation Current Conveyor          |

| CCs     | Current Conveyors                                       |

| CDBA    | Current Differencing Buffered Amplifier                 |

| CDTA    | Current Differencing Transconductance Amplifier         |

| CDU     | Current Differencing Unit                               |

| CE      | Characteristic Equation                                 |

| CF      | Current Follower                                        |

| СМ      | Current Mode                                            |

| CMOS    | Complementary Metal Oxide Semiconductor                 |

| DVCC    | Differential Voltage Current Conveyor                   |

| FDNR    | Frequency Dependent Negative Resistor                   |

| HP      | High-Pass                                               |

| KHN     | Kerwin-Huelsman-Newcomb                                 |

| LP      | Low-Pass                                                |

| MISO    | Multi-Input Single-Output                               |

| MOSFET  | Metal Oxide Semiconductor Field Effect Transistor       |

| OTA     | Operational Transconductance Amplifier                  |

| SIMO    | Single-Input Multi-Output                               |

| SITO    | Single-Input Three-Outputs                              |

| SNAP    | Symbolic Network Analysis Program                       |

| SPICE   | Simulation Program with Integrated Circuit Emphasis     |

| VC      | Voltage Conveyor                                        |

| VDTA    | Voltage Differencing Transconductance Amplifier         |

| VDVTA   | Voltage Differencing Voltage Transconductance Amplifier |

| VM      | Voltage Mode                                            |

|         |                                                         |

## LIST OF SYMBOLS

a, b coefficients of general transfer function

- *a<sub>i</sub>* coefficients of non-cascade synthesis

- C capacitance

- D denominator of transfer function

- f frequency

- $f_0$  characteristic frequency

- $\phi$  phase of all-pass filter

- G conductance

- $g_m$  transconductance of the OTA

- *R* resistance

- $V_{DD}$ ,  $V_{SS}$  supply voltages of CMOS structures

W/L CMOS transistor dimensions (Width / Length)

X, Y, Z+, Z- input or output, current or voltage terminals of the CCII

Vin+, Vin-, Iout input or output, current or voltage terminals of the OTA

p, n,  $x_+$ ,  $x_-$  input or output, current of the CDTA

- $V_p$ ,  $V_n$ ,  $x_+$ ,  $x_-$  input or output, current or voltage terminals of the VDTA

- Y admittance

- Z impedance

## CONTENTS

| 1. State of the art                            |                    |

|------------------------------------------------|--------------------|

| 2. Thesis objectives                           |                    |

| 3. Active building blocks and their properties |                    |

| 3.1. Operational Transconductance Amplifier (O | DTA)23             |

| 3.1.1. Operations using ideal OTA              |                    |

| • Voltage Amplification using OTA              |                    |

| • A Voltage – Variable Resistor (VVR)          |                    |

| • Voltage summation using OTA                  |                    |

| Integrator using OTA                           |                    |

| 3.1.2. CMOS Implementation of OTA              |                    |

| 3.2. Current Conveyor of Second Generation (C  | 27 CII)            |

| 3.2.1. Operations using the ideal CCII         |                    |

| Amplifiers using CCII                          |                    |

| Integrators using CCII                         |                    |

| Adders using CCII                              |                    |

| • Differentiators using CCII                   |                    |

| 3.2.2. Bulk-driven CCII± based on Bulk-driv    | en OTA 31          |

| 3.2.3. Bulk-driven OTA with gm adjustable v    | via external R     |

| 3.3. Current Differencing Transconductance An  | nplifier (CDTA)41  |

| 3.3.1. Operations using the ideal CDTA         |                    |

| • Integrator using CDTA                        |                    |

| • Current Summation using CDTA                 |                    |

| 3.3.2. CMOS Implementation of CDTA             |                    |

| 3.4. Voltage Differencing Transconductance Ar  | nplifier (VDTA) 49 |

| 3.4.1. Operations using the ideal VDTA         |                    |

| Integrator using VDTA                          |                    |

|                                                |                    |

| Current Summation using VDTA                                                   | 51   |

|--------------------------------------------------------------------------------|------|

| 3.4.2. CMOS Implementation of VDTA                                             | 51   |

| 3.5. Voltage Differencing Voltage Transconductance Amplifier (VDVTA)           | 53   |

| 3.6. Differential Voltage Current Conveyor (DVCC)                              | 54   |

| 4. LC ladder simulation and other applications of active elements              | 57   |

| 4.1. Optimization of ladder filters with GmC simulation of floating inductors  | 57   |

| 4.1.1. MAX435 – a commercial OTA                                               | 57   |

| 4.1.2. Synthetic inductor based on MAX435                                      | 57   |

| 4.1.3. LC Ladder simulation                                                    | 59   |

| 4.2. Commercial active elements for filter implementation                      | 65   |

| 4.2.1.Floating inductor replacement via "super-transistors"                    | 67   |

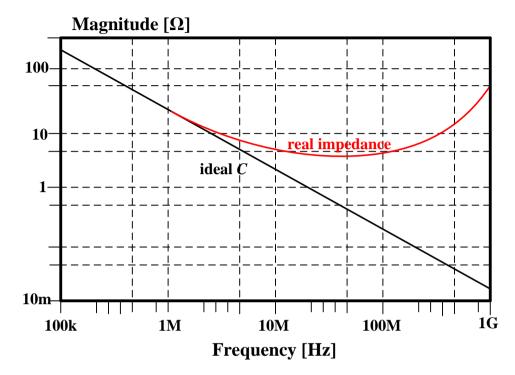

| 4.2.2. Real properties of synthetic inductor                                   | 68   |

| 4.2.3. Utilizing synthetic inductors for LC ladder simulation                  | 70   |

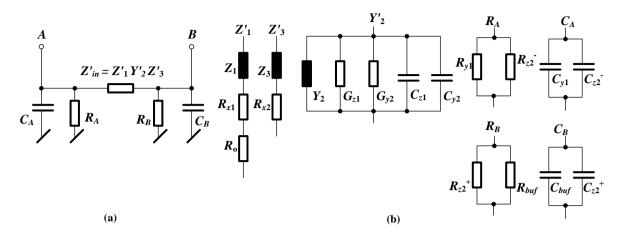

| 4.3. Floating GIC and its implementation                                       | 73   |

| 4.3.1. Introduction                                                            | 73   |

| 4.3.2. Proposed impedance converter                                            | 74   |

| 4.3.3. Analysis of the influence of parasitic impedances                       | 75   |

| 4.3.3.1. Alternative model of impedance converter                              | 75   |

| 4.3.3.2. Simulation of floating inductor                                       | 76   |

| 4.3.3.3. Simulation of floating capacitor                                      | 77   |

| 4.3.3.4. Simulation of the FDNR                                                | 78   |

| 4.3.4. Design example                                                          | 79   |

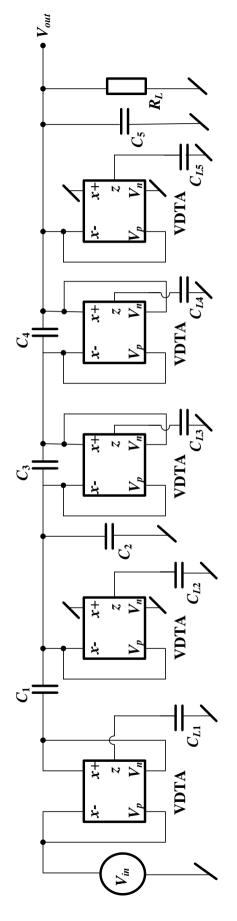

| 4.4. Voltage Differencing Transconductance Amplifier for Filter Implementation | ı 80 |

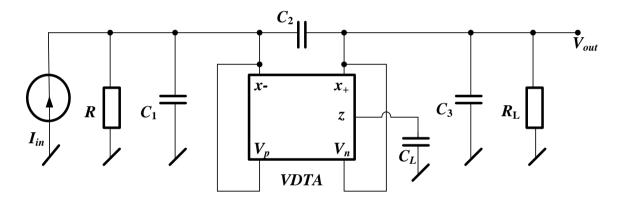

| 4.4.1. Synthetic inductor based on VDTA                                        | 81   |

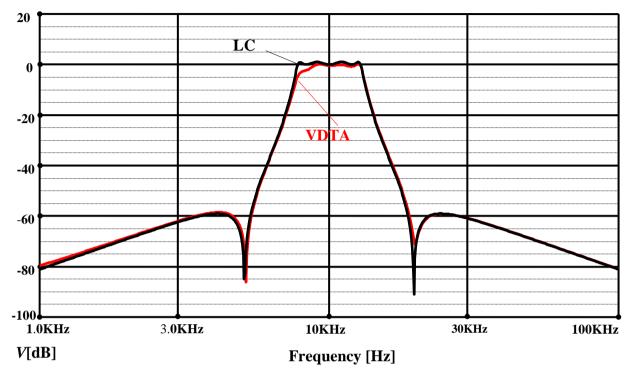

| 4.4.2. Low-pass LC Ladder simulation                                           | 82   |

| 4.4.3. Band-pass LC Ladder simulation                                          | 85   |

| 4.4.4. Design of resistor-less first-order all-pass filter using single VDVTA  | 87   |

| 4.4.5. Design of KHN filter using VDTA |    |

|----------------------------------------|----|

| 5. Conclusion                          |    |

| 6. Bibliography                        | 96 |

| 7. Appendices                          |    |

| 7.1. Appendix A                        |    |

| 7.2. Appendix B                        |    |

## LIST OF FIGURES

| Fig. 3-1: (a) OTA symbol, (b) ideal equivalent circuit.                                                      | 23 |

|--------------------------------------------------------------------------------------------------------------|----|

| Fig. 3-2: (a) Inverting and (b) noninverting voltage amplifier using OTA.                                    | 24 |

| Fig. 3-3: Grounded voltage-variable resistor using OTA                                                       | 25 |

| Fig. 3-4: Voltage summation using OTA.                                                                       | 25 |

| Fig. 3-5: Integrators using OTA, (a) voltage-mode, (b) current-mode                                          | 26 |

| Fig. 3-6: Two stages Bulk-driven OTA [54].                                                                   | 27 |

| Fig. 3-7: (a) The CCII symbol, (b) ideal equivalent circuit                                                  | 28 |

| Fig. 3-8: (a) CCII-based current amplifier, (b) CCII-based voltage amplifier.                                | 29 |

| Fig. 3-9: (a) CCII-based current integrator, (b) CCII-based voltage integrator.                              | 29 |

| Fig. 3-10: (a) CCII-based current adder, (b) CCII-based voltage adder                                        | 30 |

| Fig. 3-11: (a) CCII-based current differentiator, (b) CCII-based voltage differentiator.                     | 31 |

| Fig. 3-12: Bulk-driven CCII± based on Bulk-driven OTA.                                                       | 32 |

| Fig. 3-13: Frequency variation of the current gains $I_{Z+}/I_X$ , $I_{Z-}/I_X$ in dB of the CCII in F 3-12. |    |

| Fig. 3-14: Voltage follower between X and Y of the CCII in Fig. 3-12.                                        | 33 |

| Fig. 3-15: Current linearity between X and Y of the CCII in Fig. 3-12.                                       | 34 |

| Fig. 3-16: The X node input resistance rin, x of the CCII in Fig. 3-12.                                      | 34 |

| Fig. 3-17: The Z node output resistance rin,Z of the CCII in Fig. 3-12.                                      | 35 |

| Fig. 3-18: (a) SISO OTA with gm adjustable, (b) DISO OTA with gm adjustable                                  | 36 |

| Fig. 3-19: Bulk-driven single input single output OTA (SISO) based on CCII.                                  | 37 |

| Fig. 3-20: Bulk-driven fully differential OTA (DIDO) based on CCII and volta buffer.                         | -  |

| Fig. 3-21: DC transfer characteristics of bulk-driven fully differential OTA.                                | 40 |

| Fig. 3-22: AC transfer characteristics of bulk-driven fully differential OTA.                                | 41 |

| Fig. | 3-23:   | (a) Symbol of the CDTA, (b) its implementation by bulk-driven OTAs                                                               | 42 |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. | 3-24:   | Integrator using CDTA.                                                                                                           | 43 |

| Fig. | 3-25:   | Current summation using CDTA.                                                                                                    | 43 |

| Fig. | 3-26:   | CMOS implementation of CDTA.                                                                                                     | 44 |

| Fig. | 3-27:   | DC curves Iz versus Ip or In, for $Vz = 0$ .                                                                                     | 46 |

| Fig. | 3-28:   | Frequency responses of current gains Iz/Ip and Iz/In for $Vz = 0$                                                                | 46 |

| Fig. | 3-29:   | DC curve Vp versus Ip for evaluating small-signal input resistance of the terminal. For the n-terminal, the result is identical. | -  |

| Fig. | 3-30:   | Frequency dependence of the impedances of p- and n- terminals                                                                    | 47 |

| Fig. | 3-31:   | DC characteristics of OTA No. 3 with Rset linearization and transconductance control.                                            | 48 |

| Fig. | 3-32:   | Frequency responses of transconductances                                                                                         | 49 |

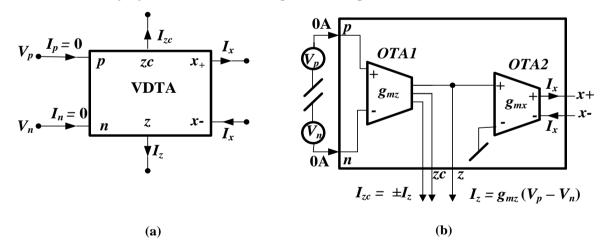

| Fig. | 3-33:   | (a) Symbol of the VDTA, (b) its implementation by OTAs.                                                                          | 50 |

| Fig. | 3-34:   | Integrator using VDTA.                                                                                                           | 51 |

| Fig. | 3-35:   | Current summation using VDTA.                                                                                                    | 51 |

| Fig. | 3-36:   | CMOS implementation of VDTA.                                                                                                     | 51 |

| Fig. | 3-37:   | (a) Symbol of the VDVTA, (b) its implementation by OTA                                                                           | 53 |

| Fig. | 3-38:   | CMOS implementation of VDVTA.                                                                                                    | 51 |

| Fig. | 3-39:   | (a) DVCCII+ model, (b) DVCII+ using diamond transistors and buffer                                                               | 55 |

| Fig. | 3-40:   | Implementation of DVCII+ by current conveyor and by OTA.                                                                         | 56 |

| Fig. | 3-41:   | CMOS Implementation of DVCII+ by Bulk-driven current conveyor and OTA.                                                           | -  |

| Fig. | 4-1: \$ | Synthetic inductor and the corresponding signal flow graphs                                                                      | 58 |

| Fig. | 4-2: 5  | 5MHz lowpass ladder filter.                                                                                                      | 59 |

| Fig. | 4-3: /  | Active ladder simulation by means of synthetic inductors and OTAs                                                                | 60 |

| Fig. | 4-4: I  | Results of the AC analysis of LC ladder from Fig. 4-2 (a) for $Iin = 10mA$                                                       | 61 |

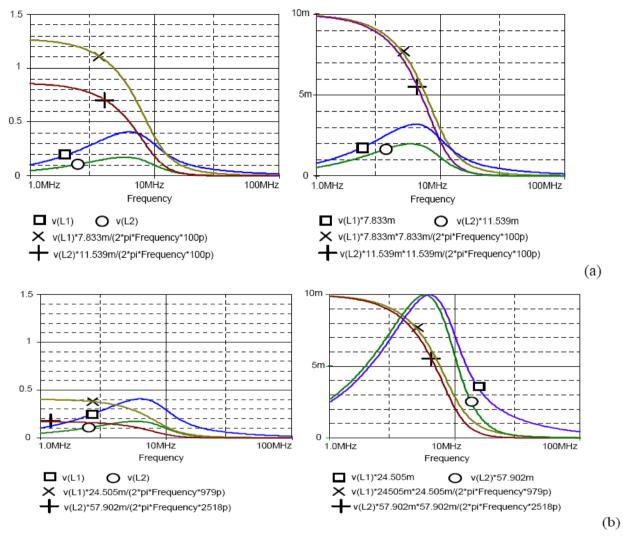

| Fig. 4-5: PSpice analysis of synthetic inductors by means of dependences described by Signal- Flow-Graphs from Fig. 4-1, (a) before, (b) after optimizing the dynamic range                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

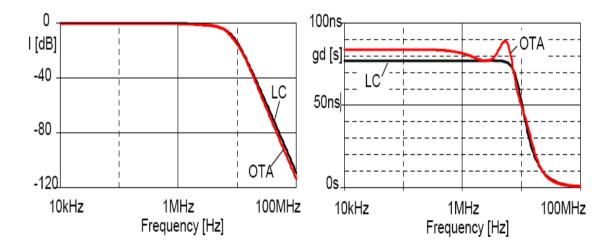

| Fig. 4-6: Frequency responses of ideal LC ladder (LC) and optimized active filter 64                                                                                                       |

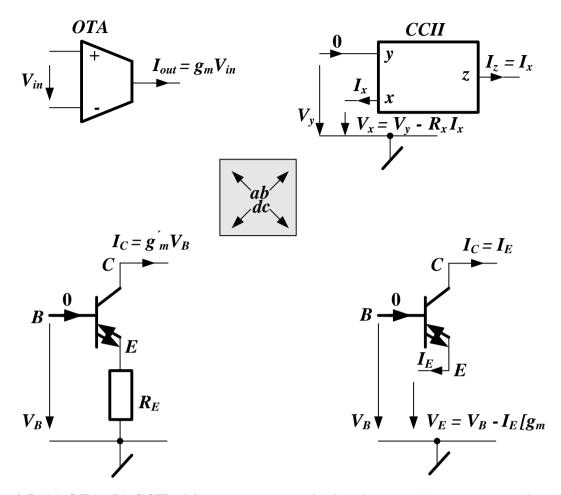

| Fig. 4-7: (a) OTA, (b) CCII with nonzero x-terminal resistance, (c) "super-transistor" as CCII, (d) "super-transistor" with a degeneration RE resistance as single-input single-output OTA |

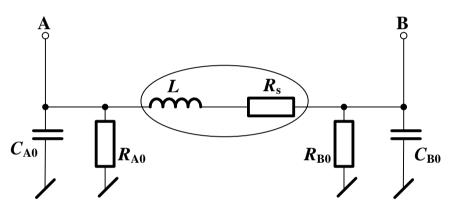

| Fig. 4-8: Simulation of floating inductor                                                                                                                                                  |

| Fig. 4-9: Model of the synthetic inductor in Fig. 5-8, with the real effects considered. 70                                                                                                |

| Fig. 4-10: 5MHz LC ladder filter                                                                                                                                                           |

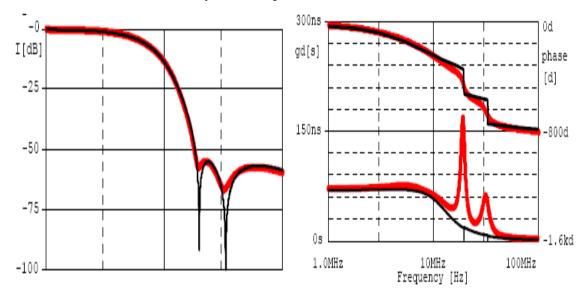

| Fig. 4-11: Active implementation of the filter from Fig. 5-10. Blocks "L1" and "L2" are synthetic inductors from Fig. 4-8                                                                  |

| Fig. 4-12: Frequency responses of the active filter from Fig. 4-11                                                                                                                         |

| Fig. 4-13: (a) Proposed impedance converter, (b) Parasitic impedances of active element                                                                                                    |

| Fig. 4-14: Model of the impedance converter from Fig. 4-13, with real effects taken into consideration. The black impedances in (b) are working, the remaining are parasitic               |

| Fig. 4-15: Simulation of the frequency dependence of the impedance of the synthetic floating capacitor                                                                                     |

| Fig. 4-16: (a) Synthetic inductor circuit employing DISO OTA and SIDO OTA, (b) simplified representation of the synthetic inductor by VDTA                                                 |

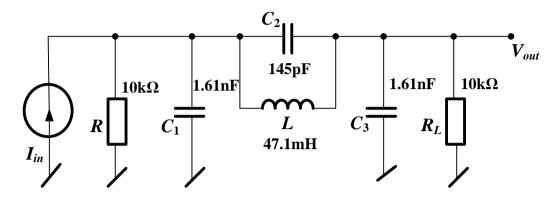

| Fig. 4-17: 25kHz LC ladder filter                                                                                                                                                          |

| Fig. 4-18: Active implementation of the filter from Fig. 4-17                                                                                                                              |

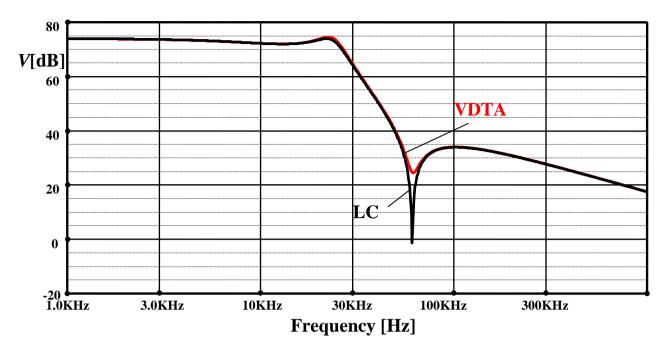

| Fig. 4-19: The frequency responses of ideal LC ladder and VDTA-based active filter. 84                                                                                                     |

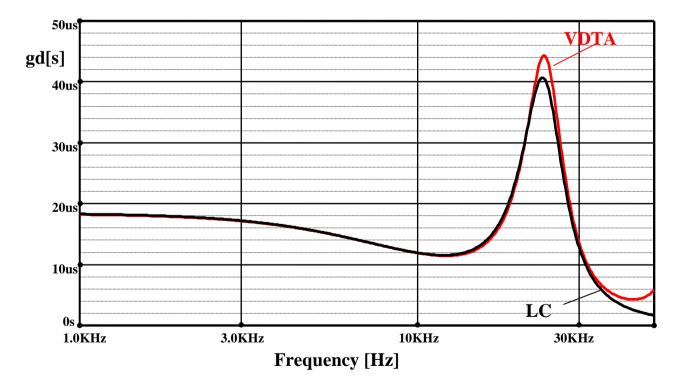

| Fig. 4-20: The group delay response of ideal LC ladder and VDTA-based active filter.                                                                                                       |

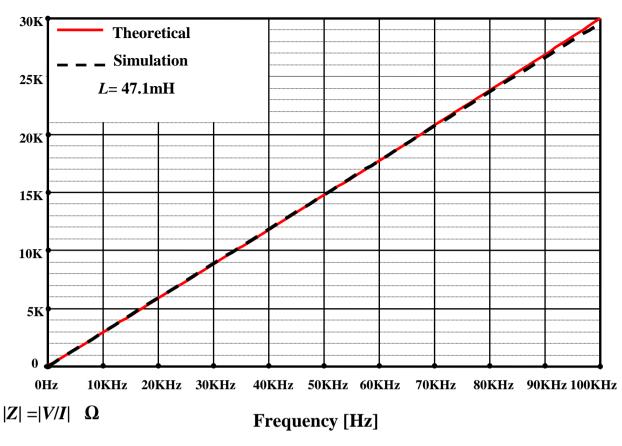

| Fig. 4-21:The impedance values relative to frequency of the ideal and simulated inductors                                                                                                  |

| Fig. 4-22: Band-pass 8th order LC ladder filter                                                                                                                                            |

| Fig. 4-23: Active implementation of the filter from Fig. 4-22                                                                                                                              |

| Fig. 4-24: | The frequency responses of ideal LC ladder and VDTA-based active filter. 8                              | 7 |

|------------|---------------------------------------------------------------------------------------------------------|---|

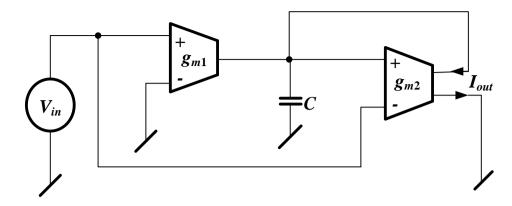

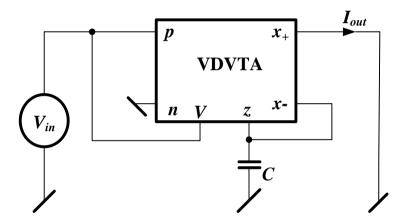

| Fig. 4-25: | The all-pass filter by OTAs                                                                             | 8 |

| Fig. 4-26: | Implementation of all-pass filter in Fig. 4-25 by using VDVTA                                           | 8 |

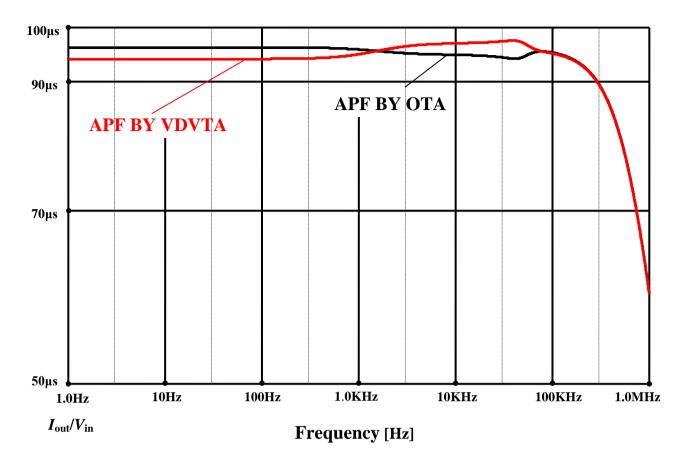

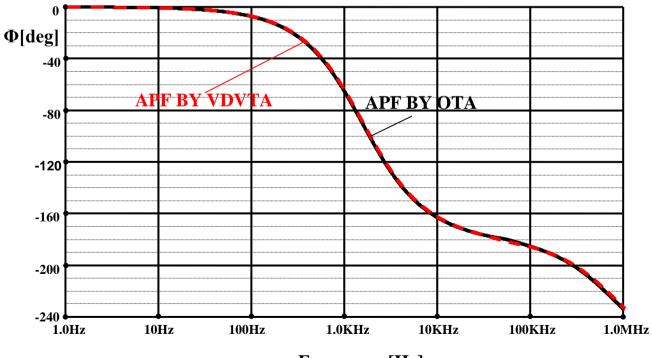

| Fig. 4-27: | Amplitude frequency responses of all-pass filters                                                       | 9 |

| Fig. 4-28: | Phase frequency responses of all-pass filters                                                           | 9 |

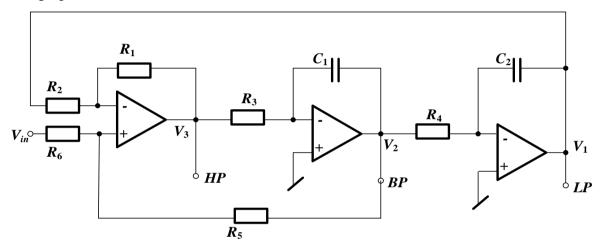

| Fig. 4-29: | Classical structure of the KHN filter9                                                                  | 0 |

|            | The corresponding flow-graph of KHN in Fig. 4-29. For $R_1 = R_2 = R_5 = R_1$<br>$b_2 = b_1 = -b_0 = 1$ |   |

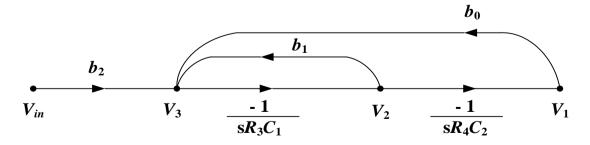

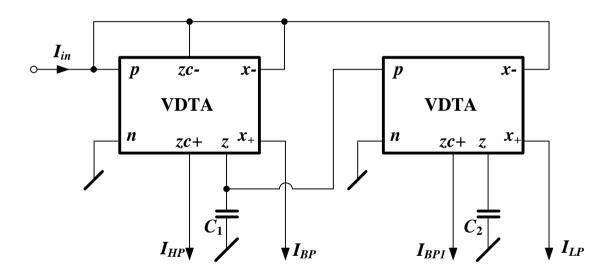

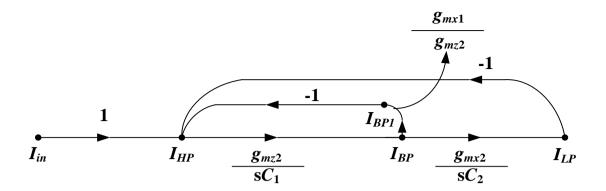

| Fig. 4-31: | VDTA-based CM KHN circuit                                                                               | 1 |

| Fig. 4-32: | The corresponding flow-graph of KHN in Fig. 4-31                                                        | 2 |

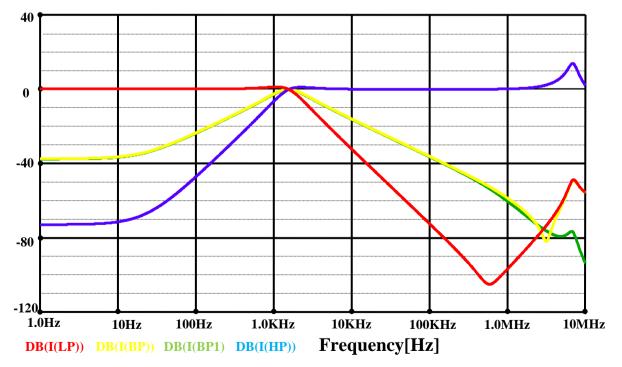

| -          | : Results of circuit simulations for CM KHN circuit using CMOS-base                                     | - |

## LIST OF TABLES

| 3-1: Simulation results of the Bulk-driven OTA.                                      | 27 |

|--------------------------------------------------------------------------------------|----|

| 3-2: Simulation results of the Bulk-driven CCII                                      | 35 |

| 3-3: Aspect ratios of the transistors used in the CCII                               | 39 |

| 3-4: Aspect ratios of the transistors used in the voltage buffer                     | 39 |

| 3-5: Variations of $g_m$ by $R_{adj}$ .                                              | 41 |

| 3-6: Simulation results of the Bulk-driven CDTA.                                     | 49 |

| 4-1: Parameters of elements of the synthetic inductors before and after optimization | 62 |

| 4-2: Maximum values of inductor voltages and currents before and after optimization. | 63 |

### INTRODUCTION

Filters are widely used in analog signal processing [1] to select the particular frequency. Voltage-mode and current-mode circuits such as current conveyors [2] and current feed back operational amplifiers [3] are getting much attention as compared to other active elements due to wider bandwidth, simple circuitry, low power consumptions and dynamic ranges.

In the last decade, a huge number of active building blocks were introduced for analogue signal processing. However, there is still the need to develop new active elements that offer new and better advantages. This thesis is, therefore, focused on definition of other novel analog building blocks (ABBs) and, furthermore, novel filter structure designs.

In the present days, a number of trends can be noticed in the area of analogue filter and oscillator design, namely reducing the supply voltage of integrated circuits and transition to the current-mode [4]. On the other hand, current-, voltage- and mixed-mode analog circuits design still receives considerable attention of many researches. Therefore, the proposed circuits in this work are working in current-, voltage-, or mixed-mode.

This thesis work discusses the low-voltage analog active elements and their various aspects. The need of high speed, high performance, low power circuits because of the advent of the portable electronic and mobile communication systems and difficulties faced in achieving that in today, this need for high performance LV circuits give encourages the analog designers to look for new circuit architectures, and new LV techniques. Therefore the proposed circuits are implemented using bulk-driven CMOS structures.

The thesis is organized as follows: Chapter 3 presents various active elements. These active building blocks are further used in this thesis for various filters. This Chapter also introduces novel elements defined within this work. As applications, several current, voltage and mixed-mode filter structures utilizing: Operational Transconductance Amplifier (OTA), Current Conveyor of Second Generation (CCII), Current Differencing Transconductance Amplifier (VDTA), and Voltage Differencing Transconductance Amplifier (VDTA), and Voltage Differencing Voltage Transconductance Amplifier (VDVTA) are presented in Chapter 4.

Chapter 4 is focused on replacement of conventional inductors by synthetic ones in passive LC ladder filters. It belongs to well-known methods of high-order low-sensitivity filter design. An efficient way of simulating the floating inductor consists in replacing the inductor by these active building blocks. Part of this Chapter focuses on such second-order filter structures that can provide all standard filter responses without changing the circuit topology.

Special attention is paid to Kerwin– Huelsman–Newcomb structure that enables independent control of the quality factor Q and characteristic frequency  $\omega_0$ .

To verify the behavior of the proposed circuits, defined active elements are implemented using bulk-driven CMOS structures.

### 1. State of the art

In the last decade, a huge number of active building blocks (ABBs) were introduced for analogue signal processing.

Due to disadvantages of conventional inductors, active element-based inductor design is very desirable to designers today. During the last few decades, various floating inductors have been created using different high-performance active building blocks. That is why replacement of conventional inductors by synthetic ones in passive LC ladder filters belongs to well-known methods of high-order low-sensitivity filter design.

The current conveyor (CC) is the basic building block of a number of contemporary applications both in the current and the mixed modes. The principle of the current conveyor of the first generation was published in 1968 by K. C. Smith and A. S. Sedra [5]. Two years later, today's widely used second-generation CCII was described in [6], and in 1995 the third-generation CCIII [7]. However, initially, during that time, the current conveyor did not find many applications because its advantages compared to the classical operational amplifier (Op Amp) were not widely appreciated and any IC implementation of Current Conveyors was not available commercially as an off-the-shelf item.

Today, the current conveyor is considered a universal analog building block with wide spread applications in the current-, voltage-, and mixed-mode signal processing. Its features find most applications in the current mode, when its so-called voltage input y is grounded and the current, flowing into the low-impedance input x, is copied by a simple current mirror into the z output.

The demand for a multiple-output current conveyor led to the DO-CCII (Dual-Output CCII), which provides currents Iz of both directions, thus combining both the positive and the negative CCII in a single device [8]. If both currents are of the same polarity, the conveyors are of the CFCCIIp or CFCCIIn types (Current Follower CCII), where the symbol p or n means positive or negative current conveyor [9]. Another generalization is represented by the so-called DVCCII (Differential Voltage Current Conveyor) [10], in which the original "voltage" input y is split into a pair of inputs y1 and y2. The voltage of the x terminal is then given by the voltage difference of the voltage inputs. This offers more freedom during the design of voltage- and mixed-mode applications.

OTA (Operational Transconductance Amplifier) [11] belongs to the most widespread active elements for on-chip implementation of fast frequency filters.

It acts as a voltage-controlled current source with the possibility of electronic adjustment of transconductance  $g_m$ .

Recently, the MO-OTA (Multiple Output OTA) has appeared as a generalization of BOTA (Bipolar OTA) and its applications in economical biquadratic filters [12], [13]. However, the drawbacks of such applications are not sufficiently emphasized. Some of them are referred to in [14]: the MO-OTA applications embody relatively high sensitivities to the attainable matching error of the current gains of the current mirrors that form the multiple output of the OTA.

Using the duality principle, the voltage conveyor (VC) has been presented in 1981 [15]. As in the theory of CCs, also here the first- and second-generation VCs (VCI, VCII, IVCI, and IVCII) were described [15], [16], [17], [18]. The best known VC is the plus-type differential current voltage conveyor (DCVC+) [19] that is more often labeled as the current differencing buffered amplifier (CDBA) [20].

By the modification of the CDBA or replacement of the VF (Voltage Follower) by the operational transconductance amplifier (OTA) [21], the current differencing transconductance amplifier (CDTA) [22] has been presented.

The methodology described, which uses the CDU (Current Differencing Unit) or CF (Current Follower) or CI (Current Inverter) as the input unit, and the following simple blocks such as voltage buffer, OTA, and CCII, represents an open system.

Continuing with the variation that the input unit will now implement voltage and not current differences, the Voltage Differencing Transconductance Amplifier (VDTA) has been introduced [23].

Recently, many papers were published about the simulation of passive ladder filters via numerous types of active elements. Direct simulation via inductor replacement by a synthetic element, indirect simulation via Bruton transformation of passive RCL cell and subsequent FDNR implementation, or leap-frog techniques was used.

In such circuits, frequently used active elements are CDBAs [24-26], CAs (Current Amplifiers) [27], MCCCIIs (Multi-Output CCCIIs) [28], CDTAs [29-31], OTRAs (Operational Transresistance Amplifier) [32], VCCs (Differential Voltage Current Conveyor) [33], CCIIs and CFAs [34], [35], DO\_OTAs (Differential-Output OTAs) [36], MO\_OTAs (Multiple-Output OTAs) [37], and a combination of classical Operational Amplifiers and OTAs [38]. Common drawback of the above circuit topologies consists in the circuit complexity. For example, a floating inductor is modeled via several active devices, and the

resulting filter structure contains large number of components, including floating resistors and capacitors. One exception from this rule is represented by recently introduced building block named CBTA (Current Backward Transconductance Amplifier) which enables simulating n-th order ladder filter via n CBTAs and n grounded capacitors [39], [40].

The above state-of-the-art clearly shows the topicality of the simulation of passive ladder filters via modern active elements as well as searching for such building blocks which would enable economical synthesis of artificial inductors. During the research activities towards finishing this work, it was shown that the VDTA element which was synthesized in the first stage of the research can be a good building block for designing economical ladder simulators.

### 2. Thesis objectives

The first aim of this thesis is to define various types of novel active building blocks for the effective synthesis of filter simulating RLC ladder structure. The second aim is to perform such a synthesis.

The first part of the thesis focuses on designing a high linearity, wideband bulk-driven OTA with tunable transconductance. This OTA is then used for designing active building blocks (CDTA, VDTA, VDVTA, and DVCC). As applications, several filters structures current-, voltage- and mixed-mode by using VDTA are presented, particularly the second-order filter structures that can provide all standard filter responses without changing the circuit topology. Special attention is paid to Kerwin–Huelsman–Newcomb structure that enables independent control of the quality factor Q and characteristic frequency  $\omega_0$ .

The second part of thesis deals with LC ladder simulation on the principle of inductor replacement by synthetic inductor.

The floating inductor is synthesized via:

1. MAX435, a commercial OTA [57], [64], which appears to be an optimal circuit element for such designs. Its differential input and output can be utilized for the simplification of the well-known circuitry for simulating the floating inductor. The transconductance of MAX435 is adjusted by an external two-terminal device. In the case of linear resistor, OTA has an extremely linear I&V characteristic. The limitations of the output current can be precisely set by another external resistor.

2. "super-transistor" (S-T), which is commercially available in several versions, e.g. OPA615, SHC615, OPA860, and OPA861 [64].

3. Newly introduced VDTA and VDVTA elements [55] designed in the first part of the thesis. All the designs are verified in two steps:

In the first step, the theoretical analyses are done using SNAP software [41]. To verify the complex behavior of the proposed circuits, SPICE simulations are performed, utilizing transistor-level models of active elements.

### 3. Active building blocks and their properties

The following active elements are devices having multi ports with properties that make them useful in network synthesis [50]. Some active elements are more useful than others, depending of various design requirements.

#### **3.1. Operational Transconductance Amplifier (OTA)**

The OTAs were made commercially available for the first time in 1969 by RCA. The first publications with OTA came out in 1985, when authors in [21] presented to the general public the new CMOS OTA architectures and new filter realizations.

An ideal operational transconductance amplifier is a voltage-controlled current source, with infinite input and output impedances and frequency independent transconductance. OTA has two attractive features: 1) changing the external dc bias current or voltage can control its transconductance, and 2) It can work at high frequencies.

This research thesis focuses on the MOS implementations of the transconductance amplifiers.OTA is a voltage controlled current source.

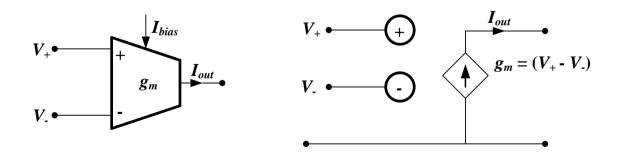

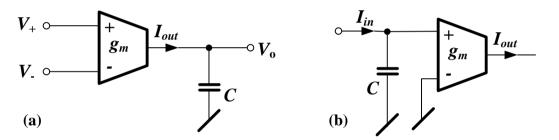

More specifically, the term "operational" comes from the fact that it takes the difference of two voltages as the input for the current conversion. The ideal OTA is a differential-input voltage-controlled current source (DVCCS). Its symbol is shown in Fig. 3-1 (a), and its operation is defined by the following equation (3-1). Both voltages  $V_+$  and  $V_-$  are with reference to ground. The equivalent circuit of the ideal OTA is shown in Fig. 3-1 (b).

(a) (b) Fig. 3-1: (a) OTA symbol, (b) ideal equivalent circuit.

$$I_{out} = g_m (V_+ - V_-) \tag{3-1}$$

Currently, the OTA elements are supplied on the market by many manufacturers [53].

A commercially available OTA elements are, for example, LT1228 (Linear Technology) or MAX435 (MAXIM-Dallas Semiconductor). The latter is a high-speed wideband transconductance amplifier (WTA) with high-impedance inputs and output. Due to its unique performance features, it is suitable for a wide variety of applications such as high-speed instrumentation amplifiers, wideband, high-speed RF filters, and high-speed differential line driver and receiver applications.

#### 3.1.1. Operations using ideal OTA

#### • Voltage Amplification using OTA

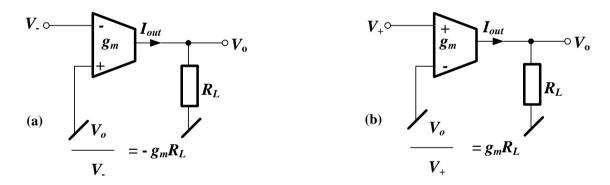

Inverting and noninverting voltage amplification can be achieved using an OTA as shown in Fig. 3-2 (a) and 3-2 (b), respectively [50]. Any desired gain can be achieved by a proper choice of gm and  $R_L$ . It should be noted that the output voltage  $V_0$  is obtained from a source with output impedance equal to  $R_L$ . Zero output impedance can be achieved only if such circuits are followed by a voltage follower.

Fig. 3-2: (a) Inverting and (b) noninverting voltage amplifier using OTA.

#### • A Voltage – Variable Resistor (VVR)

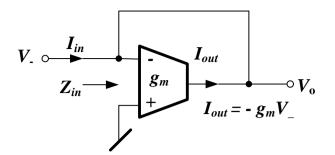

A grounded voltage-variable resistor can be easily obtained using an ideal OTA as shown in Fig. 3-3. Since  $I_{out} = -I_{in}$ , we have the following [50]:

$$Z_{in} = \frac{V_{-}}{I_{in}} = \frac{V_{-}}{-I_{out}} = \frac{V_{-}}{g_m V_{-}} = \frac{1}{g_m}$$

(3-2)

Fig. 3-3: Grounded voltage-variable resistor using OTA.

Using two such arrangements cross-connected in parallel, a floating VVR can be obtained. On the other hand, if the input terminals in Fig. 3-3 are interchanged, the input resistance will be  $-1/g_m$ . Thus, using OTAs, both positive and negative resistors become available without actually having to build them on the chip. These, coupled with capacitors, lead to the creation of the so called active-*C* filters.

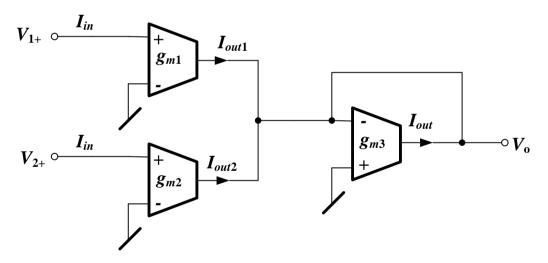

#### • Voltage summation using OTA

Voltage summation can be obtained using OTAs, which in effect translate voltages to currents. Currents are easily summed as shown in Fig. 3-4.

Fig. 3-4: Voltage summation using OTA.

It is clear that

$$I_{out1} + I_{out2} + I_{out} = 0 (3-3)$$

$$g_{m1}V_{1+} + g_{m2}V_{2+} - g_{m3}V_o = 0 ag{3-4}$$

$$V_o = \frac{g_{m1}}{g_{m3}} V_{1+} + \frac{g_{m2}}{g_{m3}} V_{2+}$$

(3-5)

If  $g_{m1} = g_{m2} = g_{m3}$

$$V_o = V_{1+} + V_{2+} \tag{3-6}$$

By changing the grounded input of one of the input OTAs, voltage subtraction can be achieved. These operations are useful for the realization of filters which should be synthesized from their transfer functions.

#### • Integrator using OTA

The operation of integration can be achieved very conveniently using the OTA as is shown in Fig. 3-5. The following equations can be written for Fig. 3-5 a) and b), respectively:

Fig. 3-5: Integrators using OTA, (a) voltage-mode, (b) current-mode.

$$V_o = \frac{I_{out}}{sC} = \frac{g_m}{sC} (V_+ - V_-)$$

$$I_{out} = \frac{g_m}{sC} I_{in}$$

(3-7)

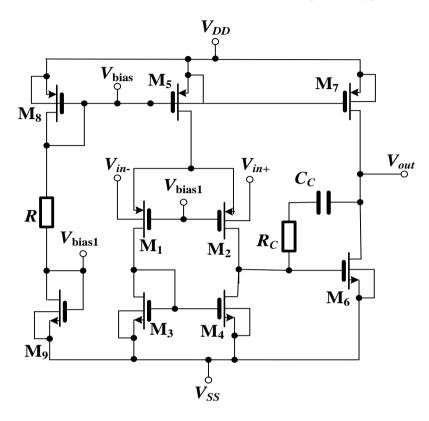

#### 3.1.2. CMOS Implementation of OTA

Bulk-driven CMOS implementation of OTA shown in Fig. 3-6 consists of two stage, the first which combined of the bulk-driven differential stage with pMOS input device  $M_1$  and  $M_2$  and the current mirror  $M_3$  and  $M_4$  acting as an active load [54]. The second stage is a simple CMOS inverter with  $M_6$  as a driver and  $M_7$  acting as an active load. Its output is connected to the output of the differential stage by means of compensation capacitance *Cc* and the resistance  $R_c$  since the compensation capacitance actually acts as a Miller capacitance in the

last stage. By setting the gate-source voltage to a value sufficient to turn on the transistor, then the operation of the bulk-driven MOS transistor becomes a depletion type.

Fig. 3-6: Two stages Bulk-driven OTA [54].

| Characteristics                                                        | Simulation Result                                   |

|------------------------------------------------------------------------|-----------------------------------------------------|

| Power consumption                                                      | 30 µW                                               |

| Open loop gain                                                         | 70 dB                                               |

| Bandwidth                                                              | 4 MHz                                               |

| Phase margin                                                           | 70°                                                 |

| DC input voltage range                                                 | -400, 700mV                                         |

| Slow rate                                                              | $SR_{LH}{=}0.8V/{\mu s}$ , $SR_{HL}{=}0.4V/{\mu s}$ |

| Measurement condition: $V_{DD} = 0.6V$ , $V_{SS} = 0.6V$ , $C_L = 1pF$ |                                                     |

#### Tab. 3.1: Simulation results of the Bulk-driven OTA.

#### 3.2. Current Conveyor of Second Generation (CCII)

One of the most basic building blocks in the area of current-mode analogue signal processing is the current conveyor (CC). The principle of the current conveyor of the first generation was published in 1968 by K. C. Smith and A. S. Sedra [5]. CCI was then replaced by a more versatile second-generation device in 1970 [6], the CCII. Current conveyor designs

have mainly been with BJTs due to their high transconductance values compared to their CMOS counterparts. They are used as current-feedback operational amplifiers like the MAX477 high-speed amplifier and the MAX4112 low-power amplifier, which both feature current feedback rather than the conventional voltage feedback used by standard operational amplifiers.

Current conveyors are used in high-frequency applications where the conventional operational amplifiers can not be used, because the conventional designs are limited by their gain-bandwidth product.

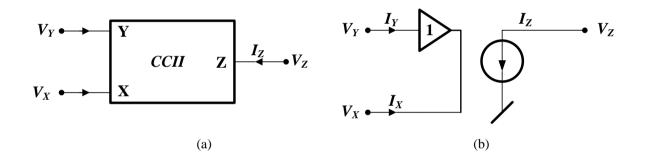

The second-generation current conveyor (CCII) is used as a basic building block in many current-mode analog circuits. It is a three-terminal (X, Y and Z) device as shown in Fig. 3-7 (a), and the equivalent circuit of the ideal CCII is shown in Fig. 3-7 (b).

Fig. 3-7: (a) The CCII symbol, (b) ideal equivalent circuit.

The characteristics of ideal CCII are represented by the following hybrid matrix

$$\begin{bmatrix} I_Y \\ V_X \\ I_Z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_Y \\ I_X \\ V_Z \end{bmatrix}$$

(3-8)

An ideal CCII has the following characteristics:

- Infinite input impedance at terminal Y ( $R_{\rm Y} = \infty$  and  $I_{\rm Y} = 0$ )

- Zero input impedance at terminal X ( $R_X = 0$ )

- Accurate voltage copy from terminal Y to X ( $V_X = V_Y$ )

- Accurate current copy from terminal X to Z with infinite output impedance at Z ( $I_Z = I_X$  and  $R_Z = \infty$ )

#### 3.2.1. Operations using the ideal CCII

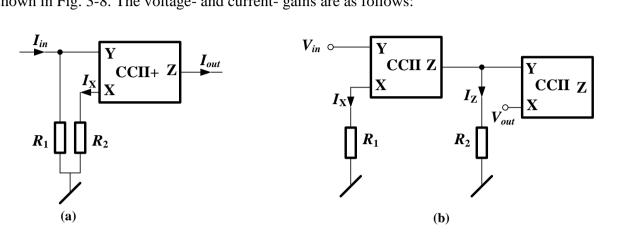

#### • Amplifiers using CCII

The CCII can easily be used to form the current output amplifiers and voltage-output amplifier as shown in Fig. 3-8. The voltage- and current- gains are as follows:

Fig. 3-8: (a) CCII-based current amplifier, (b) CCII-based voltage amplifier.

$$\frac{I_{out}}{I_{in}} = \frac{R_1}{R_2} \tag{3-9}$$

$$\frac{V_{out}}{V_{in}} = \frac{R_2}{R_1} \tag{3-10}$$

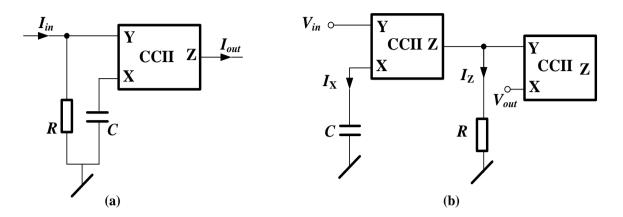

#### • Integrators using CCII

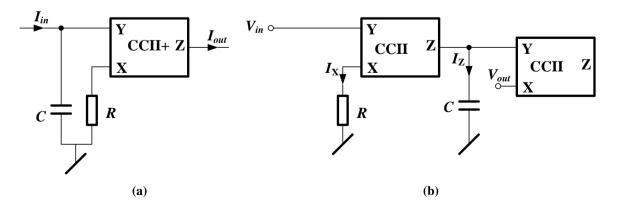

In Fig. 3-9, simple current- and voltage- integrators are presented.

Fig. 3-9: (a) CCII-based current integrator, (b) CCII-based voltage integrator.

The output signals are as follows:

$$I_{out} = \frac{I_{in}}{sCR} \tag{3-11}$$

$$V_{out} = \frac{V_{in}}{sCR} \tag{3-12}$$

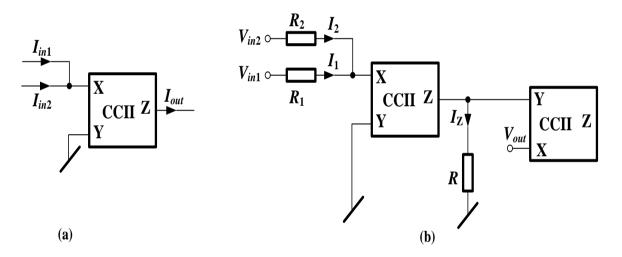

### • Adders using CCII

In Fig. 3-10, CCII-based current adder and CCII-based voltage adder are reported, with the following equations:

Fig. 3-10: (a) CCII-based current adder, (b) CCII-based voltage adder.

$$I_{out} = -(I_{in1} + I_{in2}) \tag{3-13}$$

$$V_{out} = -\frac{R}{R_1} V_{in1} - \frac{R}{R_2} V_{in2}$$

(3-14)

#### • Differentiators using CCII

Current- and voltage-mode versions are shown in Fig. 3-11. The output signals are as follows:

Fig. 3-11: (a) CCII-based current differentiator, (b) CCII-based voltage differentiator.

$$I_{out} = sCRI_{in} \tag{3-15}$$

$$V_{out} = sCRV_{in} \tag{3-16}$$

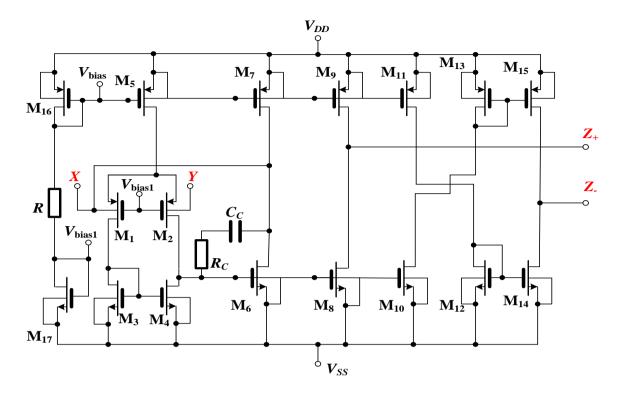

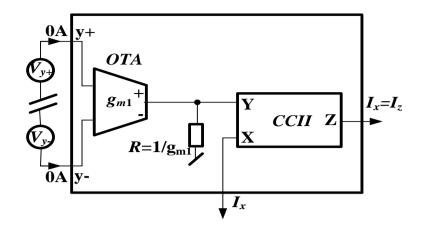

#### 3.2.2. Bulk-driven CCII± based on Bulk-driven OTA

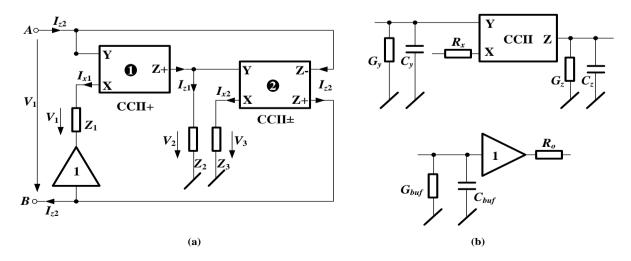

A new connection of Bulk-driven OTA is used to realize the CCII. In the OTA-based approach, presented in Fig.3-12, Bulk-driven OTA is used to implement the unity gain buffer between the Y and X inputs [54]. The X input current  $I_X$  is sensed by duplicating buffers' output transistors  $M_6$  and  $M_7$  using transistors  $M_8$  and  $M_9$ , and extracting the X current from them as  $I_Z$ . Since transistors  $M_8$  and  $M_9$  have the same size and gate-source voltage as the output stage transistors  $M_6$  and  $M_7$ , the current  $I_Z$  should be a copy of the current flowing through  $M_6$  and  $M_7$  which is  $I_X$ . Transistors  $M_{10}$ - $M_{15}$  are used to generate  $I_Z$ . Since no additional transistors need to be inserted between the OTA and rails, the approach will not increase the minimum operating voltage over that of the operational core. In addition the voltage follower is based on an OTA, thus it will maintain all the benefits and also the disadvantages of such a circuit i.e. a good voltage follower at the cost of lower bandwidth.

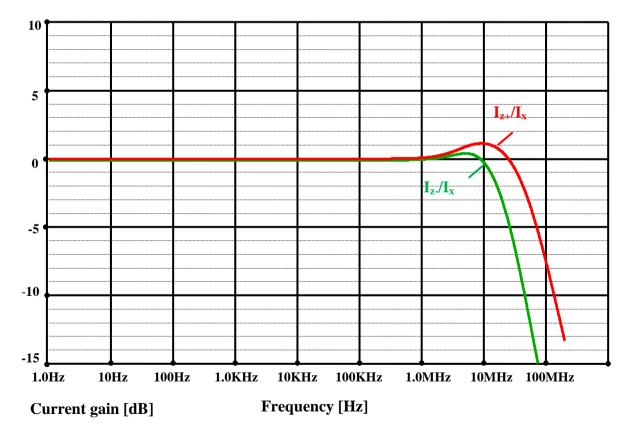

The simulated frequency responses of current gains  $I_{z+}/I_x$ ,  $I_{z-}/I_x$  are given in Fig. 3-13. The cutoff frequencies for the gains are 20 MHz and 52 MHz, respectively.

Fig. 3-12: Bulk-driven CCII± based on Bulk-driven OTA.

Fig. 3-13: Frequency variation of the current gains IZ+/IX, IZ-/IX in Db of the CCII in Fig. 3-12.

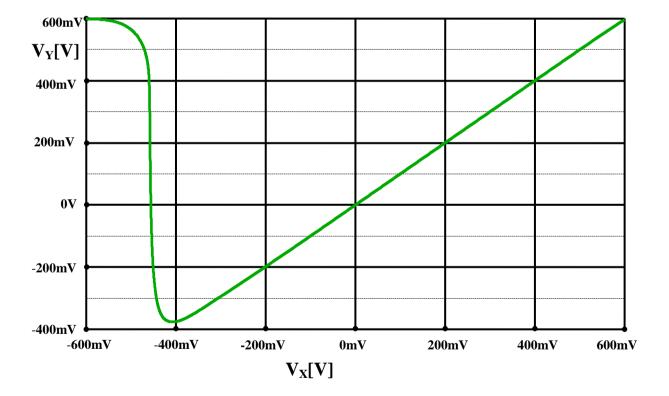

In Fig. 3-14, the input voltage buffer behavior is shown. A DC sweep simulation has been performed, to check the range in which the voltage on X node is equal to the voltage applied to Y node.

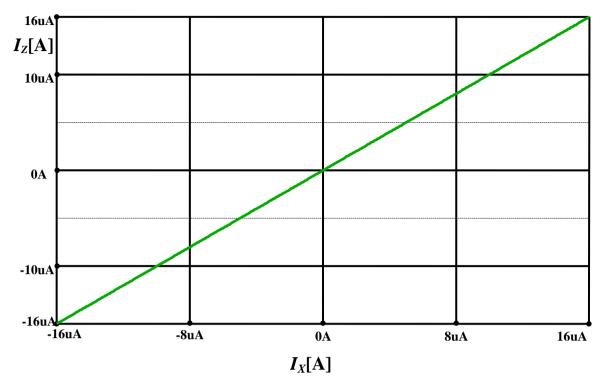

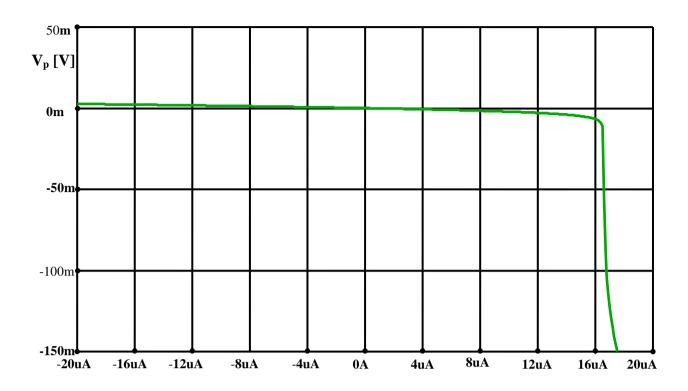

The current linearity between X and Y terminal of the bulk-driven current conveyor (CCII±) from Fig. 3-12, is demonstrated in Fig. 3-15. Note that for input currents  $I_x$  and  $I_z$ , the boundary of linear operation is ca ±16µA.

The corresponding small-signal current gains are as follows:  $I_{z+}/I_X$ ,  $I_z/I_X = 1$ , and the corresponding voltage gain  $V_X/V_Y = 0.97$ .

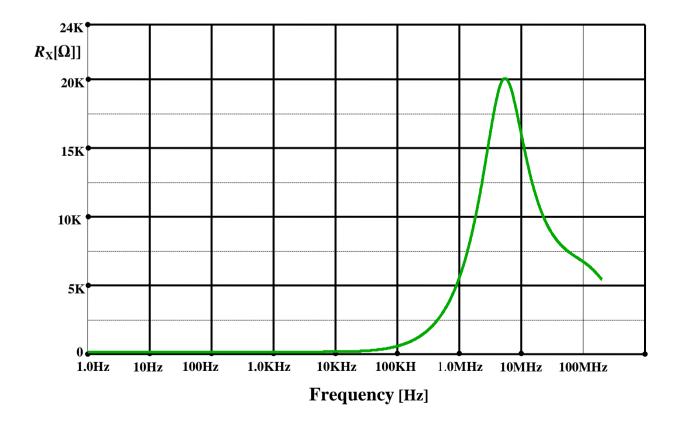

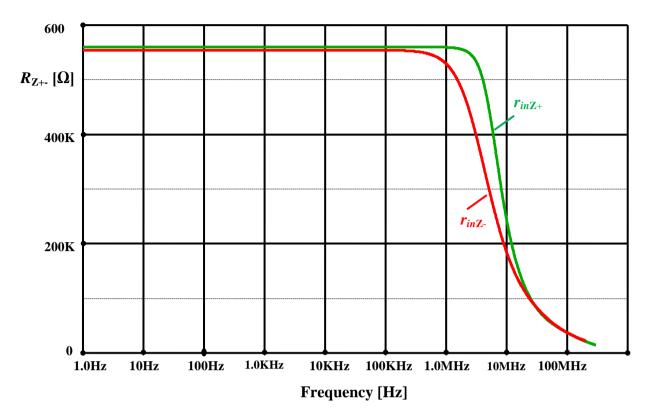

The small-signal low frequency resistance of the X terminal  $R_x$  is equal to 166  $\Omega$  as shown in Fig. 3-16. The small-signal resistance of the Y terminal  $R_Y$  is equal to 50G $\Omega$ . The smalllow frequency signal resistances of the Z+, Z- outputs terminals are equal to 560k $\Omega$ , and 554k $\Omega$ , respectively. Simulation results of the CCII± are summarized in Table 3-2.

Fig. 3-14: Voltage follower between X and Y of the CCII in Fig. 3-12.

Fig. 3-15: Current linearity between X and Y of the CCII in Fig. 3-12.

Fig. 3-16: The X node input resistance rin, x of the CCII in Fig. 3-12.

Fig. 3-17: The Z node output resistance rin,Z of the CCII in Fig. 3-12.

| Characteristics                                           | Simulation Result |

|-----------------------------------------------------------|-------------------|

| Power consumption                                         | 119 μW            |

| 3-dB bandwidth $I_{Z+}/I_X$                               | 20 MHz            |

| 3-dB bandwidth $I_{Z}/I_{X}$                              | 52 MHz            |

| DC voltage range                                          | -400, 600 mV      |

| DC current range                                          | ±16 µA            |

| Current gain $I_Z/I_X$                                    | 1                 |

| Voltage gain $V_X/V_Y$                                    | 0.97              |

| Node X parasitic DC resistance                            | 166 Ω             |

| Node Y parasitic DC resistance                            | 50 GΩ             |

| Node Z+ parasitic DC resistance                           | 560 kΩ            |

| Node Z- parasitic DC resistance                           | 554 kΩ            |

| Measurement condition: $V_{DD} = 0.6V$ , $V_{SS} = -0.6V$ |                   |

Tab. 3-2: Simulation results of the Bulk-driven CCII.

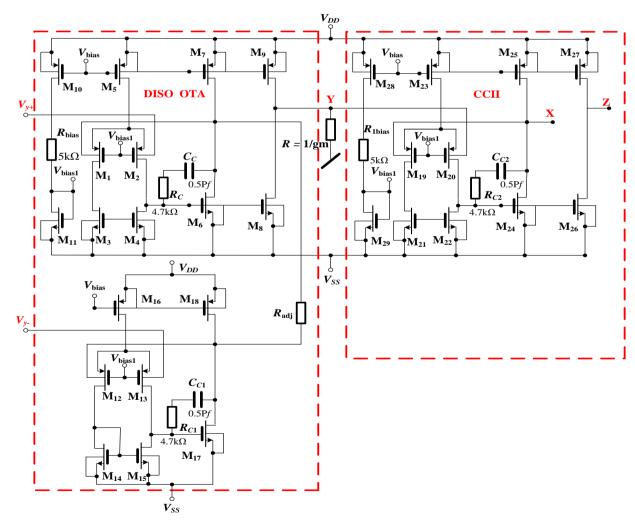

#### 3.2.3. Bulk-driven OTA with gm adjustable via external R

In this part, a new concept of high-linearity OTA with controllable transconductance is proposed. The OTA is simulated in a standard TSMC 0.18 mm CMOS process with a 0.6 V supply voltage.

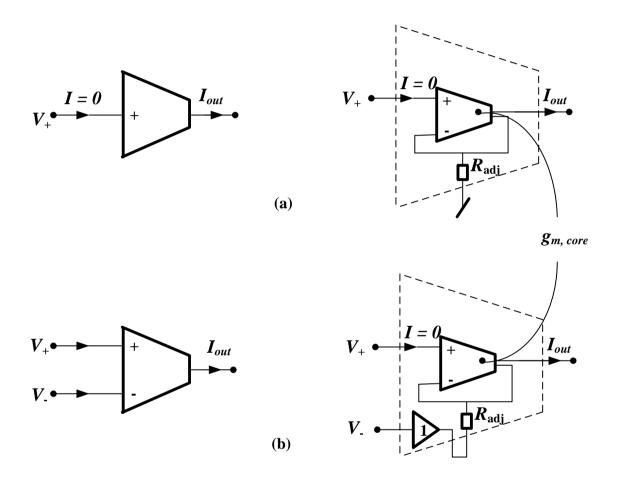

The principle of  $g_m$  adjustable via a feedback resistor  $R_{adj}$  is show in Fig. 3-18.

Fig. 3-18: (a) SISO OTA with gm adjustable, (b) DISO OTA with gm adjustable.

In this part, a high linearity, wideband OTA with tunable transconductance is presented according to Eq. (3-18). The adjustable transconductance  $g_{m, adjust}$  depends on  $R_{adj}$  as follows:

$$g_{m,adjust} = \frac{g_{m,core}}{1 + g_{m,core} R_{adj}}$$

(3-17)

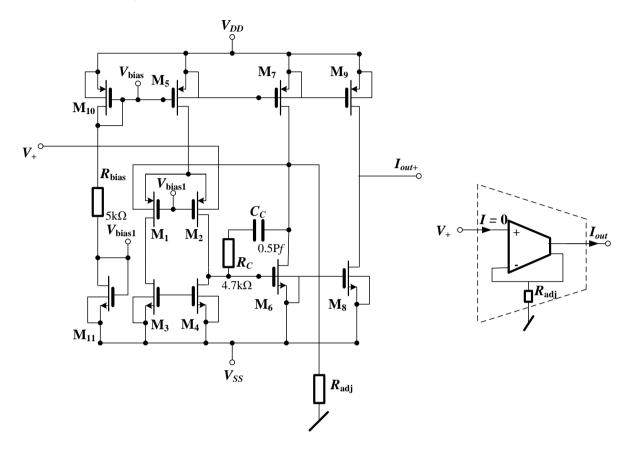

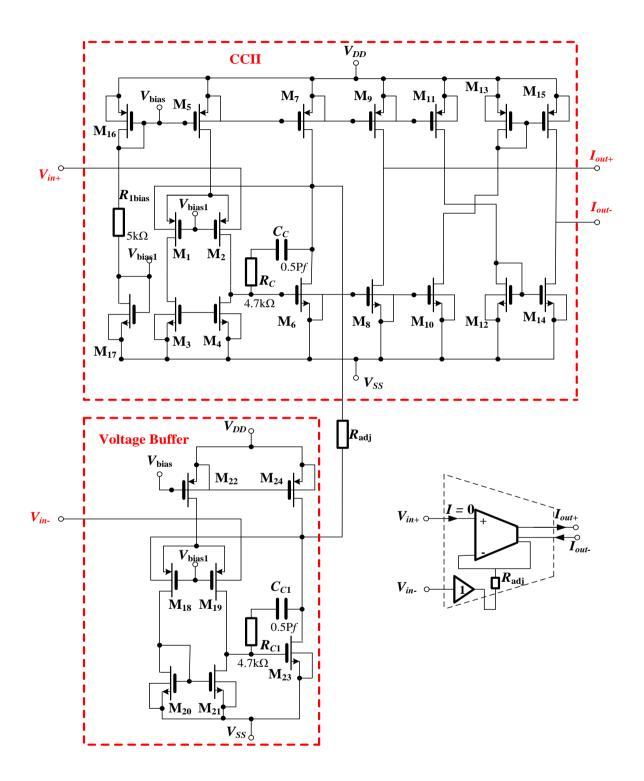

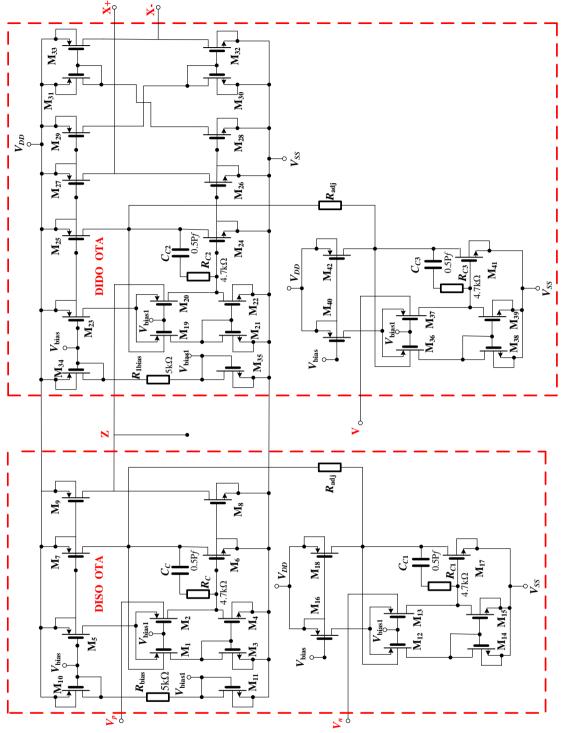

Figs. 3-19, and 3-20 show circuit implementations of Fig.3.18, namely bulk-driven single input single output OTA (SISO) and a fully differential OTA (DIDO) based on voltage buffer and Current Conveyor of Second Generation CCII.

Fig. 3-19: Bulk-driven single input single output OTA (SISO) based on CCII.

The aspect ratios of each of the transistors used the CCII and voltage buffer in Fig. 3-20 are listed in Tables 3-3 and 3-4, respectively.

Fig. 3-20: Bulk-driven fully differential OTA (DIDO) based on CCII and voltage buffer.

| Transistor                         | Length (µm) | Width (µm) |

|------------------------------------|-------------|------------|

| $M_1, M_2$                         | 2           | 30         |

| $M_3, M_4$                         | 2           | 4          |

| M <sub>5</sub> , M <sub>16</sub>   | 3           | 20         |

| $M_6, M_8, M_{10}, M_{12}, M_{14}$ | 2           | 16         |

| $M_7, M_9, M_{11}, M_{13}, M_{15}$ | 3           | 40         |

| M <sub>17</sub>                    | 3           | 10         |

Tab. 3-3: Aspect ratios of the transistors used in the CCII in Fig. 3-20.

| Transistor       | Length (µm) | Width (µm) |

|------------------|-------------|------------|

| $M_{18}, M_{19}$ | 2           | 30         |

| $M_{20}, M_{21}$ | 2           | 4          |

| M <sub>22</sub>  | 3           | 20         |

| M <sub>23</sub>  | 2           | 16         |

| M <sub>24</sub>  | 3           | 40         |

Tab: 3-4: Aspect ratios of the transistors used in the Voltage buffer in Fig. 3-20.

The performance of the proposed OTA in Fig. 3-20 was verified via PSPICE simulation. All the balanced CMOS OTA was simulated by using CMOS structure and MIETEC 0.18µm. The dimensions of transistors were used from Tables. 3-3 and 3-4 and the power supply voltages were set  $V_{DD} = -V_{SS} = \pm 0.6$ V.

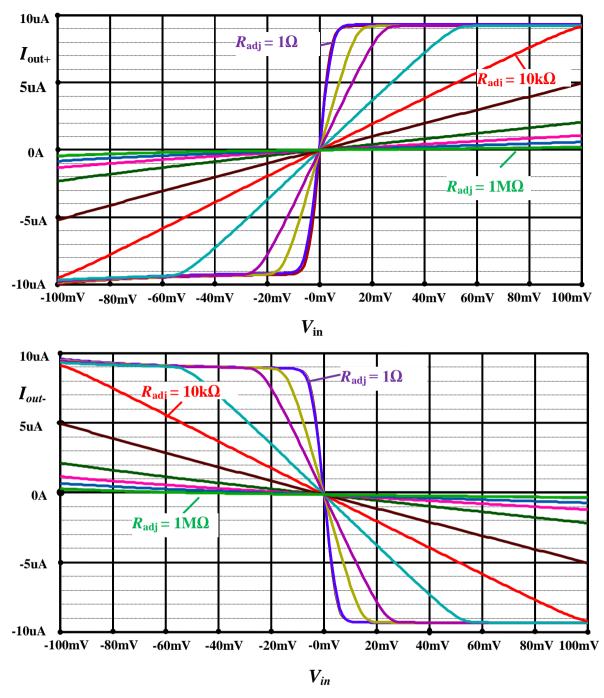

Fig. 3-21 shows the simulated transfer characteristics of the OTA in Fig. 3-20. The plots of the output current  $I_{out}$  versus the input voltage  $V_{in}$  show that, for  $R_{adj}$  values of 1 $\Omega$ , 10 $\Omega$ , 100 $\Omega$ , 1k $\Omega$ . 2k $\Omega$ , 5k $\Omega$ , 10k $\Omega$ , 20k $\Omega$ , 50k $\Omega$ , 100k $\Omega$ , 200k $\Omega$ , 500k $\Omega$ , and 1M $\Omega$ , the  $g_m$  is controlled accordingly.

Fig. 3-21: DC transfer characteristics of bulk-driven fully differential OTA.

It is shown that the transconductance gain  $g_m$  can be linearly tuned when  $R_{adj}$  is increased. But for  $R_{adj}$  bigger than 50k $\Omega$  it causes distortion. The linear range is very good for  $R_{adj}$  of about 10k $\Omega$ .

The AC analysis of the bulk-driven OTA in Fig. 3.20 is shown in Fig. 3-22. The frequency dependence of  $I_{out}$  is measured by fixing AC value of  $V_{in}$  at 1V.

The responses are plotted for  $R_{adj}$  of 1 $\Omega$ , 10 $\Omega$ , 10 $\Omega$ , 1k $\Omega$ , 2k $\Omega$ , 5k $\Omega$ , 10k $\Omega$ , 20k $\Omega$ , 50k $\Omega$ , 100k $\Omega$ , 200k $\Omega$ , 500k $\Omega$ , and 1M $\Omega$ . The corresponding values of  $g_m$  are shown in Table. 3-5

Fig. 3-22: AC transfer characteristics of bulk-driven fully differential OTA.

| R <sub>adj</sub> | g <sub>m</sub> |

|------------------|----------------|

| 1Ω               | 2.2 ms         |

| 10Ω              | 2.16 ms        |

| 100Ω             | 1.8 ms         |

| 1kΩ              | 688.7 μs       |

| 2kΩ              | 408.5 μs       |

| 50 kΩ            | 184.45 μs      |

| 100 kΩ           | 96.82 μs       |

| 200 kΩ           | 50.1 μs        |

| 500 kΩ           | 21.04 µs       |

| 1 MΩ             | 11.2 μs        |

Tab: 3-5: Variations of  $g_m$  by  $R_{adj}$ .

# 3.3. Current Differencing Transconductance Amplifier (CDTA)

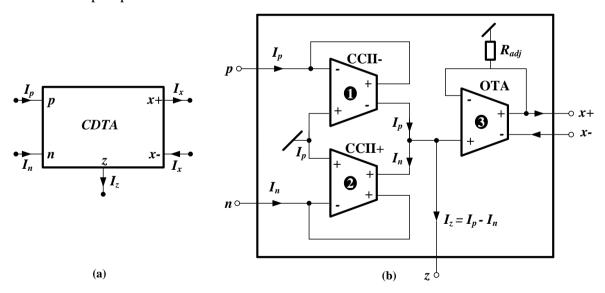

The CDTA element [55] with its schematic symbol in Fig. 3-23 (a) has a pair of lowimpedance current inputs p and n, and an auxiliary terminal z, whose outgoing current is the difference of input currents. Also in Fig. 3-23 (b) is given a possible implementation of CDTA using the OTA components. Here, output terminal currents are equal in magnitude, but flow in opposite directions, and the product of transconductance  $g_m$  and the voltage at the z terminal gives their magnitudes. Therefore, this active element can be characterized with the following equations:

$$V_P = V_n = 0,$$

$I_Z = I_P - I_n$  (3-18)

$$I_{x+} = g_m V_Z, \qquad I_{x-} = -g_m V_Z$$

(3-19)

Where  $V_z = I_z Z_z$  and  $Z_z$  is the external impedance connected to Z terminal of the CDTA. CDTA can be thought as a combination of a current differencing unit [13] followed by a dualoutput operational transconductance amplifier, DO-OTA. Ideally, the OTA is assumed as an ideal voltage-controlled current source and can be described by  $I_x = g_m(V_+ - V_-)$ , where  $I_x$  is output current,  $V_+$  and  $V_-$  denote non-inverting and inverting input voltage of the OTA, respectively.

CDTA applications do not require the use of external resistors, which are substituted by internal transconductors. Analogously to the well-known " $g_mC$ " applications, the "CDTA-C" circuits are formed by CDTA elements and grounded capacitors. Such structures are well-suited for on-chip implementation.

Fig. 3-23: (a) Symbol of the CDTA, (b) its implementation by bulk-driven OTAs.

Marking the voltages of p, n, x, and z terminals in Fig. 3-23 (a) with symbols  $V_p$ ,  $V_n$ ,  $V_x$ , and  $V_z$ , then for the CDTA+- element the following equations are true:

## 3.3.1. Operations using the ideal CDTA

## • Integrator using CDTA

The operation of integration can be achieved very conveniently using the CDTA as shown in Fig. 3-24. Clearly [56],

$$K_{i} = \frac{I_{x}}{I_{p}} = \frac{g_{m}}{sC}$$

$$(3-21)$$

$$I_{p}$$

$$CDTA$$

$$I_{x}$$

Fig. 3-24: Integrator using CDTA.

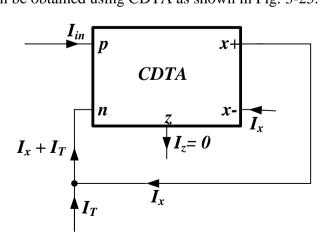

### • Current Summation using CDTA

Current summation can be obtained using CDTA as shown in Fig. 3-25.

Fig. 3-25: Current summation using CDTA.

We let z node outlet open, thus

$$I_{z} = I_{p} - I_{n}, \quad I_{z} = 0$$

(3-22)

$$I_{p} = I_{n}, \quad I_{n} = I_{x} + I_{T}$$

$$I_{in} = I_{x} + I_{T}$$

$$I_{x} = I_{in} - I_{T}$$

(3-23)

## 3.3.2. CMOS Implementation of CDTA

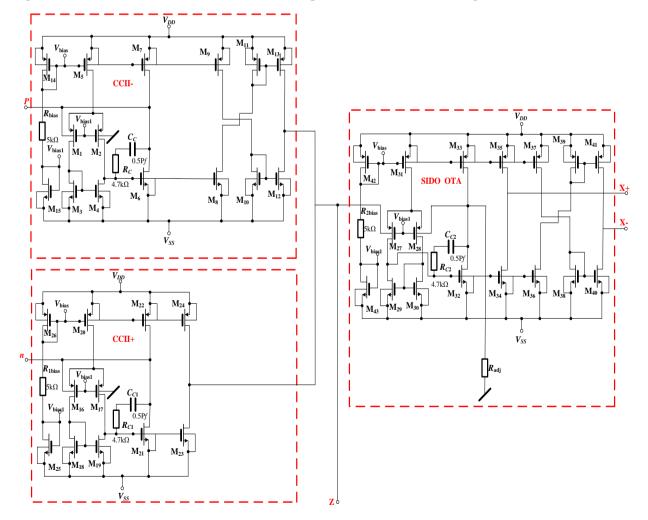

Fig. 3-26 shows CMOS bulk-driven CDTA implementation based on Fig. 3-23 (b).

Fig. 3-26: CMOS implementation of CDTA.

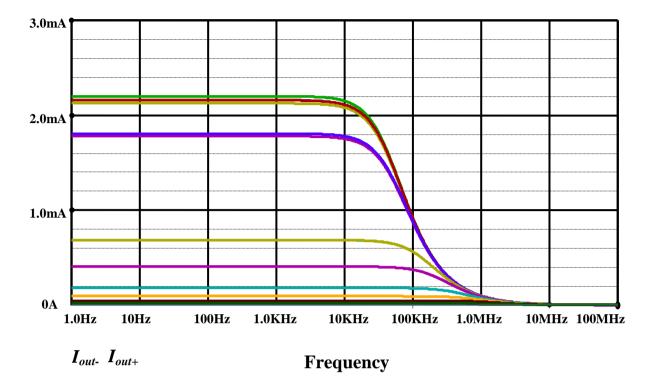

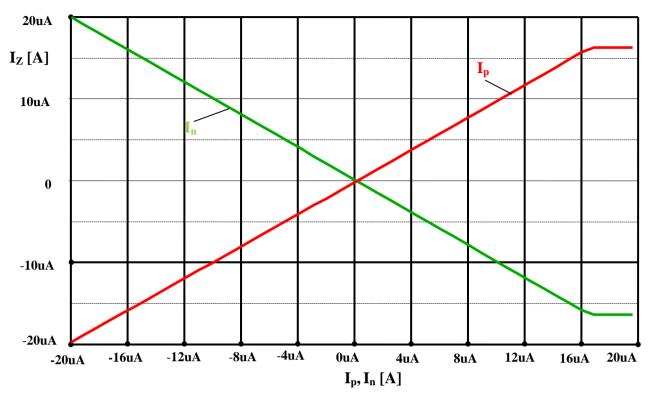

The simulation results for the CDTA according to Fig. 3-26 are given in Figs. 3-27 to 3-32, and its small-signal parameters are summarized in Table 4-6.

Fig. 3-27 shows the  $I_z/I_p$  and  $I_z/I_n$  curves of the Current Differencing Unit (CDU), simulated on the assumption of  $V_z = 0$ . Note that for positive input currents  $I_p$  and  $I_n$ , the boundary of linear operation is ca 16µA. The current offset  $\Delta I_z$  is ca -141 nA. For the bias point  $I_p = I_n = 0$ , the corresponding small-signal current gains are as follows:  $\alpha_p = I_z/I_p = 0.986$ ,  $\alpha_n = I_z/I_n = 1$ .

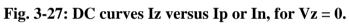

The frequency responses of current gains  $I_z/I_p$ ,  $I_z/I_n$  are given in Fig. 3-28. The cutoff frequencies for the gains  $\alpha_p$  and  $\alpha_n$  are 22 MHz and 75 MHz, respectively.

The voltage-current characteristic of the *p*-terminal input gate of the CDTA is shown in Fig. 3-29. Identical results also hold for the *n*-terminal. Note that when the input current approaches a value of ca 17  $\mu$ A, the clipping property of this curve can cause a significant nonlinear distortion. However, the range of linear operation is suitable for many applications that need extra low power consumption.

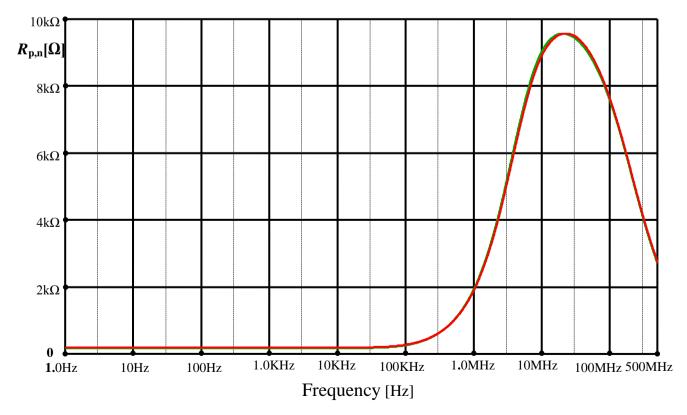

For the DC bias  $I_p = 0$ , the small-signal resistances  $R_p$  and  $R_n$  are 166  $\Omega$ . The frequency dependences of the impedances of *p*- and *n*- terminals in Fig. 3-30 show that the above values are kept up to ca one hundred kilohertz. Then the impedances increase due to the frequency dependence of the OTA transconductances.

Fig. 3-28: Frequency responses of current gains Iz/Ip and Iz/In for Vz = 0.

Fig. 3-29: DC curve Vp versus Ip for evaluating small-signal input resistance of the pterminal. For the n-terminal, the result is identical.

Fig. 3-30: Frequency dependence of the impedances of p- and n- terminals.

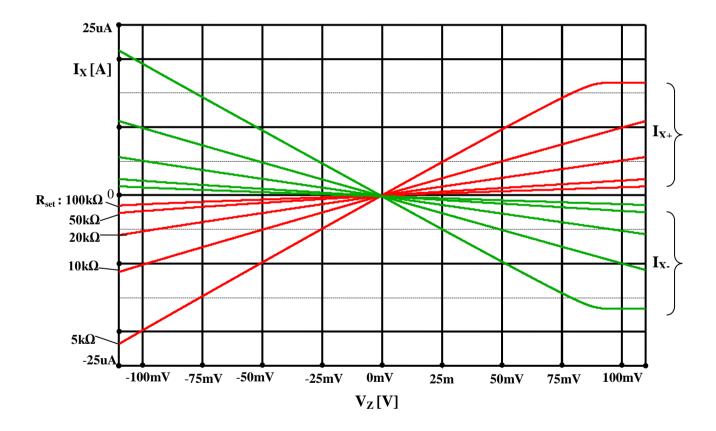

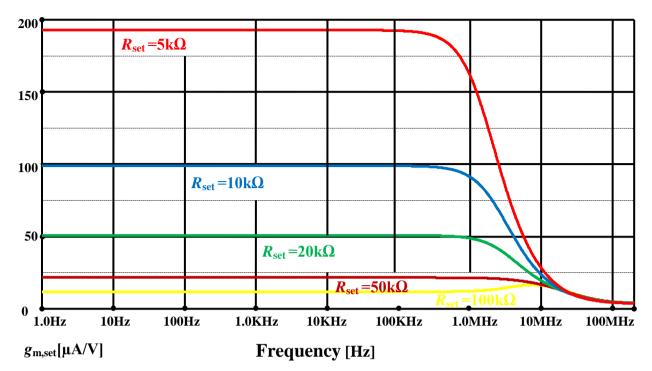

The  $I_x$  versus  $V_z$  curves in Fig. 3-31 are analyzed for several values of the external resistance  $R_{set}$ . They clearly show the transconductance control via  $R_{set}$  as well as the effect of the linearization and increasing the dynamic range with increasing values of  $R_{set}$ . A detailed analysis also confirms that the current offset is decreasing with increasing value of  $R_{set}$ . For  $R_{set} = 10 \text{ k}\Omega$ , the offset current is only -141 nA. Fig. 3-32 shows the frequency dependences of  $g_{m,set}$  and of the x- and z-terminal impedances. The transconductance bandwidth increases with increasing  $R_{set}$ . For example,  $R_{set} = 10 \text{ k}\Omega$  yields  $g_{m,set} \approx 99 \text{ }\mu\text{A/V}$  and the -3dB cutoff frequency is approximately 1.1 MHz. The frequency dependence of the z-terminal impedance shows the value 277 k $\Omega$ , with a -3dB cutoff frequency of about 2 MHz. The low-frequency x-terminal resistance is ca 554 k $\Omega$ . Simulation results of the CDTA are summarized in Table 3-6.

Fig. 3-31: DC characteristics of OTA No. 3 with Rset linearization and transconductance control.

Fig. 3-32: Frequency responses of transconductances.

| Characteristics                                          | Simulation Result                                               |  |

|----------------------------------------------------------|-----------------------------------------------------------------|--|

| Power consumption                                        | 264 μW                                                          |  |

| 3dB bandwidth $I_Z/I_p$ , $I_Z/I_n$                      | 22 MHz, 75MHz                                                   |  |

| DC current range $I_p$ , $I_n$                           | ±16 µA                                                          |  |

| DC voltage range $V_Z(R_{set} = 10k\Omega)$              | +170 mV, -310 mV                                                |  |

| DC offset of OTA stage ( $R_{set} = 10k\Omega$ )         | -141 nA                                                         |  |

| Current gains $I_Z/I_p$ , $I_Z/I_n$                      | 0.986, 1                                                        |  |

| $g_m (R_{\rm set} = 10 {\rm k}\Omega)$                   | 98.9 μA/V                                                       |  |

| 3dB bandwidth $g_m (R_{set} = 10 k\Omega)$               | 3dB bandwidth $g_m (R_{set} = 10 k\Omega)$ 1.2 MHz              |  |

| Node <i>n</i> and <i>p</i> parasitic DC resistance       | Node <i>n</i> and <i>p</i> parasitic DC resistance $166 \Omega$ |  |

| Node <i>z</i> parasitic DC resistance                    | 277 kΩ                                                          |  |

| Node x parasitic DC resistance $554 \text{ k}\Omega$     |                                                                 |  |

| Measurement condition: $V_{DD} = 0.6V$ , $V_{SS} = 0.6V$ |                                                                 |  |

## Tab. 3-6: Simulation results of the Bulk-driven CDTA.

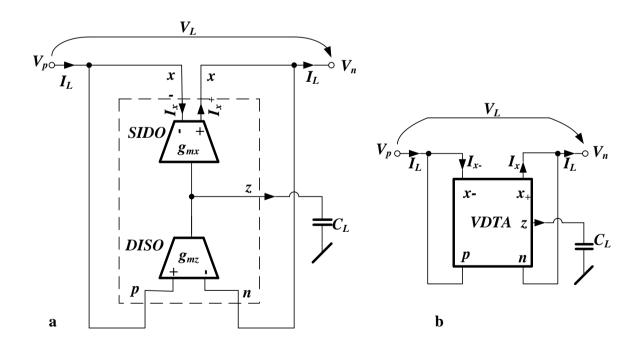

## 3.4. Voltage Differencing Transconductance Amplifier (VDTA)

The methodology described in the CDTA, which uses the CDU as the input unit, and the following simple block OTA represents an open system: Let us continue with the variation that the input unit will now implement voltage and not current differences. The differential-input OTA is a simple element for realizing the voltage difference. Simultaneously, it can

provide the possibility of electronic control. The VDTA element [23] with its schematic symbol in Fig. 3-33 (a) has a pair of high-impedance current inputs p and n, and an auxiliary terminal z. A multiple copies of  $I_z$  current are indicated here in order to increase the universality of VDTA element. Thus, according to the proposed methodology, the VDTA element should have the "zc"(Z Copy) attribute. Also a possible implementation of VDTA using two OTA components is given in Fig. 3-33 (b). Here, output terminal currents are equal in magnitude, but flow in opposite directions, and the product of transconductance ( $g_m$ ) and the voltage at the z terminal gives their magnitudes. Therefore, this active element can be characterized with the following equations:

$$I_P = I_n = 0,$$

$I_Z = g_{mZ} (V_p - V_n)$  (3-24)

$$I_{zc} = \pm I_z \tag{3-25}$$

$$I_{x+} = g_{mx}V_Z, \qquad I_{x-} = -g_{mx}V_Z$$

(3-26)

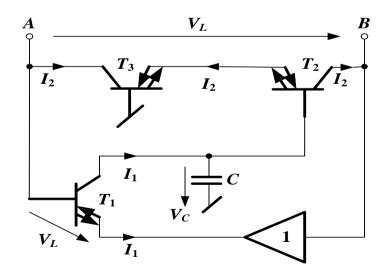

VDTA has an interesting application potential: for example, the floating loss-less inductor can be simulated only by one VDTA and one grounded capacitor.

Fig. 3-33: (a) Symbol of the VDTA, (b) its implementation by OTAs.

### 3.4.1. Operations using the ideal VDTA

### • Integrator using VDTA

The operation of integration can be achieved very conveniently using the VDTA as is shown in Fig. 3-34. Clearly,

$$V_{p} \circ I_{p} = 0$$

$$V_{p} \circ I_{n} = 0$$

$$P$$

$$VDTA$$

$$I_{x} \circ I_{n} = 0$$

$$R$$

$$Z$$

$$I_{z} = g_{mz}(V_{p} - V_{n})$$

Fig. 3-34: Integrator using VDTA.

$$I_{z} = g_{mz} (V_{p} - V_{n})$$

$$V_{z} = \frac{I_{z}}{sC} = \frac{g_{mz} (V_{p} - V_{n})}{sC}$$

$$I_{x} = g_{mx} V_{z} = \frac{g_{mx} g_{mz} (V_{p} - V_{n})}{sC}$$

$$\frac{I_{x}}{(V_{p} - V_{n})} = \frac{g_{mx} g_{mz}}{sC}$$

(3-27)

$$(3-27)$$

### • Current Summation using VDTA

Current summation can be obtained using VDTA as shown in Fig. 3-35.

Fig. 3-35: Current summation using VDTA.

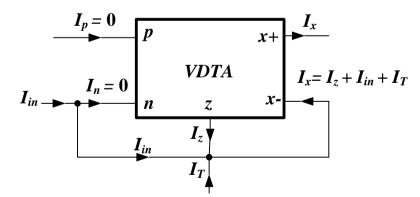

### 3.4.2. CMOS Implementation of VDTA

For low-voltage low-power applications, is can be advantageous to implement the VDTA element in Fig. 3-33 (b) with the utilization of bulk-driven [82] CMOS technique. One possibility is presented in Fig. 3-36.

VDTA is built here by means of two OTAs of DISO (Differential Input Single Output) and SIDO (Single Input Differential Output) types. This circuit uses low supply voltages, namely  $\pm 0.6$  V. The total power dissipation is less than 206µW.

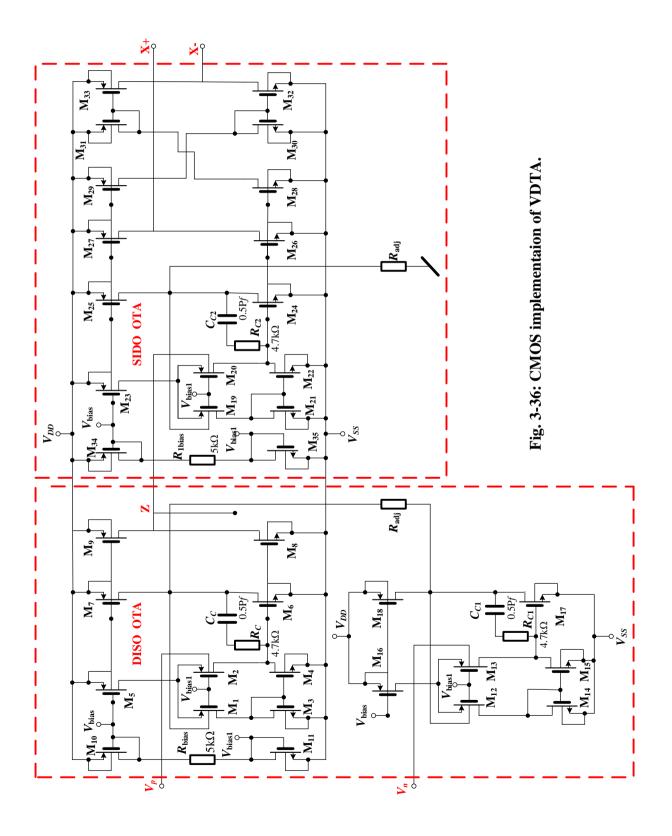

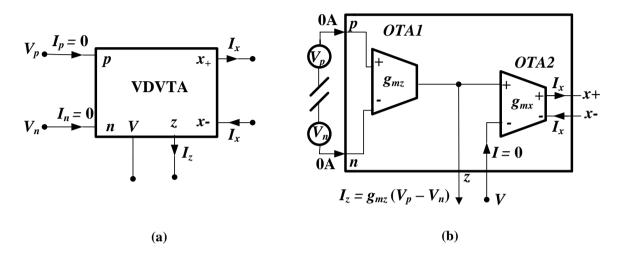

## 3.5. Voltage Differencing Voltage Transconductance Amplifier (VDVTA)

The VDVTA element [23] with its schematic symbol in Fig. 3-37 (a), and in Fig. 3-37 (b) is given with a possible implementation using two OTA components (Differential Input Single Output DISO and Differential Input Differential Output DIDO).

Fig. 3-37: (a) Symbol of the VDVTA, (b) its implementation by OTA.

For low-voltage low-power applications, is can be advantageous to implement the above element with the utilization of bulk-driven [82] CMOS technique.

Fig. 3-38 shows CMOS bulk-driven implementation of Fig. 3-37 (b) utilizing DISO (Differential Input Single Output) and DIDO (Differential Input Differential Output) OTA implementations. This circuit uses low supply voltages, namely  $\pm$  0.6 V. The total power dissipation is less than 206µW.

# **3.6. Differential Voltage Current Conveyor (DVCC)**

Since its first introduction by A. Sedra and K. Smith in 1970 [6], the second-generation current conveyor (CCII) has proved to be a versatile analog building block that can be used to implement numerous high frequency analog signal applications, like filters and current-mode oscillators. However, when it comes to applications demanding differential or floating inputs

like impedance converter circuits and current mode instrumentation amplifiers, which also require two high input impedance terminals, a single CCII block is no more sufficient.

In addition, most of these applications employ floating elements in order to minimize the number of used CCII blocks. For this reason and in order to provide two high input impedance terminals, two active building blocks, namely, the differential voltage current conveyor (DVCC) and the differential difference current conveyor (DDCC) have been proposed in the late 90s.

The DVCC is a five-port building block which is defined by the following matrix equation:

A symbol of DVCCII building block and its implementation by Diamond Transistors (DT) are shown in Fig. 3-39 [1].

Fig. 3-39: (a) DVCCII+ model, (b) DVCII+ using diamond transistors and buffer.

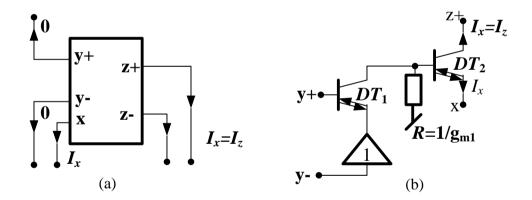

Note that DT can be simply applied as SISO (Single-Input Single-Output) OTA. DISO (Differential Input Single Output) OTA implementation requires an additional voltage buffer in order to provide high-impedance inverting input. The implementation of DVCCII by DISO (Differential Input Single Output) OTA and Current Conveyor second generation CCII is shown in Fig. 3-40.

Fig. 3-40: Implementation of DVCII+ by current conveyor and by OTA.

Fig. 3-41 shows CMOS bulk-driven implementation of circuit idea in Fig. 3-40 utilizing DISO (Differential Input Single Output) OTA CCII.

Fig. 3-41: CMOS Implementation of DVCII+ by Bulk-driven current conveyor and by OTA.

# 4. LC ladder simulation and other applications of active elements

## 4.1. Optimization of ladder filters with GmC simulation of floating inductors

Replacement of conventional inductors by synthetic ones in passive LC ladder filters belongs to well-known methods of high-order low-sensitivity filter design. An efficient way of simulating the floating inductor consists in replacing the inductor by three OTAs (Operational Transconductance Amplifier) and one grounded capacitor [51]. However, the common drawback of OTAs is the low-level input voltage providing the linear mode of the amplifier.

This can be in conflict with the requirements for a large dynamic range of signals being processed. When the filter is designed for the current-mode, the current limitations of the active elements should also be carefully monitored.

MAX435 is a commercial OTA [57], which appears to be an optimal circuit element for such designs. Its differential input and output can be utilized for the simplification of the well known circuitry for simulating the floating inductor [51]. The transconductance of MAX435 is adjusted by an external two-terminal device. In the case of linear resistor, OTA has an extremely linear I&V characteristic. The limitations of the output current can be precisely set by another external resistor.

Using the concrete example of 5th-order video filter, a method for designing and optimizing such a circuit is described in this paper. The commercial MAX435 is used in the subcircuits of synthetic inductances. The procedure described can be applied to an arbitrary type of OTA.

#### 4.1.1. MAX435 – a commercial OTA

MAX435 is an OTA with 275MHz bandwidth and 850V/us slew rate. Its recommended symmetrical power supply is +-5V. The transconductance  $g_m$  is set within a wide range by means of auxiliary  $R_t$  resistor [57]. The recommended maximum current through  $R_t$  as well as the output current are 10mA. A concrete saturation level  $I_{max}$  can be adjusted by  $R_{set}$  resistance approximately from 3mA up.  $R_{set} = 5.9$ k $\Omega \square$  corresponds to a current of 10mA. The maximum recommended differential voltage is 2.5V.

## 4.1.2. Synthetic inductor based on MAX435

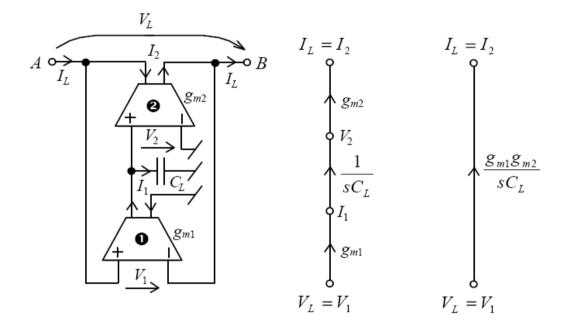

Fig. 4-1 shows a synthetic floating inductor which employs a pair of differential-input differential-output OTAs. It is a generalization of the circuit from [51], where three single-

output OTAs are used for inductor replacement. The signal flow graphs attached describe the process of transforming voltage  $V_1$  into current  $I_1$  of OTA No. 1, transforming current  $I_1$  into voltage across the capacitor, and transforming capacitor voltage into current  $I_2$ .

It follows from the last graph that the circuit implements a lossless floating inductor with the inductance

$$L = \frac{C_L}{g_{m1}g_{m2}} \tag{4-1}$$

Fig. 4-1: Synthetic inductor and the corresponding signal flow graphs.

There are two degrees of freedom when designing the transconductance  $g_{m1}$  and  $g_{m2}$  and the capacitance  $C_L$  from the desired inductance value. They can be used for dynamic range optimization. The following rule results from 4-1:

The inductor is preliminarily designed with the parameters  $g_{m1}$ ,  $g_{m2}$ , and  $C_L$ . These parameters will be modified according to the rule

$$C'_L = a_0 C_L, \qquad g'_{m1} = a_1 g_{m1}, \qquad g'_{m2} = a_2 g_{m2}$$

(4-2)

Where  $a_0$ ,  $a_1$ , and  $a_2$  are real positive numbers, fulfilling the equality

$$a_0 = a_1 a_2 \tag{4-3}$$

Then the resulting inductance is not changed due to this modification. However, current  $I_1$  will be  $a_1$  times greater and voltage  $V_2$  will be  $a_1/a_0$  times greater than before the modification of the parameters.

This rule will be used for the dynamic range optimization of target application, i.e. the active filter which simulates the LC ladder.

The following equality also results from the graph in Fig. 4-1:

$$\frac{V_2}{V_1} = \frac{g_{m1}I_2}{g_{m2}I_1} \tag{4-4}$$

The purpose of optimizing the upper limit of the dynamic range is to equalize the voltage and current levels inside the synthetic inductors, thus  $V_1 = V_2$  and  $I_1 = I_2$ . Eq. 5-1 shows that a complete equalization is enabled only when both transconductances are equal.

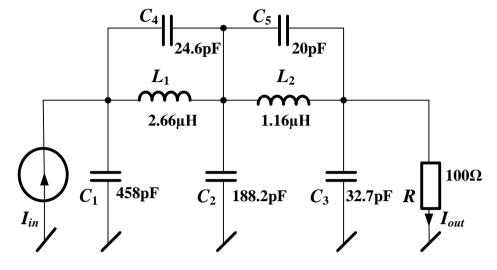

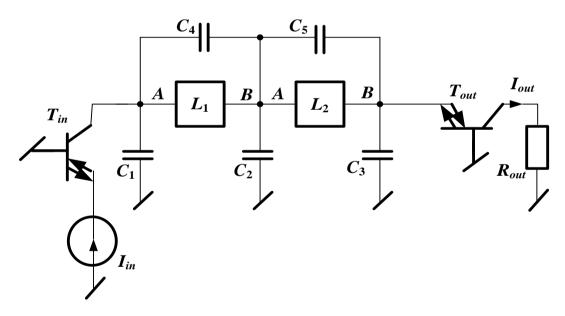

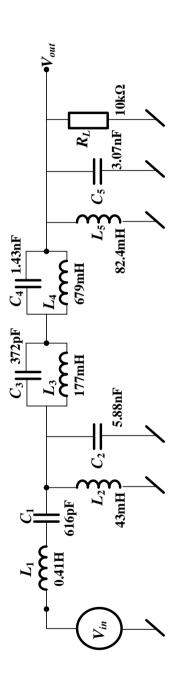

### 4.1.3. LC Ladder simulation

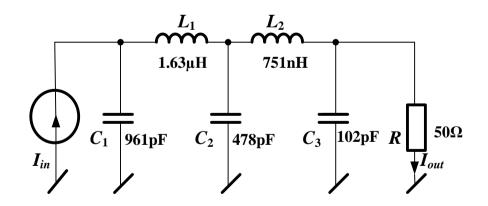

Fig. 4-2 shows the schematic of a low-pass LC ladder filter which has been designed according to Bessel approximation on the basis of the following specifications:

DC gain 0dB, 3-dB cutoff frequency 5MHz, attenuation at least 50dB for frequencies above 27MHz, maximally flat group delay. This specification is derived from the parameters of commercial video filter FMS6400-1 by Fairchild Semiconductor [58].

Fig. 4-2: 5MHz low-pass ladder filter.

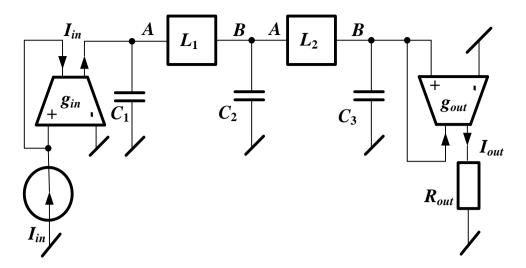

Fig. 4-3: Active ladder simulation by means of synthetic inductors and OTAs.

An active realization of the LC ladder is shown in Fig. 4-3. Blocks " $L_1$ " and " $L_2$ " are the synthetic inductors from Fig. 4-1. OTA with transconductance  $g_{in}$  serves as a current-controlled current source, providing low driving point impedance  $R_{in} = 1/g_{in}$  for the input current source.

OTA with transconductance  $g_{out} = 1/R = 20$ mS delivers current  $I_{out}$  into an independent load  $R_{out}$ .

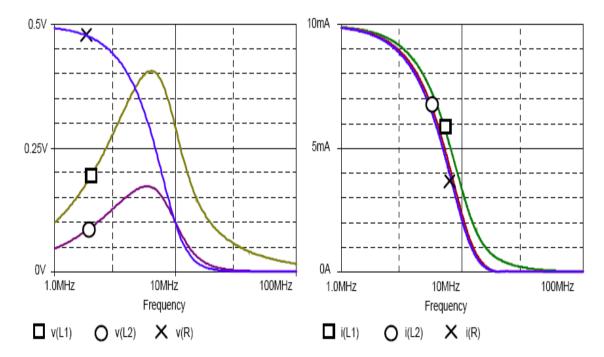

Let us design the active filter from Fig. 4-3 for a maximum driving current value of 10mA. The results of PSpice AC analysis of the passive LC ladder from Fig. 4-2 are shown in Fig. 4-4. The analysis was performed on the assumption of the attribute AC=10mA of the current source  $I_{in}$ . Those curves are depicted which are important for studying the filter dynamic range, i.e. the output voltage across R (i.e. the input voltage of the terminating OTA), the output current through R (i.e. the output current of the terminating OTA), the voltages across  $L_1$  and  $L_2$  (i.e. the input voltages of OTA No. 1 in the synthetic inductors from Fig. 4-1), and the currents through  $L_1$  and  $L_2$  (i.e. the output currents of OTA No. 2 in the synthetic inductors from Fig. 4-1). The curves are determined by the parameters of filter elements and they can be influenced only via choosing another realization structure, another approximation used here guarantees a maximally flat group delay response.

Fig. 4-4 shows that both the synthetic inductors and the terminating OTAs should be designed for a maximum current of 10mA. It is fulfilled for MAX435 when adjusting  $R_{set} = 5.9 \text{k}\Omega$ . The input voltage of the end OTA is maximum (1*V*) for low frequencies. The required

$g_m$  value of this OTA is 1/R = 20mA/V and it can be set via  $R_t = 200\Omega$  [57]. This amplifier will operate in the linear regime till its full current excitation.

The front-end OTA, excited by the current source  $I_{in}$ , will be designed with  $g_{in} = 100 \text{mA/V}$ or  $R_t = 40\Omega$   $\Box$  in order to provide low driving point impedance  $R_{in} = 1/g_{in} = 10\Omega$ . The maximum value of the input voltage will be 100mV for full current excitation of the filter input.

The curves  $V(L_1)$ ,  $V(L_2)$ ,  $I(L_1)$ , and  $I(L_2)$  can be used for designing the synthetic inductors. The voltage across  $L_1$  ( $L_2$ ) takes its maximum value 408mV (173mV) at a frequency of 6.31MHz (5.75MHz). As stated before, the currents are maximum, i.e. 10mA at a frequency of 0 Hz.

Fig. 4-4: Results of the AC analysis of LC ladder from Fig. 4-2 (a) for Iin = 10mA.

In the first step, a preliminary design of the synthetic inductors according to Eq. 4-1 will be performed. The initial capacitance in both inductors will be set to 100pF. For equal values of  $g_{m1}$  and  $g_{m2}$ , Eq. 4-1 leads to the results in Table 4-1.column (1).

|       |                              | (1) Before optimization | (2) After optimization |

|-------|------------------------------|-------------------------|------------------------|

|       | $g_{m1}$ [mA/V]              | 7.833                   | 24.505                 |

|       | $g_{m2}$ [mA/V]              | 7.833                   | 24.505                 |