## **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

## FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

## **DEPARTMENT OF RADIO ELECTRONICS**

ÚSTAV RADIOELEKTRONIKY

# SELECTED PRACTICAL APPLICATIONS OF FRACTIONAL TWO-PORT SYSTEMS IN IMMITTANCE AND TRANSFER FUNCTIONS

VYBRANÉ PRAKTICKÉ APLIKACE FRAKTÁLNÍCH DVOJPÓLŮ V IMITANČNÍCH A PŘENOSOVÝCH FUNKCÍCH

#### **DOCTORAL THESIS**

DIZERTAČNÍ PRÁCE

AUTHOR Ing. Ondřej Domanský

**AUTOR PRÁCE**

SUPERVISOR doc. Ing. Roman Šotner, Ph.D.

ŠKOLITEL

**BRNO 2024**

#### **Abstrakt**

Tato práce je rozdělena do pěti po sobě následujících částí (nepočítaje bibliografií). První část se zabývá představením implementace v navržené struktuře prvku s konstantní fázovou odezvou (constant phase element, dále jen CPE) založeného na sério-paralelním zapojení rezistorů a kondenzátorů. Následují rozbory vybraných zapojení pro implementaci takto navrženého CPE prvku a jejich možné srovnání s jinými zapojeními podobného typu v kapitole State of the Art. Cíle disertační práce, které byly stanoveny, jsou ve čtyřech bodech popsány v kapitole Objectives of Work. Úspěšnost plnění těchto bodů je pak probrána v závěrečné kapitole Concluding Discussion, společně s možností dalšího postupu implementací CPE prvků a jejich aplikace v obvodech. Hlavním bodem práce je druhá část Publications and Research sestávající se s publikovaných konferenčních článků a impaktovaných časopiseckých článků. Za zmínku stojí dva impaktované časopisy, pro publikaci v CSSP (Circuits, Systems, and Signal Processing), o tématu praktického návrhu RC aproximantů a jejich aplikace v CMOS konvejorech. Druhý článek, který měl nejsignifikantnější dopad na disertační práci byl publikován v impaktovaném časopise IEEE Access sestávající z problematiky elektronicky řiditelných a nastavitelných fraktálních filtrů. Obě navrhované aplikace v těchto impaktovaných časopisech nabízejí elektronickou ovladatelnost časové konstanty, hodnoty magnitudy a rekonfigurace. Čtenář bude seznámen s novými možnostmi použití CPE prvků v lineárních obvodech. Za účelem ověření prezentovaných konceptů byly u vybraných článků provedeny simulace v programu PSpice, stejně jako experimentální testy s vyrobenými čipy na pracovišti a s komerčně dostupnými prvky.

#### Klíčová slova

Konstantní fázový prvek (CPE), struktury neceločíselného řádu, proporční integrační a diferenční regulátor (PID, stejně tak  $PI^{\alpha}D^{\beta}$ ), napěťový diferenční proudový konvejor, frekvenčně závislé prvky, celočíselné a neceločíselné integrace a derivace

#### Abstract

This dissertation is organized into five consequential sections (excluding the bibliography). The initial section delves into the introduction of the implementation in the proposed structure of the element with a constant phase response (Constant Phase Element, henceforth referred to as CPE), based on a series-parallel configuration of resistors and capacitors. This is followed by analyses of selected configurations for the implementation of the proposed CPE element and a possible comparison with other configurations of a similar type in the State of the Art chapter. The objectives of the dissertation are described in four points in the Objectives of Work. The success in fulfilling these objectives is then discussed in the Concluding Discussion, along with further possibilities of the implementation of CPE elements and their applications in linear circuits. The second part is the core of this dissertation, consisting of published

conference papers and articles in impact journals. Noteworthy are two impact journals for publication in CSSP (Circuits, Systems, and Signal Processing) on the topic of practical design of RC approximants and their application in CMOS conveyors. The second paper, which had the most significant impact on the dissertation, was published in the impactful journal IEEE Access and consists of issues related to electronically controllable and adjustable fractional filters. Both those proposed impact paper applications offer electronic control over the time constant, magnitude values, and reconfiguration. The reader will be introduced to new possibilities for the application of CPE elements. For the purpose of verification of the presented concepts, selected simulations were conducted in the PSpice program for some articles, as well as experimental tests with fabricated chips in the lab and with commercially available components.

#### **Key words**

Constant phase element (CPE), fractional-order dynamics, proportional integrational and differential controller (PID, also  $PI^{\alpha}D^{\beta}$ ), voltage differencing current conveyor, frequency dependent elements, integer and non-integer integrations and derivations

DOMANSKÝ, Ondřej. Vybrané praktické aplikace fraktálních dvojpólů v imitančních a přenosových funkcích [online]. Brno, 2025 [cit. 2025-06-30]. Dostupné z: https://www.vut.cz/studenti/zav-prace/detail/161032. Dizertační práce. Vysoké učení technické v Brně, Fakulta elektrotechniky a komunikačních technologií, Ústav radioelektroniky. Vedoucí práce Roman Šotner.

#### **DECLARATION**

I declare that I have written the Doctoral Thesis titled "Emulators of immittances of higher orders and their applications" independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the thesis and listed in the comprehensive bibliography at the end of the thesis.

As the author I furthermore declare that, with respect to the creation of this Doctoral Thesis, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation §11 of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll., Section 2, Head VI, Part 4.

| Brno | <br>               |

|------|--------------------|

|      | author's signature |

#### **ACKNOWLEDGEMENT**

Rád bych poděkoval mému vedoucímu práce Romanovi Šotnerovi za jeho přesný metodologický postup při práci na všech projektech, které mě při doktorském studiu potkaly. Bez jeho pomoci a schopnosti motivovat lidi kolem sebe by dokončení této práce nebylo možné. Bezesporu je tím nejlepším vedoucím, kterého jsem si mohl vybrat ke zdárnému odevzdání doktorské práce. Pokud bych měl někdy v budoucnu doporučit někomu vedoucího jeho bakalářské, magisterské nebo doktorské práce, bude to určitě Roman. Dále bych taky poděkoval všem kolegům UREL, za vytvoření kolektivu podporujícího přirozenou kreativitu a dobré podmínky ke studiu a práci.

## **Contents**

|   | Preamble                                                                               |            |

|---|----------------------------------------------------------------------------------------|------------|

| 1 | Introduction                                                                           | 12         |

|   |                                                                                        |            |

| 2 | State of the Art                                                                       | 13         |

|   | 2.1 Fraction Calculus and Constant Phase Element                                       | 13         |

|   |                                                                                        |            |

|   | 2.2 Electronically Reconfigurable and Tunable Fractional-Order Two-P Network           |            |

|   |                                                                                        |            |

|   | 2.3 Possible Application of Fractional-Order Filter                                    | 15         |

| 3 | Objectives of the Work                                                                 | 17         |

| J | objectives of the work                                                                 | ······ 1 / |

| 4 | Concluding Discussion                                                                  | 19         |

| • |                                                                                        |            |

|   | 4.1 Future Research Possibilities                                                      |            |

|   | 4.2 Main Body of the Thesis                                                            | 20         |

|   | Bibliography                                                                           | 22         |

|   | Publications and Research                                                              |            |

|   | A Publication Summary Related to Objectives of Work                                    | 26         |

| A | Practical Design of RC Approximants of Constant Phase Elements                         |            |

|   | and Their Implementation in Fractional-Order PID Regulators Using                      |            |

|   | CMOS Voltage Differencing Current Conveyors                                            | 28         |

|   | A.1 Introduction                                                                       | 30         |

|   | A.1.1 Constant Phase Element (CPE)                                                     | 31         |

|   | A.1.2 State of the Art of Fractional-Order Passive Elements and $PI^{\alpha}D^{\beta}$ |            |

|   | Regulator Designs                                                                      |            |

|   | A.2 Practical Design of Passive CP                                                     |            |

|   | A.2.1 Available Passive Structures Suitable for CPE Synthesis                          |            |

|   | A.2.2 Design Example of Passive CPE                                                    |            |

|   | A.3 Special Solution of $PI^{\alpha}D^{\beta}s$ Based on VDCC Elements                 | 44         |

| A     | .3.1   | Description of VDCC Element                                  | 44             |

|-------|--------|--------------------------------------------------------------|----------------|

| A     | .3.2   | Designed PI <sup>α</sup> D <sup>β</sup> Controller           | 46             |

| A     | .3.3   | Measurement Results                                          | 49             |

| A.4   | Con    | clusion                                                      | 52             |

|       | Ack    | nowledgements                                                | 53             |

|       | Refe   | rences                                                       | 53             |

|       |        |                                                              |                |

| Integ | er-ar  | nd Fractional-Order Integral and Derivative Two-Port         |                |

| Sum   | matio  | ons: Practical Design Considerations                         | 57             |

| B.1   | Intro  | oduction                                                     | 59             |

| B.2   | Gene   | eral Concept of Two-Port Interconnection                     | 63             |

| B.3   | Pass   | ive Solution of Constant Phase Element                       | 64             |

| B.4   | Ana    | lytical Analysis of Two-Port Interconnections                | 65             |

| В     | .4.1   | Sum of Integer and Fractional-Order Integrator Responses.    |                |

| В     | .4.2   | Sum of Integer and Fractional-Order Differentiator Respon    | ses 67         |

| В     | .4.3   | Sum of Integer-Order Integrator and Fractional-Order         | Differentiator |

|       |        | Responses                                                    | 68             |

| В     | .4.4   | Sum of Fractional-Order Integrator and Integer-Order         | Differentiator |

|       |        | Responses                                                    | 69             |

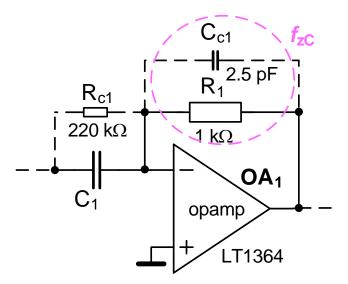

| B.5   | Solv   | ing Non-Ideal Issues during the Tests                        | 70             |

| B.6   | Expe   | erimental Anal                                               | 71             |

| В     | .6.1   | Analysis of Integer-and Fractional-Order Integrators and     |                |

|       |        |                                                              |                |

|       | .6.2   | Analysis of Sum of Integer and Fractional-Order Integrator   | •              |

| В     | .6.3   | Analysis of Sum of Integer and Fractional-Order              |                |

|       |        | Responses                                                    |                |

| В     | .6.4   | Analysis of Sum of Integer-Order Integrator and Fra          |                |

|       |        | Differentiator Responses                                     |                |

| В     | .6.5   | Analysis of Sum of Fractional-Order Integrator and           | =              |

|       |        | Differentiator Responses Analysis                            |                |

| B.7   |        | clusion                                                      |                |

|       |        | nowledgements                                                |                |

|       | Refe   | erences                                                      | 81             |

| High  | er Oı  | rder Differentiator Block for Synthesis of Controllable      |                |

|       |        | y Dependent Element                                          | 84             |

| C.I.  |        | oduction                                                     |                |

|       |        | eral Electronically Controllable Higher Order Differentiator |                |

|       |        | 3rd-order Differentiator                                     |                |

|       |        | Integer Order Electronically Tunable Negative/positive Fre   |                |

| _     | •      | Dependent Resistor                                           |                |

| C     | .II.C. | Fractional Order FDNR                                        |                |

|       |        |                                                              |                |

|   | C.III. | Examples of Application                                              | 88      |

|---|--------|----------------------------------------------------------------------|---------|

|   | C.IV.  | . Conclusion                                                         | 89      |

|   |        | References                                                           | 89      |

| D | Reco   | nfigurable Impedance Converter for Synthesis of Integer and          | ]       |

|   | Frac   | tional-Order Synthetic Elements                                      | 90      |

|   | D.I    | Introduction                                                         |         |

|   | D.II   | Newly Proposed Structure of a Synthetic Inductor with Four Active    |         |

|   |        | Elements                                                             | 93      |

|   | D.III  | The Additional Extension of Control with Second Current Conveyor     | 94      |

|   | D.IV   | Substitution of Capacitance for Constant Phase Element               | 94      |

|   | D.V    | Conclusion                                                           | 95      |

|   |        | References                                                           | 95      |

| E | Elect  | tronically Reconfigurable and Tunable Fractional-Order Filter        | ]       |

|   |        | g Resonator Concept and Feedforward Path for Low-Frequency           |         |

|   | Tone   | Signalization                                                        | 97      |

|   | E.I    | Introduction                                                         | 99      |

|   | E      | .I.A Reconfigurable Filters                                          | 100     |

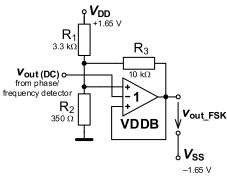

|   | E      | .I.B Phase Detector                                                  | 101     |

|   | E      | .I.C Contribution of This Work                                       | 102     |

|   | E      | .I.D Organization                                                    | 102     |

|   | E.II   | Proposed Solution of Special Fractional-Order Filter                 | 102     |

|   | E.III  | Description of Active Devices                                        | 105     |

|   | E.IV   | Experimental Verification                                            | 105     |

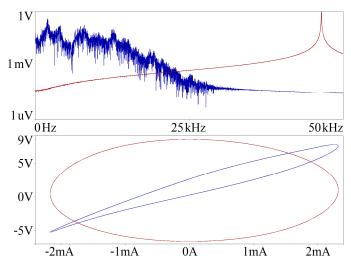

|   | E      | .IV.A Tests of the Filter                                            | 106     |

|   | E      | .IV.B Application Example of Reconfigurable Filter - Phase/Frequency |         |

|   |        | Detector for Frequency Detecting System of Frequency Keying          |         |

|   |        | Demodulation                                                         |         |

|   | E.V    | Conclusions                                                          | 112     |

|   |        | References                                                           | 113     |

|   | Time   | eline and Summary of Other Publications with an Author's Contr       | ibution |

|   | •••••  |                                                                      | 115     |

| F |        | gn Method Based on Modification of the Transformation of Hor         |         |

|   | Struc  | ctures in Current-Mode Frequency Filters                             | 119     |

|   | F.1    | Introduction                                                         | 120     |

|   | F.2    | Modification of the Horizontal Structures Transformation Method      | 121     |

|   | F.3    | Simulations and Results                                              | 122     |

|   | F.4    | Conclusion                                                           | 123     |

|   |        | Acknowledgement                                                      | 123     |

|   | References                                                          | 123      |

|---|---------------------------------------------------------------------|----------|

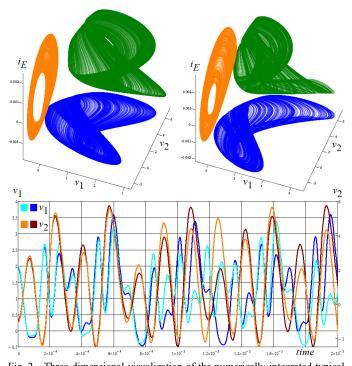

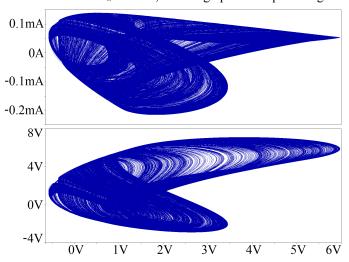

| G | Simple Chaotic Oscillator with Wideband Passive Fractional-Order    |          |

|   | Inductor                                                            | 125      |

|   | G.I Introduction                                                    | 126      |

|   | G.II Configuration of Chaotic Oscillator                            |          |

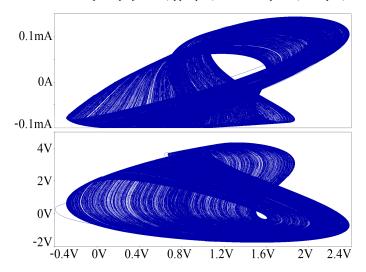

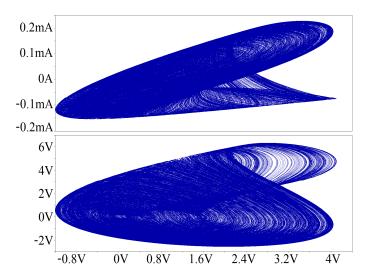

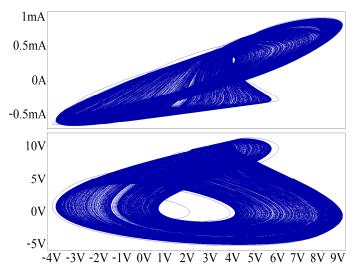

|   | G.III Design of FO Two-Terminal Device                              |          |

|   | G.IV Orcad Pspice Verification of FO Chaotic System                 |          |

|   | G.V Conclusion                                                      | 130      |

|   | References                                                          | 130      |

|   |                                                                     |          |

|   |                                                                     |          |

| H | Comparison of Simple Design Methods for Voltage Controllable Resist | ance 131 |

|   | H.I Introduction                                                    |          |

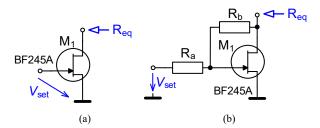

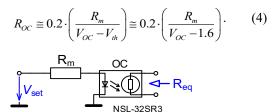

|   | H.II Easily Available Methods of Resistance Control                 | 133      |

|   | H.II.A Single J-FET transistor                                      | 133      |

|   | H.II.B Optocoupler                                                  | 133      |

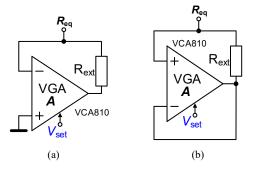

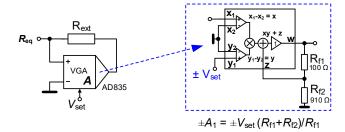

|   | H.II.C Variable Gain Amplifier                                      | 134      |

|   | H.III Analysis of Presented Solutions                               | 134      |

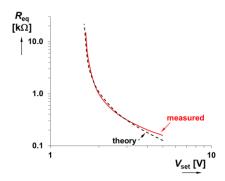

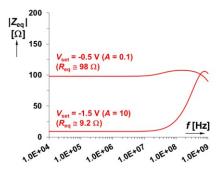

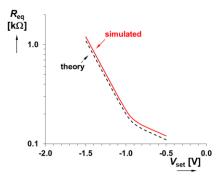

|   | H.III.A Simulation of J-FET in linear regime                        |          |

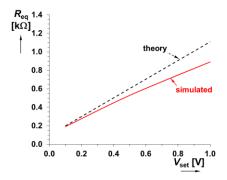

|   | H.III.B Measurement of optocoupler                                  |          |

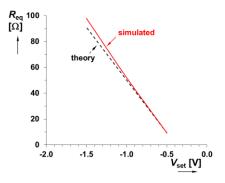

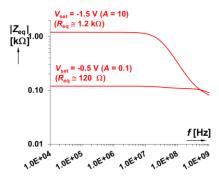

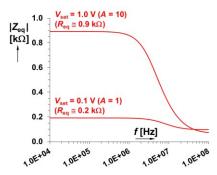

|   | H.III.C Simulation of Variable Gain Amplifier Based Resistance      |          |

|   | H.IV Comparison of Studied Solutions                                |          |

|   | H.V Conclusions                                                     |          |

|   | References                                                          | 137      |

|   | Appendix                                                            |          |

|   | Curriculum Vitae                                                    | 140      |

## **PREAMBLE**

Introduction

State of the Art

Objectives of the work

Concluding discussion

#### 1 Introduction

Fractional calculus is a branch of mathematical analysis that extends further development of the concept of differentiation and integration from integer orders up to real or complex orders. It provides a general framework for operations like differentiation and integration. The mathematical conception and the unconventional natural behavior of fractional calculus makes it a rich field for research, with potential applications still being explored in scientific and engineering disciplines, which have attracted increasing attention of researchers.

The historical background of fractional calculus is fascinating, as it goes back over several centuries, with early contributions from some of the most renowned mathematicians like Leibniz [1], Liouville [2], Riemann [3], Butzer [4] and many others [5], [6]. It was initially an only theoretical field, exploring the mathematical and extending knowledge of the traditional calculus. Despite its early establishment, the field remained largely theoretical until its potential was discovered in the late 20th century when there were many natural systems uncovered, which couldn't be accurately modeled by integer-order differential equations but could be described very efficiently by fractional-order differential equations. The recovery of interest in fractional calculus was fueled by the discovery of its applicability in modeling physical systems characterized by constant phase response. One of the first mention was in 1950 by Borisova and Ershler [7] following with more modern calculus statements [8], [9], [10], [11], [12].

As a fractional calculus evolved from a purely theoretical concept into a robust analytical tool, the evolution has seen its transition from complex mathematical constructs to a practical instrument of innovation and the shift in how scientists and engineers employ fractional calculus for modeling complex behaviors in their respective fields. With the continuous progression of research and the enhancement of computational capabilities, the future of the fractional calculus appears highly promising.

#### 2 State of the Art

#### 2.1 Fraction Calculus and Constant Phase Element

The RC network whose immittance is characterized by almost constant phase shift over an extended frequency range [13] (now so-called constant phase element - CPE) is a concept used in electrochemistry and impedance spectroscopy to model the frequency-dependent impedance element. Unlike an ideal capacitor, which has a frequency-independent capacitance that introduces a phase shift of exactly  $-90^{\circ}$  between voltage and current (phase shift of  $0^{\circ}$  for resistor), a CPE can stand for the non-ideal behavior observed in real systems. A significant challenge in the practical implementation of CPE lies in its lack of commercial availability. However, in recent years, various substitutes for CPEs have been developed. These alternative solutions can be based on electrochemical components, as referenced in [14], [15], [16], organic materials as well as polymer composites [8], [17], [18], [19], [20]. Additionally, there has been progress in creating thick film layers composed of resistive, dielectric, and insulating materials on silicon substrates, as documented in [8], [20], [21]. The impedance  $Z_{CPE}$  of the ideally proposed CPE is:

$$Z_{CPE} = R_s + \frac{1}{j\omega C_s},\tag{1.1}$$

where  $R_s$  and  $C_s$  stand for finial form of non-integer impedance and capacitance respectively, j is the imaginary unit and  $\omega$  is the angular frequency response equal to  $\omega = 2\pi f$ . In our application this equation could be simplified for further development of CPE with custom phase deviation as  $\lceil 8 \rceil$ ,  $\lceil 12 \rceil$ :

$$Z_{CPE} = \frac{1}{Y_0(j\omega)^{\alpha}} \left[ F^{1/\alpha} s^{(\alpha-1)/\alpha} \right], \qquad (1.2)$$

where  $\alpha$  is a proportionality of constant that represents the magnitude of the CPE. It's related to the capacitance in an ideal capacitor,  $\alpha$  characterizes the phase order of the final CPE element. It varies in range from  $\alpha \leq \pm 1$  and depends on phase shift  $\varphi$  ( $\alpha = 1 - \varphi/90^{\circ}$ ) [8]. Detailed description and discussion of the non-integer order passive two-terminal element can be seen in chapter Publication and Research under the Chapter A: Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors, described in [8].

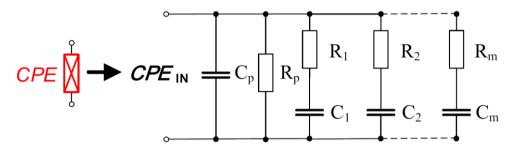

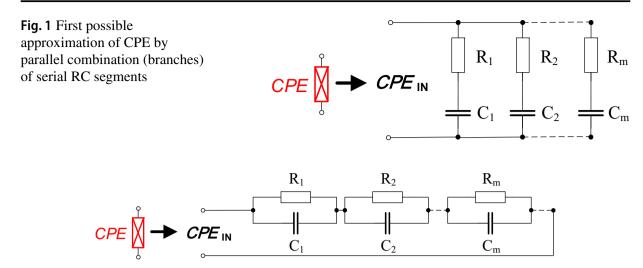

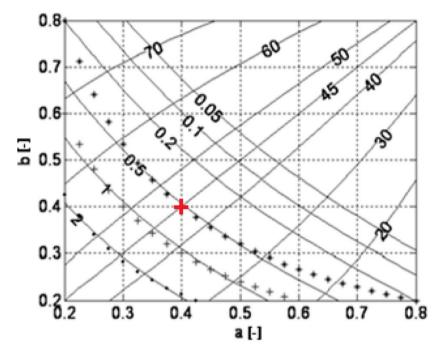

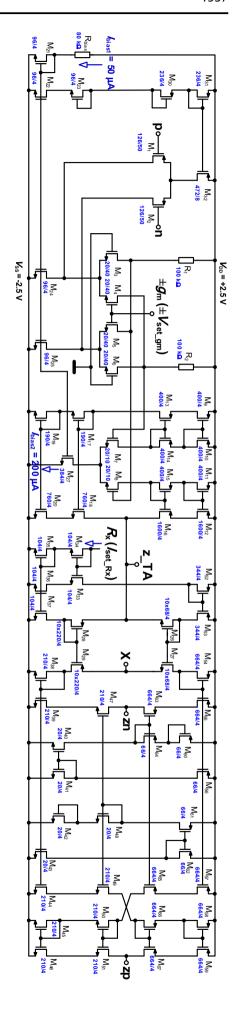

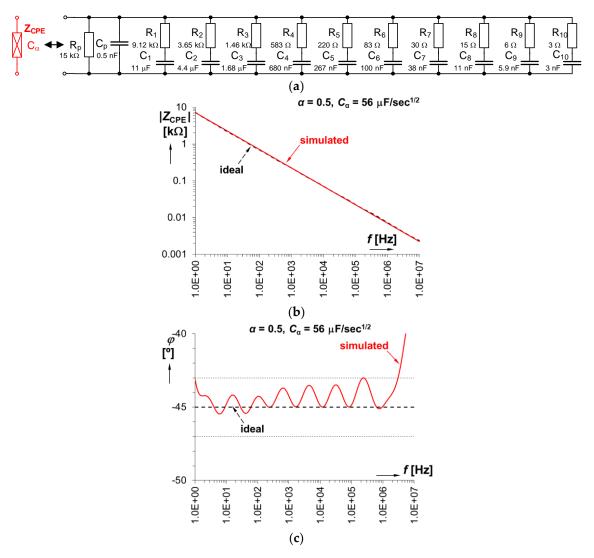

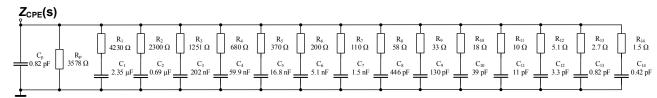

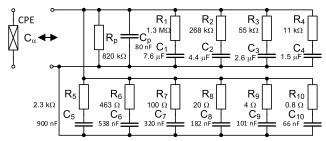

As previously discussed, there are several ways to create a CPE element that ensures a constant phase shift within a specified frequency range. For the purpose of this thesis, the most promising and frequently utilized structure will be the approximation of CPE through a resistor-capacitor configuration (RC [8], [11]). Detailed approximation of the serial-parallel structure can be seen on Figure 1. For more practical usage the mathematical foundation offers several approaches for approximation of CPEs [11], [12], [22], [23], aiming to achieve the desired bandwidth and phase ripple. These methods result in a specific distribution of zeros and poles (the roots of polynomial symbolical expression of impedance/admittance) related to the

previously mentioned passive RC sections [22]. The chosen approximation method and the calculation algorithm are detailed and further elaborated in [8]. In our case, the design of the CPE is based on the RC structure depicted in Figure. 1 is presented as an example. The final and corrected input admittance of the CPE can be expressed as [8], [22]:

$$Y(s) = sC_p + \frac{1}{R_p} + \sum_{i=1}^{m} \frac{sC_i}{sC_iR_i + 1},$$

(1.3)

**Figure 1.** Scheme of an approximation of CPE by serial-parallel combination (branches) of RC segments [8]

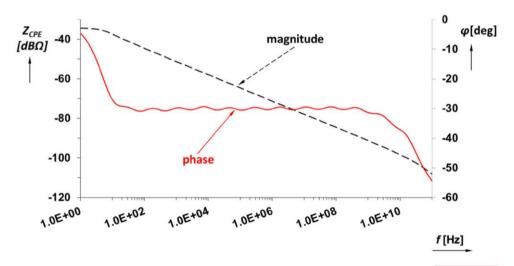

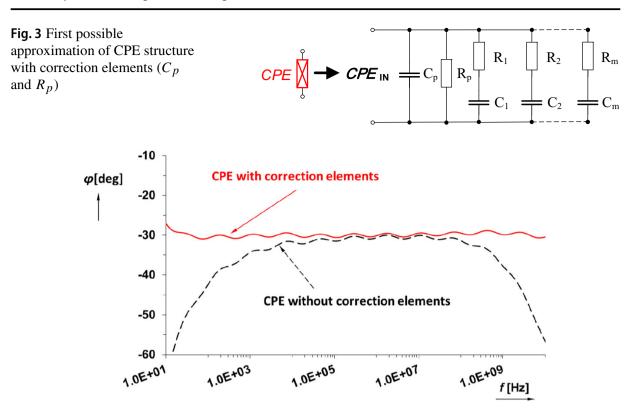

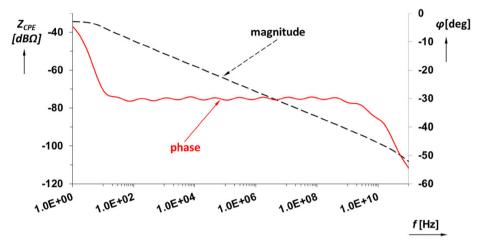

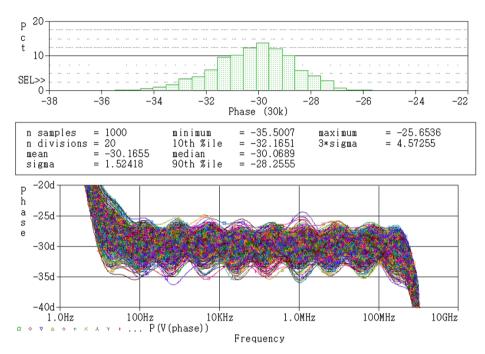

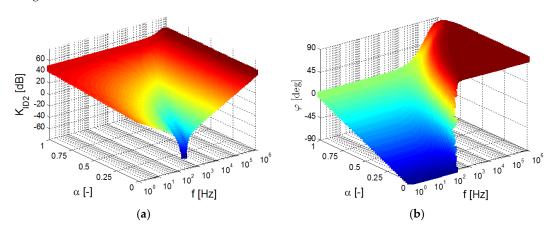

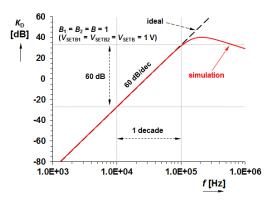

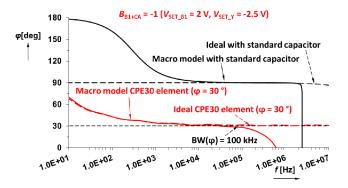

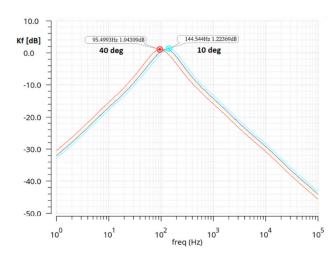

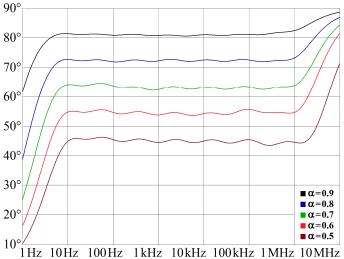

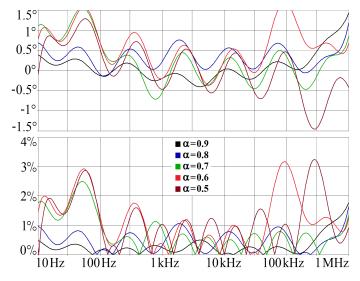

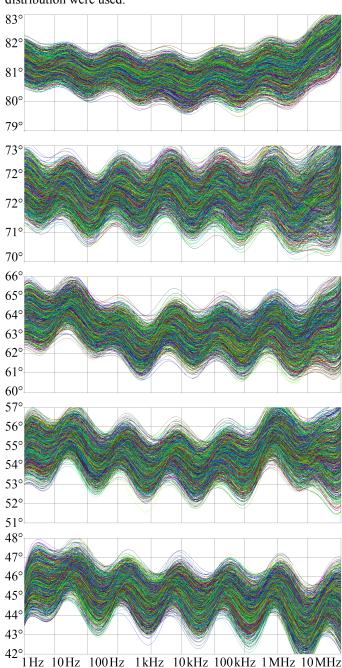

Simulation results in Figure 2, demonstrating example of phase ripple and magnitude of a designed CPE, were obtained for specific values (selected example) of  $\varphi = 30^{\circ}$ . Such a designed element is further used in Chapter A: Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors [8].

**Figure 2.** Simulation results of approximated CPE (exact values calculated in Chapter A: Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors) for phase shift  $\varphi = 30^{\circ}$  and its magnitude [8]

## 2.2 Electronically Reconfigurable and Tunable Fractional-Order Two-Port Network

In numerous instances, the need arises for altering the transfer response (such as the type or bandwidth limit) in signal processing. However, just tunability or the ability to manual selection of the output often falls short of meeting these requirements, as pointed out in [24], [25]. The complexity of reconfiguring a filter's transfer response surpasses the capabilities of standard active devices like operational transconductance amplifiers [9]. This is because a broader spectrum of variables, including pass-band gain and pole frequency, are involved, as noted in [26].

#### 2.3 Possible Application of Fractional-Order Filter

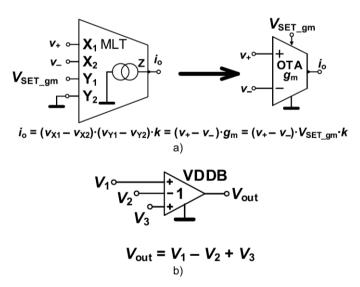

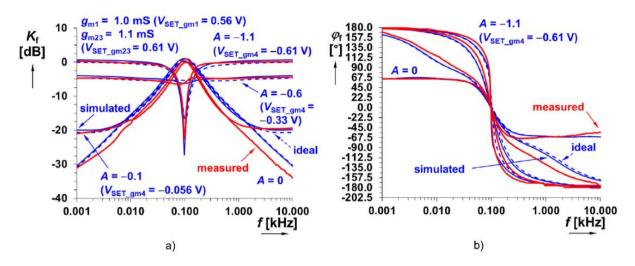

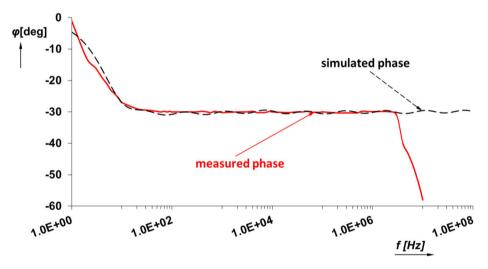

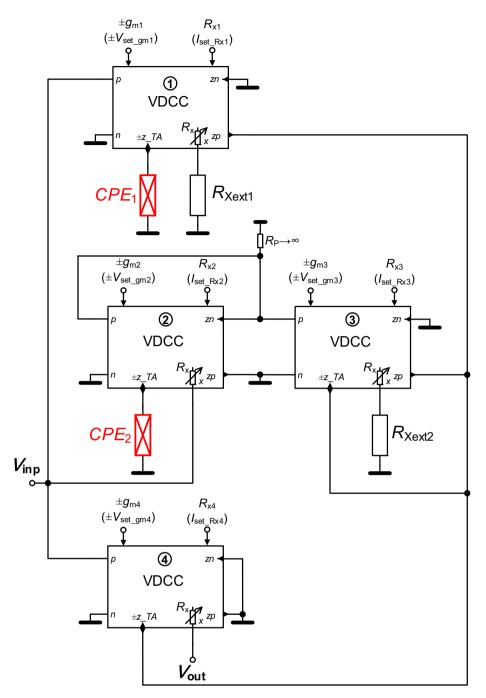

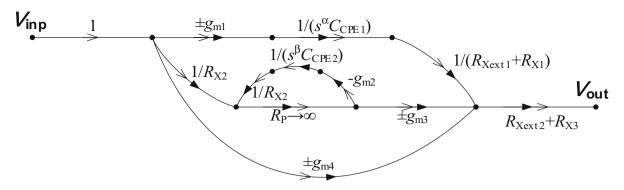

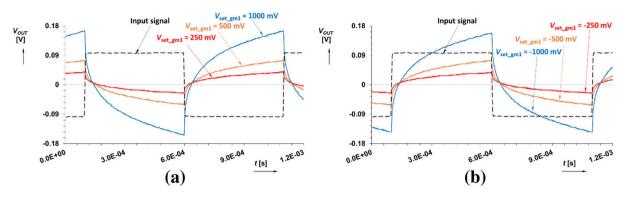

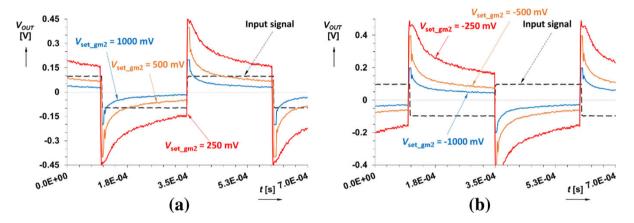

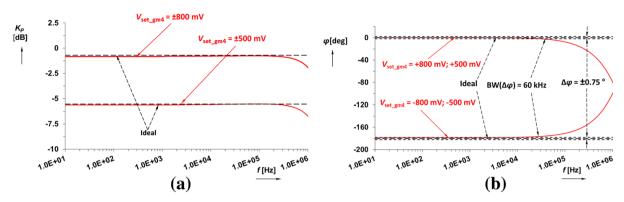

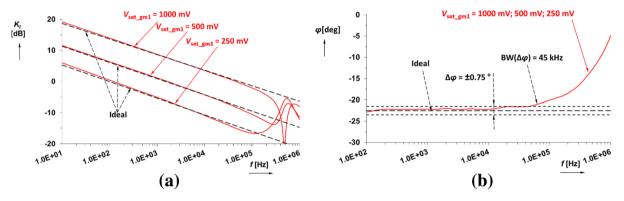

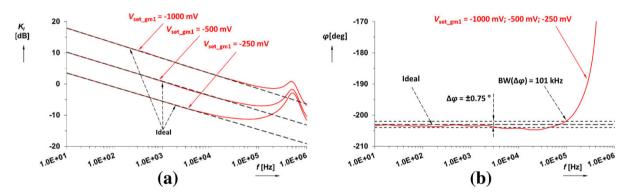

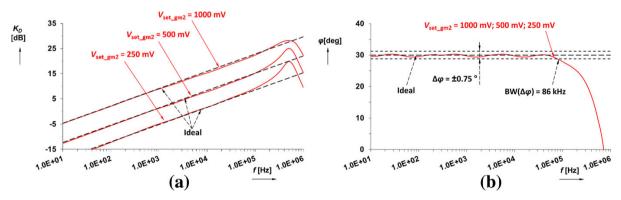

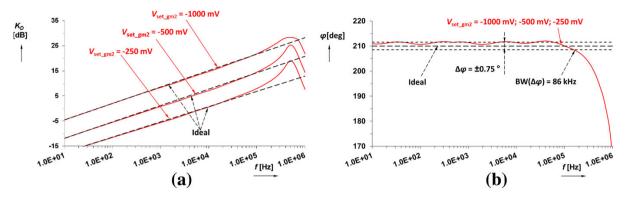

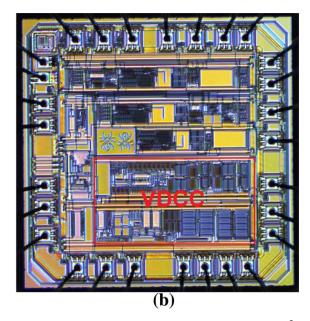

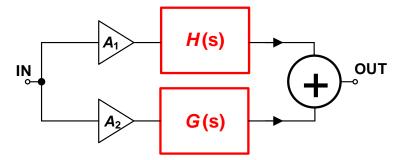

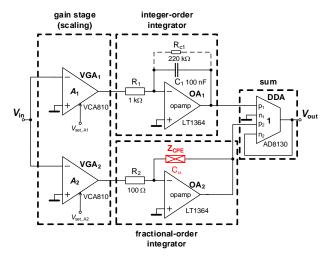

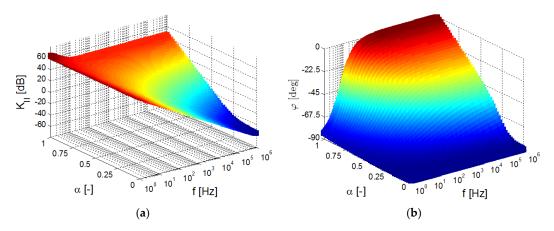

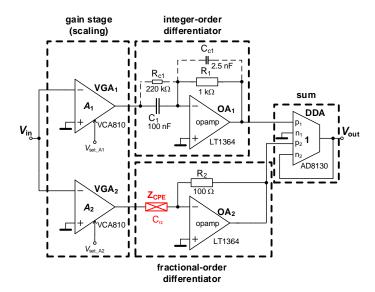

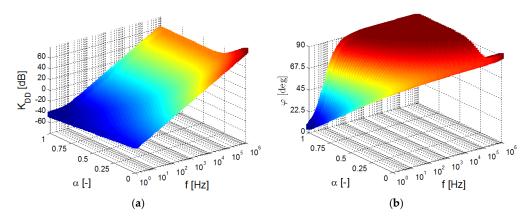

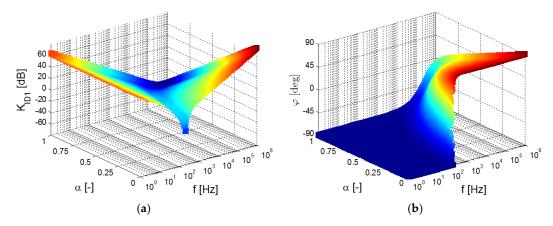

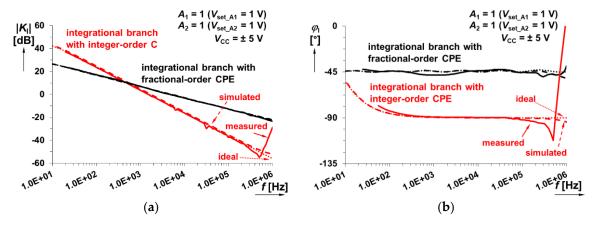

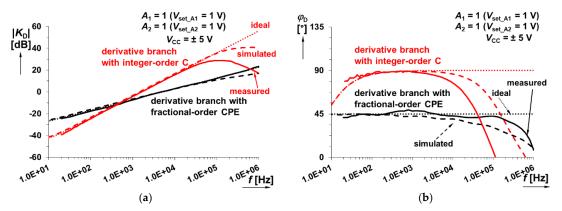

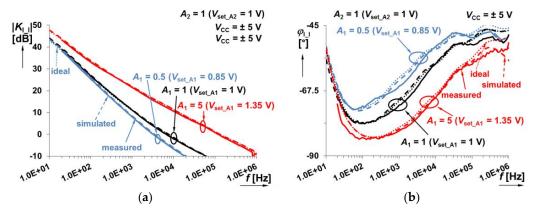

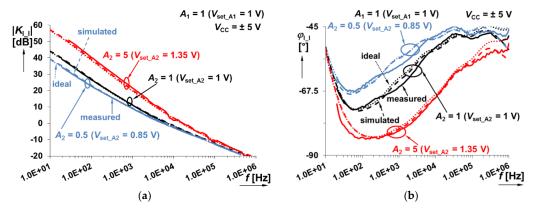

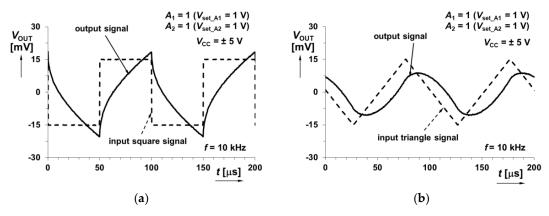

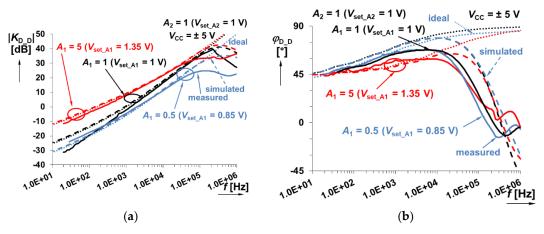

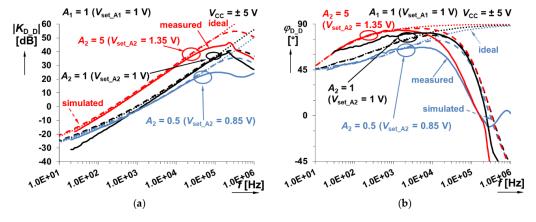

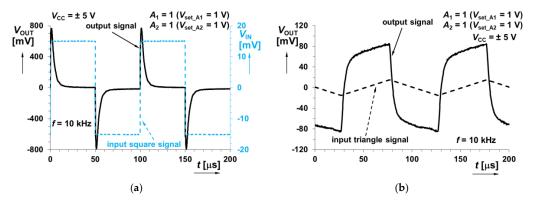

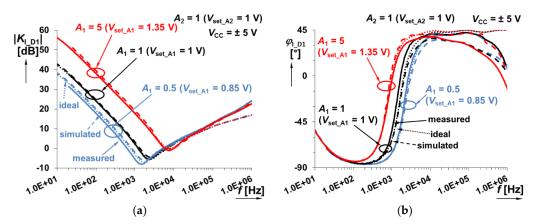

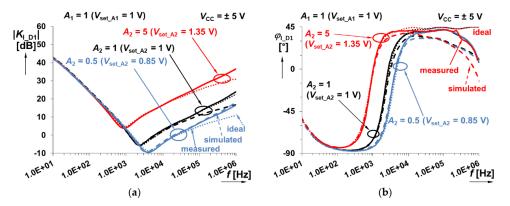

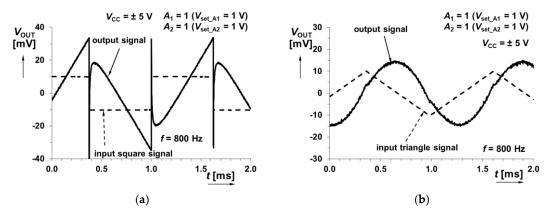

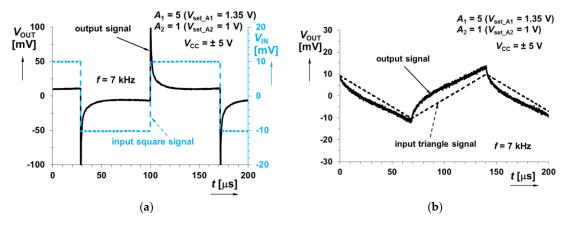

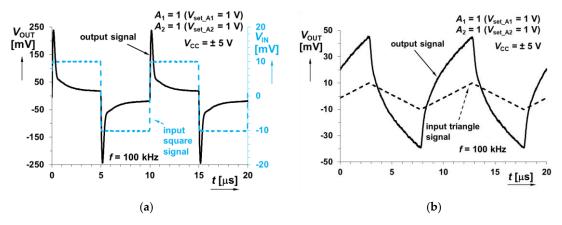

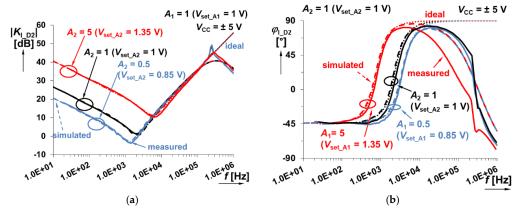

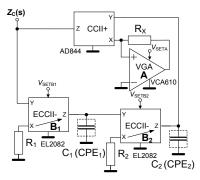

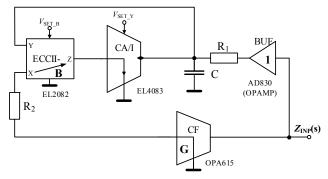

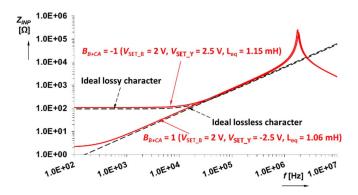

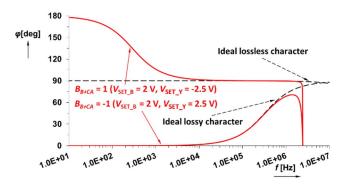

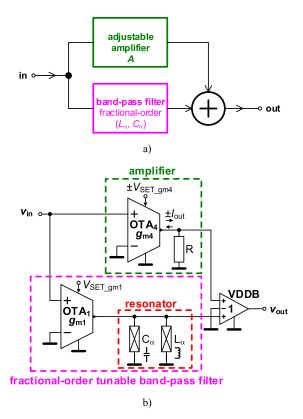

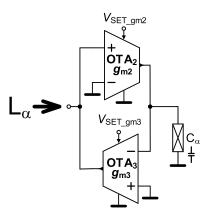

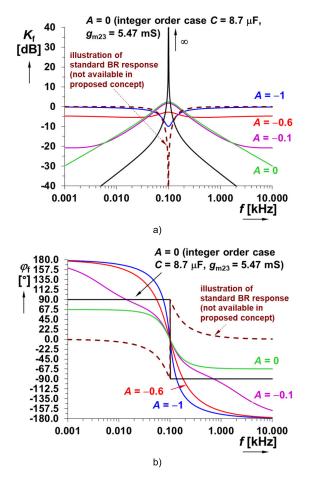

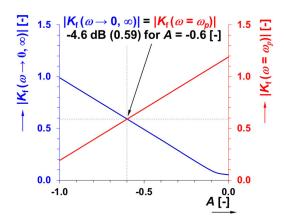

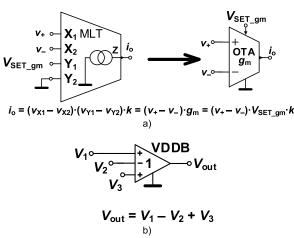

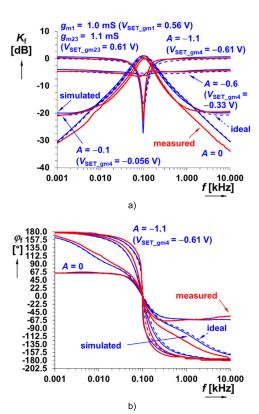

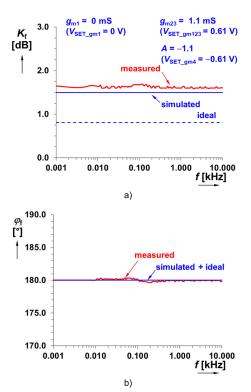

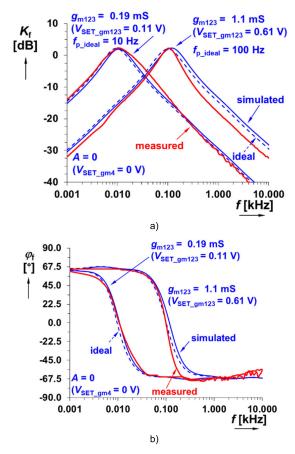

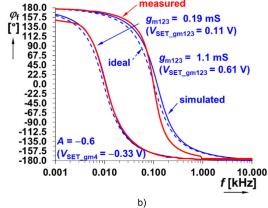

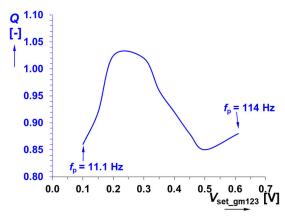

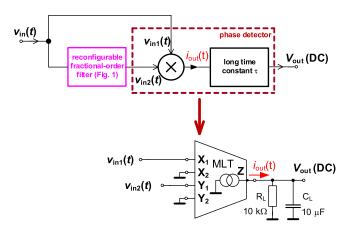

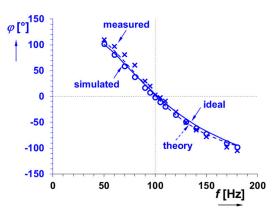

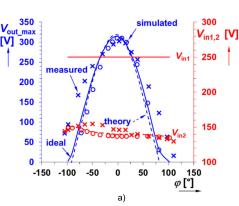

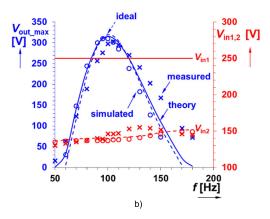

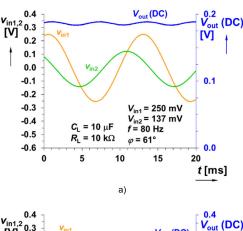

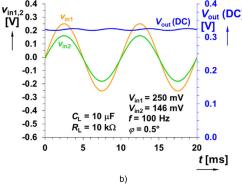

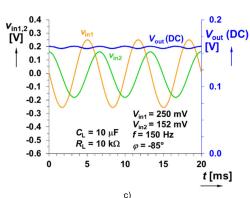

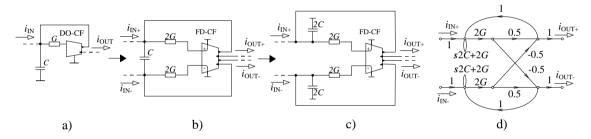

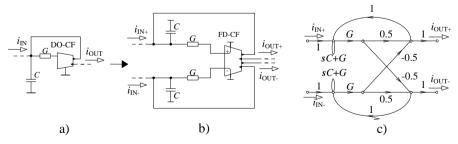

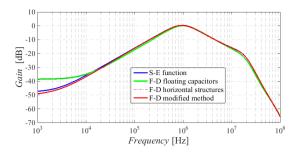

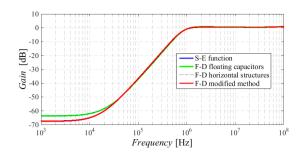

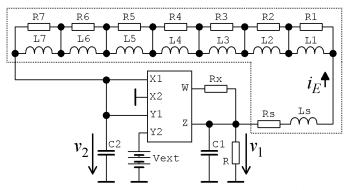

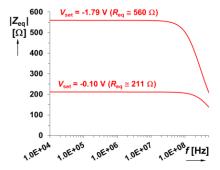

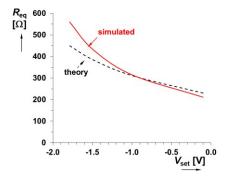

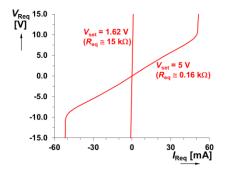

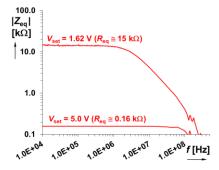

The solution of fractional-order (FO) circuits (as they are also stated in previous chapter 2.1) [12], [27], [28], [29], [30], introduces innovative features to this field. Unlike integer-order systems, FO circuits allow for the setting of area transition between stop-bands and pass-bands with a more gradual slope as referenced in [9], [27], [31], [32], [33] or as the example of the electronically reconfigurable fractional-order filter presented in Figure 3 and Figure 4. This unique feature arises from the magnitude slope's dependence on frequency, which is intrinsically linked to the order of the FO components employed in the circuit design, a concept further elaborated in [28]. More specific requirements on the slope of response of such a circuit can be fulfilled by applying FO approaches [34], [35], [36]. This property of FO circuits lays the groundwork for a more tunable and flexible approach to filter design and signal processing.

**Figure 3.** Possibility of configuration of active devices used for construction of the special fractional-order reconfigurable filter and its application: a) analog multiplier as OTA application, b) voltage differencing differential buffer [9]

**Figure 4.** An example of possible frequency responses of a reconfigurable filter: a) magnitude responses, b) phase responses [9]

#### 3 Objectives of Work

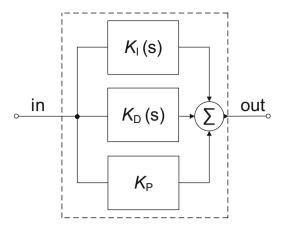

Objective 1: Initial research on the topic of fractional-order elements. Namely the design of a voltage and current controlled fractional-order PID regulator with reduced topology using known CPE design approach extended to more frequency decades. Following by the next specific part of this objective focuses to implementation of fractional-order behavior in the two-port design used in construction of complex analog systems (filters, controllers) especially for integer and fractional order response combination. The research question is: "What is the product of the sum of responses processed by integer and fractional-order path?".

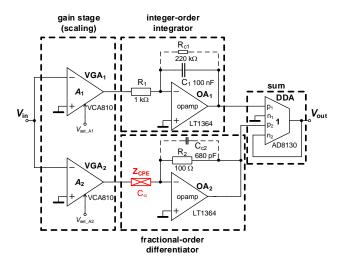

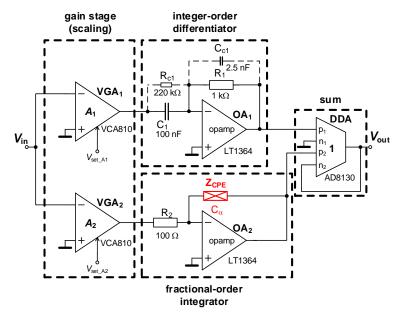

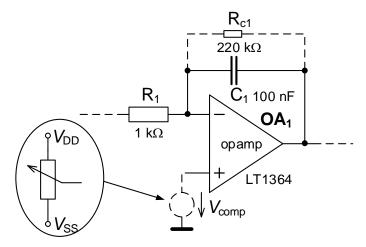

Recent designs of fractional-order PID regulators show significant lack of simple electronic variability and controllability of parameters, especially when standard operational amplifiers are used as active devices Chapter A. This subpart of this objective was partially fulfilled by a novel topology of PID using voltage differencing current conveyors (VDCC) and two CPE devices (structures and values adopted from Chapter A). The electronic adjustment allows simple time constant control by DC voltages and currents. There is an availability for implementing special CMOS active devices and circuit topology using only grounded passive elements (including CPEs). This fact is beneficial for possible integration of the complete device. The method as well as a complete algorithm of designing CPE element is described in Chapter A.

The second part of this objective consists of complex analog system and their integer and fractional order responses which they were not tested in previous works in literature in this specific form. The second authorship and the issues addressed regarding this topic are presented in Chapter B and Chapter C. Beyond fractional order elements, the reader can learn about practical solutions for the summing response of fractional and integer order differentiators, as well as a detailed Mathcad analysis of various functions. Results in Chapter B uses a summing block and two paths using independently adjustable voltage gains and including two different transfer responses (integrator, differentiator, twoport of higher order Chapter C) where each of them has an integer-order character and the second one has a fractional-order character. Presented results in 3D plots indicate very interesting and useful responses (especially for filtering applications, so-called inverse response filters Chapter B). Moreover, many practical advice and recommendations are presented (preventing issues of DC offsets a high-gain frequency bands, instability compensations, etc.). Also, as a side note a versatile type of electronically controllable bilinear transfer segments, i.e. two-ports allowing an independent electronic control of zero and pole of a transfer function. It is based on a modified current differencing unit (MCDU) as a part of a novel two-path system of the fractional-order proportional-integral or a derivative (FOPI/D) controller [35].

Objective 2: Proposal of novel active synthetic impedance (inductor) using current gain adjustment for simple electronic (voltage) tuning of equivalent inductance as well as losses of the synthetic inductor. This feature is not typically solved in similar state-of-the-art solutions (or standard operation amplifier-based solutions).

This objective presents design and study of difference between integer and fractional-order impedance (synthetic inductor) allowing impedance magnitude adjustment (inductance value adjustment). The adjustment of equivalent inductance is provided by a single current gain (controlled by DC voltage) and an adjustment (or minimization) of serial losses by the second adjustable current gain parameter. Therefore, presented topology fulfills the intended target of this objective regarding standard solutions in literature.

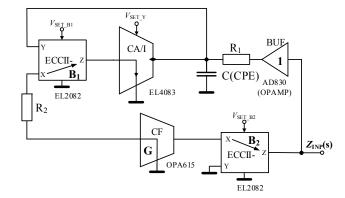

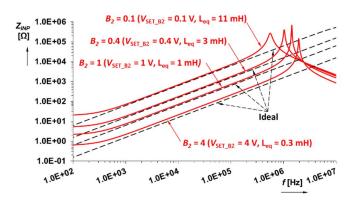

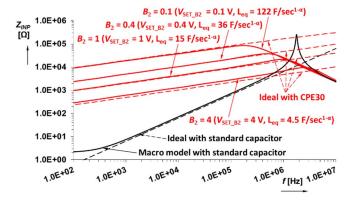

The objective was also addressed and actualized throughout the entire thesis. It is crucial to alter parameters (ideally DC voltage) of the final network structure without having to modify the internal configuration of the circuit. Chapter D presents paper that addresses this issue. It employs widely used and electronically controllable current conveyors, integrating CPE elements in the process for integrating more electronic controllability of the magnitude of input impedance via DC voltage  $V_{SET\ B}$  parameter Chapter D, [36].

Objective 3: The last objective targets the implementation of fractional-order behavior in the design of special resonator with feature of magnitude response reconfigurability. This feature was not tested in a selective transfer response generation, but in several fractional-order reconfigurable two-ports (filters).

This field of study is not so well described or published in literature. The proposed solution introduces distinctive transfer responses, not present in conventional models, that have significant potential in various applications, such as adaptive frequency equalizers and random distortion level control. For instance, the fractional-order resonator implementation may be used in the phase/frequency detection or in achieving synchronization between two signals of the same frequency and phase. These topics are thoroughly discussed in Chapter E.

#### 4 Concluding Discussion

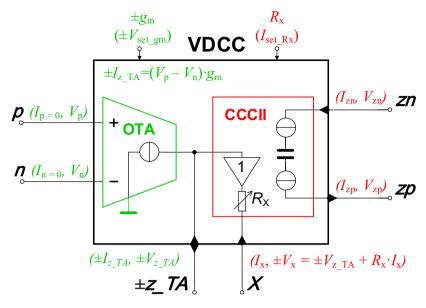

This doctoral thesis has firstly undertaken a comprehensive initial analysis for electronical application of fractional calculus and its theoretical foundations, tracing its developmental trajectory, and highlighting its expanding integration into diverse scientific and engineering disciplines such as novel the topology of the  $PI^{\alpha}D^{\beta}$  regulator, which can be seen in Chapter A: Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors. This marks the author's initial impact journal publication in their doctoral studies, thus signifying its importance. It addresses the complexities and methodologies for the design and application of  $PI^{\alpha}D^{\beta}$  regulators, topology utilizes fabricated complementary metal-oxidesemiconductor (CMOS) voltage differencing current conveyors (VDCC), and the detailed design of the CPE element. Furthermore, it provides a critical in-depth analysis of the current research of the state, and a comparison of selected contemporary works up to the date of this publication Chapter A. Work continues with deeper understanding of the analysis of specific types of transfer functions obtained by the summing operation of integer-order and fractional-order two-port responses. Various operations provided by fractional-order, two-terminal devices utilizing those kinds of electronically reconfigurable elements and their Mathcad simulation could be seen in Chapter B: Integer-and Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations. Following by the next group of articles with main authorship comprises of conference paper, marking contributions to the field of higher order differentiator synthesis. The first that could be seen in Chapter C: Higher Order Differentiator Block for Synthesis of Controllable Frequency Dependent Elements, delves into the development of a sophisticated framework for creating elements that exhibit frequency-dependent behaviors, structure of generally nth-order differentiator transfer block serving for purpose of integer order or fractional order immittance synthesis.

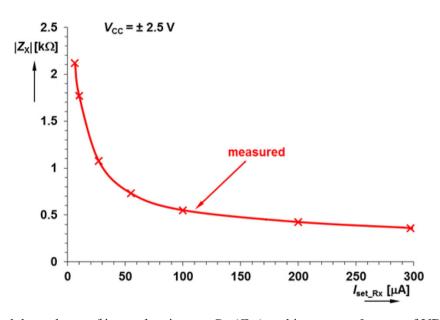

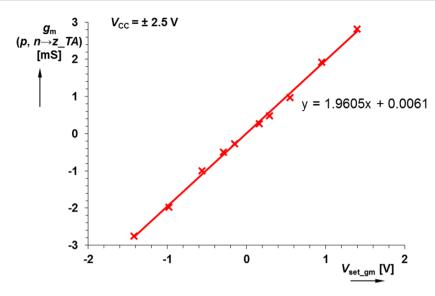

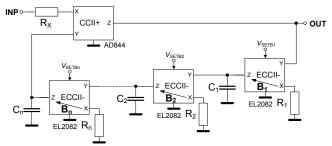

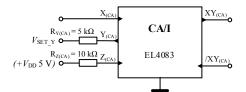

The second key insight of this dissertation is realization of reconfigurable impedance converter in Chapter D: Reconfigurable Impedance Converter for Synthesis of Integer and Fractional-Order Synthetic Elements, introduces an innovative approach to designing a clear and practical perspective on a circuit design utilizing electronically controllable current conveyors (ECCII), wide-band operational transconductance amplifiers (OTA), and differential difference amplifiers implemented as voltage buffers, alongside four-quadrant current-mode multiplier Chapter D.

Following traditional integer-order mathematical models often fall short in accurately describing the behavior of complex systems. The introduction of the fractional calculus into these models introduces a level of sophistication and accuracy previously unattainable, allowing for a more tunable utilization. Such a publication could be seen in Chapter E: Electronically Reconfigurable and Tunable Fractional-Order Filter Using Resonator Concept and Feedforward Path for Low-Frequency Tone Signalization. The reader is introduced to a comprehensive comparison of filter principles featuring transfer response reconfiguration capabilities within this work. Highlighting the contributions of this research, a novel solution for a special fractional-order filter is proposed. This includes illustrations of examples

demonstrating ideal system behavior alongside with results from the practical testing, allowing for a direct comparison. The detailed analysis not only showcases the theoretical design but also validates the proposed model through empirical and experimental evidence. Presented discussions have highlighted not only the theoretical advancements in the field but also the practical implementations and the potential for any future innovations Chapter E.

#### 4.1 Future Research Possibilities

The exploration of fractional calculus within this thesis opens a multitude of avenues for future research, particularly in enhancing the design and application of advanced circuit elements. Building on the foundational work presented, further investigation could delve into optimizing the ECCII, OTA, and differential difference amplifier (DDA) configurations for even more possibilities of reconfigurability with simple DC control as well as broader bandwidths and higher efficiency. Additionally, the integration of all above mentioned structures (CPEs, immittances, fractional-order resonators, etc.) on CMOS integrated chip technology in novel fractional-order systems to unlock new capabilities in signal processing, control systems, minimalization of parasitic effects in real behavior and beyond. Experimental verification of these advanced designs remains a critical step, offering valuable insights into their practical applications and limitations. It would be advisable to expand the frequency spectrum usability of CPE elements to the widest possible band (GHz). Moreover, the development of comprehensive models that bridge theoretical predictions with real-world performance will be crucial in advancing the field. As computational resources and algorithms continue to evolve, so there will be the potential for simulating increasingly complex systems, enabling groundbreaking innovations in fractional calculus applications.

#### 4.2 Main Body of the Thesis

Following the main body of the dissertation (excluding the bibliography) the subsequent section titled "Publications and Research" along with "A Publication Summary Related to Objectives of Work" compiles all publications related to the author's Objectives of Work. The following chapter "Timeline and Summary of Other Publications with an Author's Contribution" consists of other papers that are not primarily connected to Objectives of Work (papers are mostly second authorship). This segment offers a clear and organized timeline of research outputs, such as journal articles, conference papers, and main or second authorship. Each entry is accompanied by symbolic representations to easily distinguish the type of publication and authorship status.

Furthermore, this part methodically lists all publications directly related to Objectives of Work from Chapter A to Chapter E for the first part of Publication and Research. And Chapter F to Chapter H for the second part. Chapters F to H do not directly solve any objectives related to the dissertation but they are the main part of the author's study (second authorship) and thus significantly adding to the author's research growth. All papers detail instances in the raw format as they appeared in their respective publications. Preceding each article with a "Bibliographic citation", "Author's Contribution" to clarify the extent of involvement.

Additionally, a "Copyright Notice" is included for each publication, ensuring compliance with legal requirements and acknowledging copyright holders.

#### **Bibliography**

- [1] Leibniz, G.; Gerhardt, C.; Pertz, G. "Mathematische Schriften: aus den Handschriften der Königlichen Bibliothek zu Hannover. Briefwechsel zwischen Leibniz, Wallis, Varignon, Guido Grandi, Zendrini, Hermann und Freiherrn von Tschirnhaus," Druck und Verlag von H. W. Schmidt, Halle, Germany, 1859, Vol. 1.

- [2] Liouville, J. "Mémoire Sur quelques Questions de Géometrie et de Mécanique, et sur un nouveau genre de Calcul pour résoudre ces Questions," J. L'École Polytech., 1832, 13, pp. 1–69.

- [3] Riemann, B. "Versuch einer allgemeinen Auffassung der Integration und Differentiation," in Gesammelte Mathematische Werke, Dedekind, R., Weber, H. (Eds.), Druck und Verlag, Leipzig, Germany, 1876.

- [4] Butzer, P.L.; Nessel, R.J. Fourier Analysis and Application, Vol. I: One-Dimensional Theory, Birkhäuser Verlag, Basel, 1971.

- [5] Campos, L.M.B.C. "On a Concept of Derivative of Complex Order with Applications to Special Functions," IMA J. Appl. Math., 1984, 33, pp. 109–133.

- [6] Laurent, H. "Sur le calcul des dérivées à indices quelconques," Nouv. Ann. Mathématiques J. Des Candidats Aux Écoles Polytech. Norm., 1884, 3, pp. 240–252.

- [7] Borisova, T. I.; Ershler, B. V. "Determination of potentials of zero charge from double layer measurements," Zh. Fiz. Khim., 1950, Vol. 24, pp. 337–344.

- [8] Domansky, O.; Sotner, R.; Langhammer, L. "Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors," Circuits Syst Signal Process, 2019, 38, pp. 1520–1546, doi: https://doi.org/10.1007/s00034-018-0944-z.

- [9] Domansky, O.; Sotner, R.; Langhammer, L.; Polak, L. "Electronically Reconfigurable and Tunable Fractional-Order Filter Using Resonator Concept and Feedforward Path for Low-Frequency Tone Signalization," IEEE Access, 2021, vol. 9, pp. 138026-138041, doi: 10.1109/ACCESS.2021.3118084.

- [10] Domansky, O.; Sotner, R.; Petrzela, J.; Langhammer, L.; Dostal, T. "Higher order differentiator block for synthesis of controllable frequency dependent elements," 2017 27th International Conference Radioelektronika (RADIOELEKTRONIKA), 2017, pp. 1-5, doi: 10.1109/RADIOELEK.2017.7937587.

- [11] Valsa, J.; Vlach, J. "RC models of a constant phase element," International Journal of Circuit Theory and Applications, 2013, Vol. 41, No. 1, pp. 59–67.

- [12] Lasia, A. "The origin of the constant phase element," The Journal of Physical Chemistry Letters, 2022, Vol. 13, No. 2, pp. 580-589, https://doi.org/10.1021/acs.jpclett.1c03782.

- [13] Morrison, R. "RC Constant-Argument Driving-Point Admittances," in IRE Transactions on Circuit Theory, 1959, Vol. 6, No. 3, pp. 310-317, doi: 10.1109/TCT.1959.1086554

- [14] Krishna, M.; Das, S.; Biswas, K.; Goswami, B. "Fabrication of a fractional order capacitor with desired specifications: a study on process identification and characterization," IEEE Transactions on Electron Devices, 2011, Vol. 58, No. 11, pp. 4067–4073.

- [15] Adhikary, A.; Khanra, M.; Sen, S.; Biswas, K. "Realization of carbon nanotube based electrochemical fractor," Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), 2015, pp. 2329–2332.

- [16] Yun, C.; Hwang, S. "Analysis of the charging current in cyclic voltammetry and supercapacitor's galvanostatic charging profile based on a constant-phase element," ACS Omega, 2020, Vol. 6, No. 1, pp. 367-373, https://doi.org/10.1021/acsomega.0c04702.

- [17] Kittel, J.; Celati, N.; Keddam, M.; Takenouti, H. "New methods for the study of organic coatings by EIS: new insights into attached and free films," Progress in Organic Coatings, 2001, Vol. 41, Nos. 1–3, pp. 93–98.

- [18] Sylvain, A.; Marco, M.; Orazem, M.E.; Pebere, N.; Tribollet, B.; Vivier, V. "Constant-phase-element behavior caused by inhomogeneous water uptake in anti-corrosion coatings," Electrochimica Acta,

- 2013, Vol. 87, pp. 693-700.

- [19] Yamahigashi, et al. "Modeling of Lithium-Ion Batteries with Constant Phase Element and Butler-Volmer's Equation," 2023 11th International Conference on Power Electronics and ECCE Asia (ICPE 2023 ECCE Asia), Jeju Island, Republic of Korea, 2023, pp. 697-702, doi: 10.23919/ICPE2023-ECCEAsia54778.2023.10213775.

- [20] Yang, H. J.; Han, D.; Kim, J.; Kim, Y. H.; Bae, J. H. "Constant phase element affected by ion transport in nanoporous electrodes," Journal of Electroanalytical Chemistry, 2022, Vol. 922, 116766.

- [21] Ushakov, P.; Shadrin, A.; Kubanek, A.; Koton, J. "Passive fractional-order components based on resistive capacitive circuits with distributed parameters," Proceedings of the 39th International Conference on Telecommunications and Signal Processing (TSP), 2016, pp. 638–462.

- [22] Valsa, J.; Dvorak, P.; Friedl, M. "Network model of the CPE," Radioengineering, 2011, Vol. 20, No. 3, pp. 619–626.

- [23] Petrzela, J. "A note on fractional-order two-terminal devices in filtering applications," Proceedings of the 24th International Conference Radioelektronika, 2014, pp. 1–4.

- [24] Sun, Y.; Fidler, J. K. "Current-mode OTA-C realisation of arbitrary filter characteristics," Electronics Letters, 1996, Vol. 32, No. 13, pp. 1181-1182, doi: 10.1049/el:19960807.

- [25] Dostal, T. "Filters with multi-loop feedback structure in current mode," Radioengineering, 2003, Vol. 12, No. 3, p. 6.

- [26] Sotner, R.; Petrzela, J.; Jerabek, J.; Dostal, T. "Reconnection-less OTA based biquad filter with electronically reconfigurable transfers," Elektronika Ir Elektrotechnika, 2015, Vol. 21, No. 3, pp. 33-37, doi: 10.5755/j01.eee.21.3.10205.

- [27] Domansky, O.; Sotner, R.; Langhammer, L. "Reconfigurable Impedance Converter for Synthesis of Integer and Fractional-Order Synthetic Elements," 2018 41st International Conference on Telecommunications and Signal Processing (TSP), Athens, Greece, 2018, pp. 1-5, doi: 10.1109/TSP.2018.8441376.

- [28] Sotner, R.; Domansky, O.; Jerabek, J.; Herencsar, N.; Petrzela, J.; Andriukaitis, D. "Integer and Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations," Applied Sciences Basel, 2020, vol. 10, no. 1, pp. 1-25, ISSN: 2076-3417.

- [29] Petrzela, J.; Domansky, O. "Simple Chaotic Oscillator with Wideband Passive Fractional-Order Inductor," Proceedings of the 42nd International Conference on Telecommunications and Signal Processing (TSP), 2019, pp. 327-331, ISBN: 978-1-7281-1864-2.

- [30] Elwakil, A.S. "Fractional-order circuits and systems: An emerging interdisciplinary research area," IEEE Circuits Syst. Mag., 2010, Vol. 10, No. 4, pp. 40-50, doi: 10.1109/MCAS.2010.938637.

- [31] Langhammer, L.; Dvorak, J.; Sotner, R.; Jerabek, J.; Bertsias, P. "Reconnection-less reconfigurable low-pass filtering topology suitable for higher-order fractional\_order design," J. Adv. Res., 2020, Vol. 25, No. 9, pp. 257-274, doi: 10.1016/j.jare.2020.06.022.

- [32] Naglich, E.J.; Lee, J.; Peroulis, D.; Chappell, W.J. "Switchless tunable bandstop-to-all-pass reconfigurable filter," IEEE Trans. Microw. Theory Techn., 2012, Vol. 60, No. 5, pp. 1258\_1265, doi: 10.1109/TMTT.2012.2188723.

- [33] Sotner, R.; Polak, L.; Jerabek, J.; Jaikla, W. "Arbitrarily Tunable Phase Shift in Low-Frequency Multiphase Oscillator," IEEE Transactions on Instrumentation and Measurement, 2023, Vol. 72, pp. 1-11, Art no. 2004711, doi: 10.1109/TIM.2023.3280514.

- [34] Sotner, R.; Jerabek, J.; Polak, L.; Langhammer, L.; Stolarova, H.; Petrzela, J.; Andriukaitis, D.; Valinevicius, A. "On the performance of electronically tunable fractional-order oscillator using grounded resonator concept," AEU-Int. J. Electron. Commun., 2021, Vol. 129, Feb., Art. no. 153540, doi: 10.1016/j.aeue.2020.153540.

- [35] Sotner R.; Jerabek J.; Kartci A.; Domansky O.; Herencsar N.; Kledrowetz W.; Baykant Alagoz B.; Yeroglu C. "Electronically reconfigurable two-path fractional-order PI/D controller employing constant phase blocks based on bilinear segments using CMOS modified current differencing unit," Microelectronics Journal, 2019, Vol. 86, pp. 114-129, ISSN: 1879-2391, doi: 10.1016/j.mejo.2019.03.003.

[36] Sotner, R.; Jerabek, J.; Petrzela, J.; Domansky, O.; Tsirimokou, G.; Psychalinos, C. "Synthesis and design of constant phase elements based on the multiplication of electronically controllable bilinear immittances in practice," AEU - International Journal of Electronics and Communications, 2017, Vol. 78, No. 8, pp. 98-113, ISSN: 1434-8411.

## **PUBLICATIONS AND RESEARCH**

A Publication Summary Related to Objectives of Work

Timeline and Summary of Other Publications with an

Author's Contribution

## A Publication Summary Related to Objectives of Work

Objective 1

Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors

(impact factor: 2.715, Scopus, 2023)

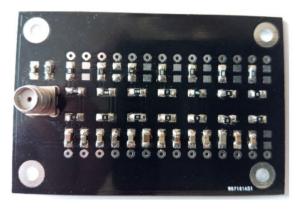

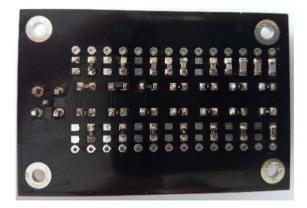

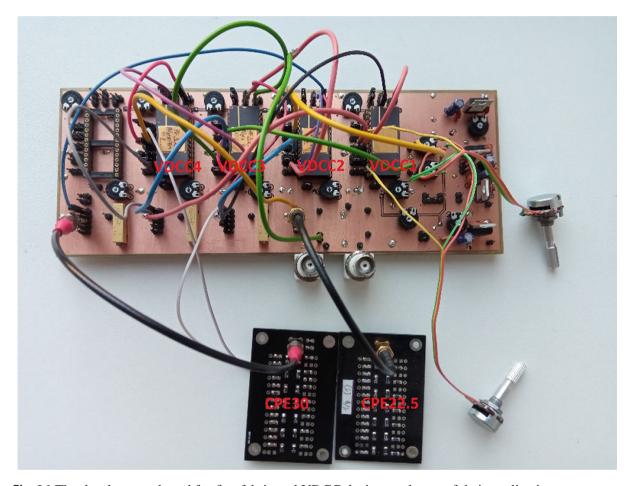

This paper brings a practical and straightforward view on the design of circuit elements described by fractional-order dynamics known as the constant phase element and their implementation in a novel structure of a PI $\alpha$ D $\beta$  (or PI $\lambda$ D $\mu$  in some literature) regulator based on fabricated CMOS voltage differencing current conveyors. Step-by-step design of the CPE as well as the PI $\alpha$ D $\beta$  regulator is supported by experiments with active devices fabricated using the C07 I2T100 0.7  $\mu$ m CMOS process (ON Semiconductor). Presented in the journal Circuits, Systems, and Signal Processing (CSSP). Objective 1

Authors: Domanský, O.; Šotner, R.; Langhammer, L.; Jeřábek, J.; Psychalinos, C.; Tsirimokou, G.

Objective 1

Integer-and Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations

(impact factor: 3.143, Scopus, 2023)

This work targets the design and analysis of specific types of transfer functions obtained by the summing operation of integer-order and fractional-order two-port responses. Various operations provided by fractional-order. However, this topic needs to be further studied, and the topologies need to be analyzed in order to extend the state of the art. The studied topology utilizes the passive solution of a constant-phase element. This work was published in journal Applied Sciences by MDPI. Objective 1

Authors: Šotner, R.; Domanský, O.; Jeřábek, J.; Herencsár, N.; Petržela, J.; Andriukaitis, D.

Objective 1

Higher Order Differentiator Block for Synthesis of Controllable Frequency Dependent Elements

This paper presents a structure of generally nth-order differentiator transfer block serving for purpose of integer order or fractional order immittance synthesis. Presentation was commenced during the proceedings at 27th International Conference Radioelektronika 2017. Objective 1

Authors: Domanský, O.; Šotner, R.; Petržela, J.; Langhammer, L.; Dostál, T.

Objective 2 (

Reconfigurable Impedance Converter for Synthesis of Integer and Fractional-Order Synthetic Elements

This paper introduces a practical and straightforward view on the design of a circuit based on electronically controllable current conveyors, wide-band operational transconductance amplifier, voltage buffer and four quadrant current-mode multiplier. All these elements are implemented for the possibility of multiple electronical tunability of the resulting specific reconfigurable impedance converter of the integer-order as well as the fractional-order. Novelty of this paper was presented at Proceedings of IEEE 2018 41st International Conference on Telecommunications and Signal Processing (TSP 2018).

Objective 2 Authors: Domanský, O.; Šotner, R.; Langhammer, L.

Objective 3

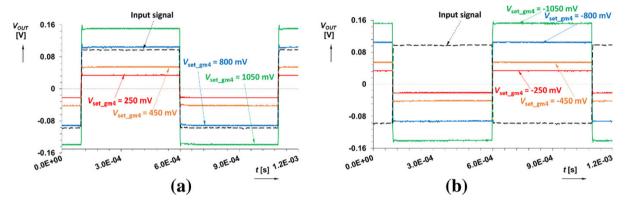

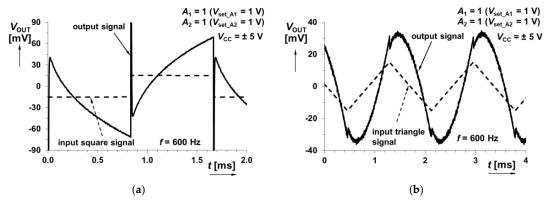

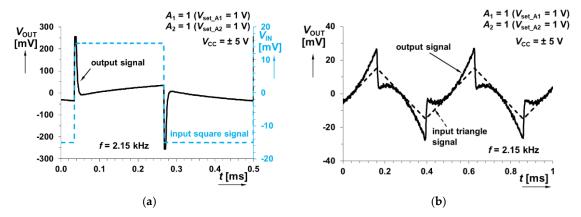

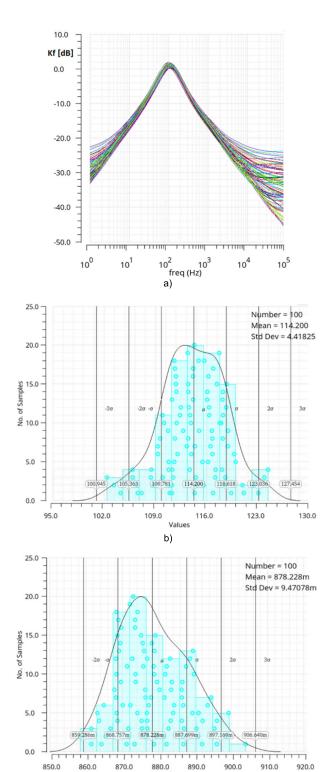

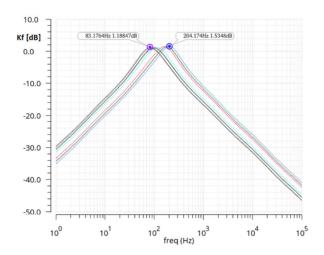

Electronically Reconfigurable and Tunable Fractional-Order Filter Using Resonator Concept and Feedforward Path for Low-Frequency Tone Signalization

(impact factor: 4.255, Scopus, 2023)

The last work of my study (as well as the paper with the biggest impact factor of this dissertation) is a novel electronically reconfigurable fractional-order filter allowing independent electronic frequency tuning and switchless change of the transfer response by a single parameter between a standard band-pass, inverting all-pass response and a special type band-reject response. The proposed fractional-order filter tunability yields one-decade range approximately between 10 Hz and 100 Hz. Cadence simulations as well as experimental tests using integrated cells of special multipliers fabricated in ON Semiconductor 0.35 µm I3T25 CMOS. This work was published in IEEE Access journal with the open access version. Objective 3

Authors: Domanský, O.; Šotner, R.; Langhammer, L.; Polák, L.

Legend:

- journal article;

- conference paper

- main authorship; ( )

- second author

## A Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors

Objective 1; (impact factor (2022): 2.311)

#### **Outline**

- A.1 Introduction

- A.1.1 Constant Phase Element (CPE)

- A.1.2 State of the Art of Fractional-Order Passive Elements and  $PI^{\alpha}D^{\beta}$  Regulator Designs

- A.2 Practical Design of Passive CPE

- A.2.1 Available Passive Structures Suitable for CPE Synthesis

- A.2.2 Design Example of Passive CPE

- A.3 Special Solution of  $PI^{\alpha}D^{\beta}s$  Based on VDCC Elements

- A.3.1 Description of VDCC Element

- A.3.2 Designed  $PI^{\alpha}D^{\beta}$  Controller

- A.3.3 Measurement Results

- A.4 Conclusion

Acknowledgements

References

### **Bibliographic Information**

O. Domansky, R. Sotner, L. Langhammer, "Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors," *Circuits Syst Signal Process* 38, 2019, 38, pp. 1520–1546, doi: https://doi.org/10.1007/s00034-018-0944-z.

#### **Author's Contribution**

Further research of the original master's thesis of the author. The author proposed the concept, co-designed the methodology, performed realization, analysis, validation, and data visualization. Also worked on finalization and the whole manuscript i.e. reviewing,

editing, etc. The Objective 1 of this paper was fulfilled by the novel topology of PID using voltage differencing current conveyors (VDCC) and two CPE devices. The electronic adjustment allows simple time constant control by DC voltages and currents. It is available for implementing special CMOS active devices and circuit topology using only grounded passive elements (including CPEs). This fact is beneficial for possible integration of the complete device.

Author's contribution: 48 % (the main author).

#### **Copyright Notice**

All copyrights, proprietary rights and other third-party rights which are accessed via springernature.com remain the sole property of their respective holders and are protected accordingly. Unless otherwise stipulated in an individual case, you only have the statutory right to make a small number of copies of parts of the content, provided that such copies may only be made and used for personal purposes and it must be ensured that all copyright and other proprietary notices and their content are retained. Reproduced with permission from Springer Nature. © 2023 Springer Nature.

(https://link.springer.com/article/10.1007/s00034-018-0944-z).

## Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors

Ondrej Domansky<sup>1</sup> · Roman Sotner<sup>1</sup> · Lukas Langhammer<sup>1</sup> · Jan Jerabek<sup>2</sup> · Costas Psychalinos<sup>3</sup> · Georgia Tsirimokou<sup>3</sup>

Received: 5 March 2018 / Revised: 12 September 2018 / Accepted: 14 September 2018 /

Published online: 3 October 2018

© Springer Science+Business Media, LLC, part of Springer Nature 2018

#### **Abstract**

This paper brings a practical and straightforward view on the design of circuit elements described by fractional-order dynamics known as the constant phase element (CPE) and their implementation in a novel structure of a  $PI^{\alpha}D^{\beta}$  (or  $PI^{\lambda}D^{\mu}$  in some literature) regulator based on fabricated CMOS voltage differencing current conveyors. Comparison of presented topology with known solutions indicates significant improvements regarding overall simplification, simpler electronic controllability of time constants, and having all passive elements in grounded form. Step-by-step design of the CPE as well as the  $PI^{\alpha}D^{\beta}$  regulator is supported by experiments with active devices fabricated using the C07 I2T100 0.7  $\mu$ m CMOS process (ON Semiconductor). Laboratory tests in frequency and time domain confirm the correct operation of the designed application and the accuracy of the derived results in comparison with the theoretical expectations.

**Keywords** Constant phase element (CPE) · Differentiator · Fractional-order circuit · Integrator · Proportional branch · Proportional integrational and differential controller (PID) · Voltage differencing current conveyor (VDCC)

#### 1 Introduction

In recent years, fractional elements [43] have attracted increasing attention of researchers because of their interesting behavior in both the time and frequency domain. Fractional calculus has been well known in the mathematical domain for decades, but its potential in electronic circuits with lumped parameters has not been fully explored in detail. Practical implementation of these elements (such as two ter-

Ondrej Domansky domansky@phd.feec.vutbr.cz

Extended author information available on the last page of the article

minals or one port) in electronic systems delivers new applications in the field of signal filtering and generation of signals (both harmonic and non-harmonic).

#### 1.1 Constant Phase Element (CPE)

A fractional-order element, known also as constant phase element (CPE), is characterized by a constant phase shift, in the interval between  $0^{\circ}$  and  $\pm\,90^{\circ}$ , between response (voltage or current) and excitation (voltage or current) in the entire frequency band (ideally from zero to infinity) [43]. The main difficulty for practical application of CPEs is their commercial unavailability. Several solutions of CPEs based on electrochemical [1, 2, 7, 18, 21] organic material [20, 40], polymer composites [11], and thick film layers of resistive, dielectric and insulating materials on silicon [42] have been introduced in recent years. Therefore, these devices are commonly approximated by standard electronic components in passive [24, 31, 43] or active (see for example [37, 41] and references cited therein) implementation. Various active elements [6] can be used in active solutions if limited frequency bandwidth is sufficient.

The simplest ways of CPE imitation are based on suitably arranged infinite series of linear resistors and capacitors in serial/parallel combinations [43]. In practice, there are several methods leading to the design of specific approximations. These so-called ladder structures are very beneficial for purposes of approximation of fractional elements. Their utilization can lead to the creation of two-terminal devices having symbolical mathematical character of immittance function of the Laplace operator  $s^{\pm \alpha}$ , where  $0 < |\alpha| < 1$ . There are several special cases, e.g., when  $\alpha = 0.5$ , where CPE behaves as a so-called half capacitor [26, 37]. Note that in order to allow real implementation, all these known approximations work with limited and finite number of resistances and capacitances in resulting ladder structures. Therefore, the bandwidth of approximation is also restricted. Also, the phase response fluctuates around a mean value with a certain phase ripple being acceptable for particular applications.

The most important guidelines for initial studies in this area, from a mathematical point of view, have been presented in [22, 26, 32, 33]. In the last few years, many papers have significantly contributed to the improvement in this field [31]. Later, methods for widening the frequency range of constant phase shift have been introduced (see for example, [43, 44]). The work in [43] is based on the geometric series of elements, setting initial parameters like phase change, phase ripple, and number of segments. Note that this method is very important for designing the CPEs in this paper. However, this approach is valid up to several MHz. Therefore, CPEs became popular and their behavior and parameters are the main focus of recent studies; for example, influence of roughness [2], capacitance [9] or for filtering [25, 34, 36] of signals with increasing [27] or decreasing [26] phase shift.

## 1.2 State of the Art of Fractional-Order Passive Elements and $PI^{\alpha}D^{\beta}$ Regulator Designs

The contribution of this paper is the employment of already designed CPEs into proportional, integrational and differential controllers (PIDs). The PIDs serve for regulating

the input signal into desirable controlled output. Initial studies of this topic and resulting advantages/features were introduced in [4, 32]. Those papers are mainly theoretical and use general operational amplifier (opamp) structures with presented results concerning stability, gain and phase responses. Integer-order PID regulators are significant in the field of applications in automation and regulation theory [4] and practice [5]. However, the fractional-order solutions [8, 12, 15, 16, 30, 43] can be even more beneficial in these applications. In general, the main difference between integer-order and fractional-order PID is that the fractional-order solution offers two extra degrees of freedom, making the tuning of such controllers easier than that of the conventional (i.e., integer order) counterparts. The first fractional  $PI^{\alpha}D^{\beta}$  (also known as  $PI^{\lambda}D^{\mu}$ ) controller was mentioned in [30] where two approaches of fractional calculus are described (the Lenikov-Riemann–Liouville definition and the Caputo definition).

Table 1 shows a list of relevant previously reported PID solutions and provides a simple comparison of their key features. Based on Table 1, we can see that PID concepts suffer from several drawbacks: (a) high number of active elements [13, 14, 23, 35], (b) high number of passive elements [19, 23, 43], (c) impossible electronic tunability [3, 13, 19, 43], (d) floating passive elements [19, 23, 28, 43], and (e) lack of simple (electronical) change of polarity of transfer response (i.e., PID branch transfer) [3, 13, 14, 19, 28, 29, 35, 43]. We are comparing both integer-order and fractional-order solutions in Table 1 because our solution can be easily implemented in both these cases as well as integer-order PID solutions in Table 1 can be easily modified to fractional-order PID regulators when standard capacitors are replaced by fractional-order CPEs and vice versa. Therefore, important novelty of our contribution consists in circuit topology of PID regulator and consequent advantages.

The last noted issue (e) is very important and by fixing it, we may bring some new feature(s) in the area of PID regulators. Direct electronic modification of polarity of integrating or differentiating branch does not require changing PID topology. It is actually a very interesting feature increasing the universality of the proposed PID topology in real applications in regulating/controlling systems for instance. The proposed solution presented in this paper solves each of the discussed issues of previously reported circuits simultaneously. To the best of the author's knowledge, these features have not been reported yet. We can claim that the main novelty of the proposed design consists in its simplicity of topology (as compared with current state of the art) and the possibility of electronic control of parameters of the PID regulator due to the control of the transconductance or the resistance of current input terminal of each VDCC element. Those parameters serve for changing the polarities of transfer in each branch and tuning of time constants as well as changing the gain of a proportional branch. These features are not available simultaneously in previous designs presented in the literature.

The paper is organized as follows: Sect. 2 deals with defining the ideal CPE element and the necessary steps leading to selecting appropriate values of passive components of real CPE created by a selected RC ladder structure. This part explains in detail the calculation, design procedure, and final optimization in order to use a combination of resistors and capacitors of the common fabrication series E24. This Section also shows the effect of tolerances of RC elements on the Monte Carlo analysis. Section 3 continues with the designed CPE and its application into a new solution of a  $PI^{\alpha}D^{\beta}$

Table 1 Comparison of PID conceptions based of different active elements

|           | No. of passive elements | No. of active elements | Type of active elements  | Technology                     | All resistors<br>grounded | All capacitors grounded | Type of control                         |

|-----------|-------------------------|------------------------|--------------------------|--------------------------------|---------------------------|-------------------------|-----------------------------------------|

| [43]      | 8                       | 4                      | Opamp                    | Bipolar<br>(commercial IC)     | No                        | No                      | Passive only (value of C)               |

| [43]      | ∞                       | 4                      | Opamp                    | Bipolar<br>(commercial IC)     | No                        | No                      | passive only (value of R)               |

| [14]      | 8                       | ∞                      | OTA                      | CMOS (AMS 0.8 µm)              | Yes                       | Yes                     | 8m                                      |

| [29]      | 3                       | 3-4                    | DVCC, OTA                | N/A                            | Yes                       | Yes                     | $R_{ m X}, g_{ m m}$                    |

| [28]      | 3                       | 4                      | OTA                      | N/A                            | Yes                       | No                      | 8m                                      |

| [35]      | 2                       | 9                      | OTA                      | CMOS (TSMC 0.18 µm)            | N/A                       | Yes                     | 8m                                      |

| [3]       | ς.                      | 2                      | CCII                     | CMOS (TSMC 0.35 µm)            | Yes                       | Yes                     | Passive only (value of R and C)         |

| [13]      | 4                       | ∞                      | OTA                      | Bipolar (AT&T)                 | Yes                       | Yes                     | passive value of R, C and $g_{\rm m}$   |

| [19]      | 10                      | 4                      | CDBA                     | CMOS (N/A)                     | No                        | No                      | Passive only (value of R and C)         |

| [23]      | 63 (60)                 | 11 (12)                | Opamp +FPAA <sup>d</sup> | Bipolar<br>(commercial<br>N/A) | No                        | No                      | CAB (passive R,<br>C)/FPAA <sup>d</sup> |

| [10]      | 10                      | 26                     | OTA                      | CMOS (AMS 0.35 µm)             | N/A                       | Yes                     | 8m                                      |

|           | Proposed                |                        |                          |                                |                           |                         |                                         |

| This work | 4                       | 4                      | VDCC                     | CMOS ON (0.7 µm)               | Yes                       | Yes                     | 8m                                      |

|           |                         |                        |                          |                                |                           |                         |                                         |

Table 1 continued

|           | Electronic control of branch polarity | Type of verification | No. of approx. decades (bandwidth) | Fractional order | Power<br>consumption [mW] | Area (large—com-<br>mercial<br>opamps/small-fully<br>integrated) | Cost (high —integrated circuit/low —opamps) |

|-----------|---------------------------------------|----------------------|------------------------------------|------------------|---------------------------|------------------------------------------------------------------|---------------------------------------------|

| [43]      | No                                    | Simulated            | $N/A^a$                            | No               | N/A                       | Large                                                            | Low                                         |

| [43]      | No                                    | Simulated            | $N/A^a$                            | Yes              | N/A                       | Large                                                            | Low                                         |

| [14]      | No                                    | Simulated            | N/A                                | No               | N/A                       | Large                                                            | Low                                         |

| [59]      | No                                    | Simulated            | 7b                                 | Yes              | N/A                       | Large                                                            | Low                                         |

| [28]      | No                                    | Simulated            | 3                                  | Yes              | N/A                       | Large                                                            | Low                                         |

| [35]      | No                                    | Simulated            | 29                                 | No               | 1.44                      | N/A                                                              | N/A                                         |

| [3]       | No                                    | Simulated            | N/A                                | No               | N/A                       | Large                                                            | Low                                         |

| [13]      | No                                    | Simulated            | N/A                                | No               | N/A                       | Large                                                            | Low                                         |

| [19]      | No                                    | Simulated            | N/A                                | No               | N/A                       | Large                                                            | Low                                         |

| [23]      | No                                    | Simulated/measured   | 1                                  | Yes              | N/A                       | Large                                                            | Low                                         |

| [10]      | No                                    | Simulated            | 4                                  | Yes              | N/A                       | Small                                                            | High                                        |

|           | Proposed                              |                      |                                    |                  |                           |                                                                  |                                             |

| This work | Yes                                   | Simulated/measured   | 4                                  | Yes              | 120                       | Large                                                            | High                                        |

veyor; CCII, current conveyor (second generation); CDBA, current differencing buffered amplifier; CMOS, complementary metal-oxide-semiconductor; CAB, configurable Opamp (opamp), operational amplifier; OTA, operational transconductance amplifier; DVCC, differential voltage current conveyor; VDCC, voltage differencing current conanalog blocks; FPAA, field-programmable analog array

<sup>&</sup>lt;sup>a</sup>Study focuses on theory of general design of CPE

<sup>&</sup>lt;sup>b</sup>CPE used in [29] was theoretically designed for operation up to 1 GHz but real features of elements (dispersion of small values of capacity) limit usability up to several MHz in practice

<sup>&</sup>lt;sup>c</sup>Magnitude response designed for range 40 Hz-40 MHz (6 decades) but higher corner significantly deviates from ideal trace above 10 MHz

<sup>&</sup>lt;sup>d</sup>Configurable analog blocks (CAB) based on opamps and field-programmable analog array (FPAA) used together

regulator based on voltage differencing current conveyor (VDCC) active elements. Various experimental benchmarks are also presented. At the end of Sect. 4, the main benefits of the experimentally tested PID are summarized as well as the overall results of the proposed structure.

#### 2 Practical Design of Passive CPE

Dynamics of the non-integer order passive two-terminal element can be characterized with its impedance and admittance. Such an element can be described by the Laplace transformation as admittance:

$$Y_{\alpha}(s) = \frac{I_{\text{in}}(s)}{V_{\text{in}}(s)} = Y_o \cdot s^{\alpha}, \tag{1}$$

where the order of CPE ( $\alpha$ ) can be within the range of  $-1 < \alpha < 1$ . The substitution  $s = j\omega$  results in complex frequency response of CPE:

$$\hat{Y}_{\alpha}(j\omega) = Y_o \cdot (j\omega)^{\alpha} = Y_o \cdot \omega^{\alpha} e^{j\varphi} = Y_o \cdot \omega^{\alpha} (\cos \varphi + j \cdot \sin \varphi), \tag{2}$$

where  $\varphi$  represents the phase shift given by the formula:  $\varphi = \alpha \frac{\pi}{2}$  [rad] or  $\varphi = 90\alpha$  [degree or °]. The exponent  $\alpha$  characterizes the final admittance, and it corresponds to a fractional capacitor  $(0 < \alpha < 1)$  or to a fractional inductor  $(-1 < \alpha < 0)$ . In the case that  $\alpha = 0$ , a real resistance is obtained. The Laplace transform can be used in order to convert this function into a rational function with the following pole-zero form:

$$Y(s) = \frac{\sum_{i=1}^{m-1} A_i s^i}{\sum_{k=1}^{m} B_k s^k} = Y_o \frac{\prod_{i=1}^{m-1} (s - \omega_{zm})}{\prod_{k=1}^{m} (s - \omega_{pm})}.$$

(3)

The roots and coefficients of (3) determine the phase change  $\varphi$  and the ripple  $\triangle \varphi$  as will be explained in the following section. Symbols  $\omega_{zm}$  and  $\omega_{pm}$  represent the zeros and poles. When the number of sections (i.e., the number of serial RC, RL branches in parallel—between two nodes or serial chain of parallel RC, RL sections) is infinite, phase ripple should be almost equal to zero in the working bandwidth and magnitude response of admittance plot should be linearly increasing/decreasing with  $20 \cdot \alpha$  dB per decade.

#### 2.1 Available Passive Structures Suitable for CPE Synthesis