# VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ BRNO UNIVERSITY OF TECHNOLOGY

# FAKULTA INFORMAČNÍCH TECHNOLOGIÍ ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

FACULTY OF INFORMATION TECHNOLOGY DEPARTMENT OF COMPUTER SYSTEMS

# EVOLUČNÍ PŘÍSTUP K SYNTÉZE A OPTIMALIZACI BĚŽNÝCH A POLYMORFNÍCH OBVODŮ

EVOLUTIONARY APPROACH TO SYNTHESIS AND OPTIMIZATION OF ORDINARY AND POLYMORPHIC CIRCUITS

DISERTAČNÍ PRÁCE

PHD THESIS

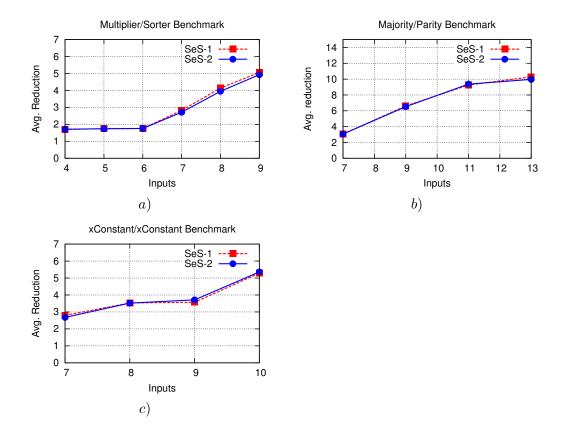

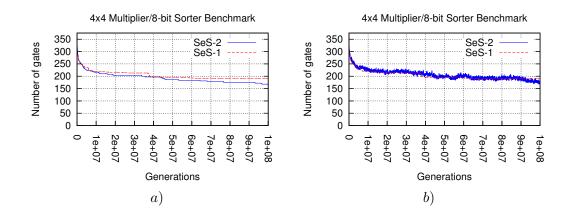

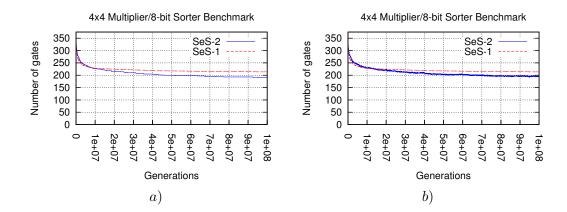

AUTOR PRÁCE

Ing. ZBYŠEK GAJDA

AUTHOR

VEDOUCÍ PRÁCE

doc. Ing. LUKÁŠ SEKANINA, Ph.D.

SUPERVISOR

**BRNO 2011**

## Abstract

This thesis deals with the evolutionary design and optimization of ordinary and polymorphic circuits. New extensions of Cartesian Genetic Programming (CGP) that allow reducing of the computational time and obtaining more compact circuits are proposed and evaluated. Second part of the thesis is focused on new methods for synthesis of polymorphic circuits. Proposed methods, based on polymorphic binary decision diagrams and polymorphic multiplexing, extend the ordinary circuit representations with the aim of including polymorphic gates. In order to reduce the number of gates in circuits synthesized using proposed methods, an evolutionary optimization based on CGP is implemented and evaluated. The implementations of polymorphic circuits optimized by CGP represent the best known solutions if the number of gates is considered as the target criterion.

# Keywords

Polymorphic gate, polymorphic circuit, digital circuit design, evolutionary design, evolutionary optimization, Cartesian Genetic Programming.

# **Bibliographic Citation**

Zbyšek Gajda: Evolutionary Approach to Synthesis and Optimization of Ordinary and Polymorphic Circuits, PhD thesis, Brno, FIT BUT, 2011

## Abstrakt

Tato disertační práce se zabývá evolučním návrhem a optimalizací jak běžných, tak polymorfních digitálních obvodů. V práci jsou uvedena a vyhodnocena nová rozšíření kartézského genetického programování (Cartesian Genetic Programming, CGP), která umožňují zkrácení výpočetního času a získávání kompaktnějších obvodů. Další část práce se zaměřuje na nové metody syntézy polymorfních obvodů. Uvedené metody založené na polymorfních binárních rozhodovacích diagramech a polymorfním multiplexovaní rozšiřují běžné reprezentace digitálních obvodů, a to s ohledem na začlenění polymorfních hradel. Z důvodu snížení počtu hradel v obvodech syntetizovaných uvedenými metodami je provedena evoluční optimalizace založená na CGP. Implementované polymorfní obvody, které jsou optimalizovány s využitím CGP, reprezentují nejlepší známá řešení, jestliže je jako cílové kritérium brán počet hradel obvodu.

## Klíčová slova

Polymorfní hradlo, polymorfní obvod, návrh digitálních obvodů, evoluční návrh, evoluční optimalizace, kartézské genetické programování.

# Citace

Zbyšek Gajda: Evolutionary Approach to Synthesis and Optimization of Ordinary and Polymorphic Circuits, disertační práce, Brno, FIT VUT v Brně, 2011

# Evolutionary Approach to Synthesis and Optimization of Ordinary and Polymorphic Circuits

### Prohlášení

Prohlašuji, že jsem tuto disertační práci vypracoval samostatně pod vedením doc. Lukáše Sekaniny.

Zbyšek Gajda 3. března 2011

## Poděkování

Na tomto místě bych rád poděkoval Lukáši Sekaninovi, který byl mým školitelem během doktorského studia. Velmi si cením jeho neutuchající podpory během výzkumu a jeho neocenitelné pomoci při psaní článků i této práce.

Dále děkuji zaměstnancům Ústavu počítačových systémů za skvělé pracovní podmínky a přátelské prostředí, jmenovitě vedoucímu ústavu, Zdeňku Kotáskovi, kolegům, Michalu Bidlovi, Jiřímu Jarošovi, Martinu Strakovi, Josefu Strnadelovi, Václavu Šimkovi, Jaroslavu Škarvadovi, Richardovi Růžičkovi, a asistentce ústavu, Marii Gaďorkové.

V neposlední řadě děkuji rodičům, Marii a Janu Gajdovým, a všem dobrým duším, které mi dodávaly sílu a přinášely inspiraci.

Výsledky této práce vznikly za podpory Grantové agentury České republiky a Ministerstva školství, mládeže a tělovýchovy v rámci projektů: Metody návrhu polymorfních číslicových obvodů, GAČR, GA102/06/0599, 2006-2008, Návrh a obvodová realizace zařízení pro automatické generování patentovatelných invencí, GAČR, GA102/07/0850, 2007-2009, Integrovaný přístup k výchově studentů DSP v oblasti paralelních a distribuovaných systémů, GAČR, GD102/05/H050, 2005-2008 a Výzkum informačních technologií z hlediska bezpečnosti, CEZ MŠMT, MSM0021630528, 2007-2013.

#### © Zbyšek Gajda, 2011.

Tato práce vznikla jako školní dílo na Vysokém učení technickém v Brně, Fakultě informačních technologií. Práce je chráněna autorským zákonem a její užití bez udělení oprávnění autorem je nezákonné, s výjimkou zákonem definovaných případů.

# Contents

| 1 | Introduction                                                      |                                             |    |  |  |  |  |  |

|---|-------------------------------------------------------------------|---------------------------------------------|----|--|--|--|--|--|

|   | 1.1                                                               | Thesis Organization                         | ļ  |  |  |  |  |  |

| 2 | Overview of Digital Circuit Design                                |                                             |    |  |  |  |  |  |

|   | 2.1                                                               | Digital Circuits – Principles               | 6  |  |  |  |  |  |

|   | 2.2                                                               | Standard Representations of Logic Functions | 7  |  |  |  |  |  |

|   | 2.3                                                               | Combinational-Circuit Synthesis             | 7  |  |  |  |  |  |

|   |                                                                   | 2.3.1 Two-level minimization methods        | 8  |  |  |  |  |  |

|   |                                                                   | 2.3.2 Multi-level representations           | Ć  |  |  |  |  |  |

|   |                                                                   | 2.3.3 Synthesis tools                       | 10 |  |  |  |  |  |

|   | 2.4                                                               | Application-Specific Circuits               | 11 |  |  |  |  |  |

|   |                                                                   | 2.4.1 Combinational multiplier              | 11 |  |  |  |  |  |

|   |                                                                   | 2.4.2 Binary sorters                        | 12 |  |  |  |  |  |

|   |                                                                   | 2.4.3 Even parity                           | 12 |  |  |  |  |  |

| 3 | Evolutionary Design of Digital Circuits and Evolvable Hardware 14 |                                             |    |  |  |  |  |  |

| J | 3.1                                                               | Evolutionary Algorithms                     | 14 |  |  |  |  |  |

|   | $\frac{3.1}{3.2}$                                                 | ·                                           |    |  |  |  |  |  |

|   | $\frac{3.2}{3.3}$                                                 | Cartesian Genetic Programming               | 18 |  |  |  |  |  |

|   | ა.ა                                                               | 3.3.1 Basic CGP                             | 18 |  |  |  |  |  |

|   |                                                                   | 3.3.2 Circuit evolution using CGP           | 19 |  |  |  |  |  |

|   | 3.4                                                               | Scalability Problem                         | 21 |  |  |  |  |  |

|   |                                                                   |                                             |    |  |  |  |  |  |

| 4 | •                                                                 | Polymorphic Electronics 2                   |    |  |  |  |  |  |

|   | 4.1                                                               | Polymorphic Gates                           | 23 |  |  |  |  |  |

|   | 4.2                                                               | Polymorphic Circuits                        | 24 |  |  |  |  |  |

|   |                                                                   | 4.2.1 REPOMO32 platform                     | 26 |  |  |  |  |  |

|   | 4.3                                                               | Applications of Polymorphic Electronics     | 26 |  |  |  |  |  |

|   |                                                                   | 4.3.1 Polymorphic FIR filter                | 27 |  |  |  |  |  |

|   |                                                                   | 4.3.2 Polymorphic controller                | 27 |  |  |  |  |  |

|   |                                                                   | 4.3.3 Self-checking adder                   | 27 |  |  |  |  |  |

| 5 | Goa                                                               | als                                         | 29 |  |  |  |  |  |

| 6 | Extensions of Standard Cartesian Genetic Programming 3            |                                             |    |  |  |  |  |  |

|   | 6.1                                                               | Design Phase and Optimization Phase         | 30 |  |  |  |  |  |

|   | 6.2                                                               | Modified Fitness Functions                  | 30 |  |  |  |  |  |

|   | 6.3                                                               |                                             | 39 |  |  |  |  |  |

|           | 6.4  | Short-Circuit Evaluation                                  | 33              |  |  |  |  |  |  |  |

|-----------|------|-----------------------------------------------------------|-----------------|--|--|--|--|--|--|--|

|           | 6.5  | Training-Set Reorganization                               | 33              |  |  |  |  |  |  |  |

| 7         | Evo  | Evolutionary Optimization of Circuit Designs              |                 |  |  |  |  |  |  |  |

|           | 7.1  | Benchmark Problems                                        | 35              |  |  |  |  |  |  |  |

|           |      | 7.1.1 Small binary multipliers                            | 36              |  |  |  |  |  |  |  |

|           |      |                                                           | 36              |  |  |  |  |  |  |  |

|           |      |                                                           | 36              |  |  |  |  |  |  |  |

|           | 7.2  | · · · · · · · · · · · · · · · · · · ·                     | 37              |  |  |  |  |  |  |  |

|           | 7.3  |                                                           | 37              |  |  |  |  |  |  |  |

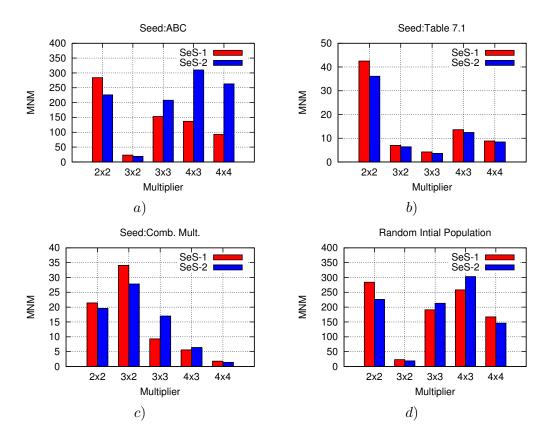

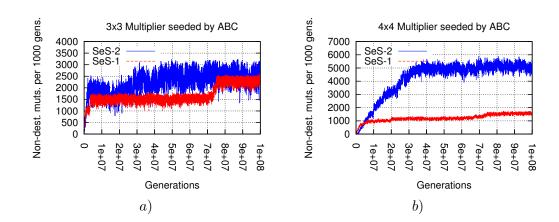

|           |      |                                                           | 37              |  |  |  |  |  |  |  |

|           |      |                                                           | 39              |  |  |  |  |  |  |  |

|           |      | 1 1                                                       | 39              |  |  |  |  |  |  |  |

|           | 7.4  |                                                           | 43              |  |  |  |  |  |  |  |

| 8         | Util | Utilization of Polymorphic Gates in Evolutionary Design 4 |                 |  |  |  |  |  |  |  |

|           | 8.1  |                                                           | 48              |  |  |  |  |  |  |  |

|           | 8.2  | <u> </u>                                                  | 50              |  |  |  |  |  |  |  |

|           | 8.3  | ,                                                         | 50              |  |  |  |  |  |  |  |

|           | 8.4  |                                                           | 52              |  |  |  |  |  |  |  |

|           | 0.1  |                                                           | 52              |  |  |  |  |  |  |  |

|           |      |                                                           | 52              |  |  |  |  |  |  |  |

|           |      |                                                           | 5 <b>-</b>      |  |  |  |  |  |  |  |

|           | 8.5  |                                                           | 55              |  |  |  |  |  |  |  |

| 9         | Dola | Polymorphic Circuit Design                                |                 |  |  |  |  |  |  |  |

| J         | 9.1  |                                                           | <b>58</b><br>58 |  |  |  |  |  |  |  |

|           | 9.1  |                                                           | 59              |  |  |  |  |  |  |  |

|           | 9.4  | <del>-</del>                                              | 59              |  |  |  |  |  |  |  |

|           |      |                                                           | 60              |  |  |  |  |  |  |  |

|           |      |                                                           | 62              |  |  |  |  |  |  |  |

|           | 9.3  | v 1 S                                                     | 64              |  |  |  |  |  |  |  |

|           | 9.3  |                                                           | 65              |  |  |  |  |  |  |  |

|           | 9.4  |                                                           |                 |  |  |  |  |  |  |  |

|           |      | • 5 5                                                     | 65<br>65        |  |  |  |  |  |  |  |

|           |      | • •                                                       | 65<br>ee        |  |  |  |  |  |  |  |

|           | 0.5  |                                                           | 66<br>60        |  |  |  |  |  |  |  |

|           | 9.5  | Summary                                                   | 68              |  |  |  |  |  |  |  |

| <b>10</b> |      |                                                           | <b>7</b> 0      |  |  |  |  |  |  |  |

|           |      | v 1                                                       | 70              |  |  |  |  |  |  |  |

|           |      |                                                           | 71              |  |  |  |  |  |  |  |

|           | 10.3 |                                                           | 71              |  |  |  |  |  |  |  |

|           |      |                                                           | 71              |  |  |  |  |  |  |  |

|           |      | •                                                         | 71              |  |  |  |  |  |  |  |

|           | 10.4 | Summary                                                   | 72              |  |  |  |  |  |  |  |

| 11        | Con  | Conclusions 8                                             |                 |  |  |  |  |  |  |  |

|           | 11.1 | Contributions                                             | 81              |  |  |  |  |  |  |  |

|           | 11.2 | Possibilities of Future Research                          | 82              |  |  |  |  |  |  |  |

Bibliography 84

# Chapter 1

# Introduction

Although the foundation of the digital circuit design dates from the 1950s, there are still many open areas to explore. New opportunities occasionally grow when new technologies are invented. Polymorphic electronics can be considered as one of them. Polymorphic electronics can give us an alternative to conventional digital electronics in some application domains. Researchers expect the utilization of this technology in connection with embodied intelligence where capabilities of sensing and logic operations can be combined in one compact structure, a polymorphic circuit. In continuing research based on graphene technology, scientists are developing components with polymorphic functionality that can be reconfigured on the fly into six different logic gates [99]. Unfortunately, conventional synthesis algorithms are not directly applicable for solving the polymorphic circuit synthesis problem which is, in fact, a more difficult case than the classic digital circuit synthesis problem.

A synthesis algorithm operates over a circuit representation. Various models have been devised to represent digital circuits in such a form which is suitable for synthesis algorithms. Boolean expressions, truth tables and Binary Decision Diagrams (BDD) among others have been utilized. The synthesis algorithms are capable of transforming the initial circuit representation (which is derived from the behavioral specification) onto a circuit representation which is suitable for subsequent circuit fabrication. Usually the goal of logic synthesis is to represent a circuit in the simplest way. The circuit representation, together with the synthesis algorithm, determines the space of possible implementations that one can obtain as a result of the synthesis process.

It remains unclear how to represent a gate-level polymorphic circuit and to define such transformations over a chosen representation which will lead to an efficient implementation of the polymorphic circuit using a given set of ordinary and polymorphic gates. A partial success was achieved using evolutionary design methods which do not pose any requirements on the representation or the set of transformations. However, because the methods are search-based, they are not scalable and only relatively small polymorphic circuits have evolved from scratch. Recall that a similar discipline, evolutionary optimization, allows us to optimize the circuits which have been created by the usage of conventional methods.

This thesis further develops the concept of evolutionary circuit design and optimization that have been known for almost 20 years. The evolutionary approach is primarily applied to the area of polymorphic circuit synthesis with the aim of proposing new synthesis algorithms which lead to more compact circuits.

## 1.1 Thesis Organization

This thesis is organized as follows. The basic principles of digital circuit design are introduced in Chapter 2. This chapter is mainly devoted to basic general design and optimization methods. It introduces some application-specific methods too. An introduction to the evolutionary circuit design is given in Chapter 3 together with the description of Evolvable Hardware concepts and some issues related to evolutionary circuit design. The state of the art of polymorphic electronics area is summarized in Chapter 4. Chapters 2, 3, 4 represent prerequisites for understanding the remaining chapters. The goals of the thesis are formulated in Chapter 5. Subsequent chapters represent the main contributions of the thesis.

Several extensions for the evolutionary algorithm, especially standard Cartesian Genetic Programming (CGP), are proposed in Chapter 6. We divide the evaluation process into the design phase and optimization phase that allows for a more accurate experimental setup to be applied. We modify the standard fitness function to support an optimization with priorities. We also propose a new selection strategy. For speeding up of the complex-problem evaluation, we introduce the short-circuit evaluation and the training-set reordering to the parallel simulation. The proposed extensions are utilized in the following experiments.

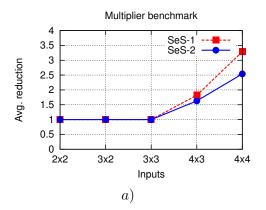

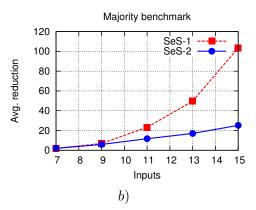

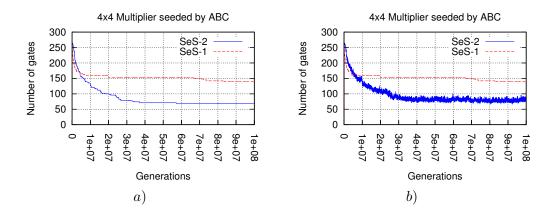

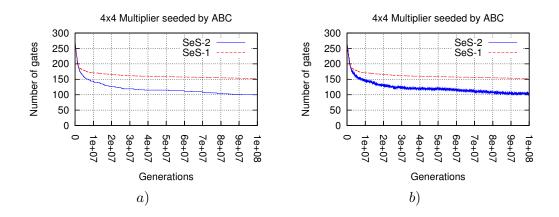

The optimization of ordinary digital circuits is performed in Chapter 7. For evaluation of the results of optimization, we utilize various benchmarks including the multipliers, majority circuits and the LGSynth91 benchmark set. The optimization is performed using the extended CGP and its results are summarized in Section 7.4.

The gate-level evolutionary design with the aim of reducing the number of utilized transistors is investigated in Chapter 8. The prioritized fitness function utilized in Cartesian Genetic Programming is examined on the adder and majority benchmarks. In order to reduce the number of transistors in obtained circuits, we add specific polymorphic gates to the set of available gates. Results of the experiments are summarized in Section 8.5.

Proposed methods for polymorphic-circuits design are described and evaluated in Chapter 9. In particular, the standard Cartesian Genetic Programming, Polymorphic Multiplexing and Polymorphic Binary Decision Diagrams are utilized in the design. We propose a set of benchmarks to compare the algorithms for polymorphic circuit synthesis.

Chapter 10 subsequently deals with the evolutionary optimization of polymorphic circuits conducted by the extended CGP. The best-obtained polymorphic circuits are summarized in Section 10.4

Conclusions, the main contributions of this thesis and future work are given in Chapter 11.

# Chapter 2

# Overview of Digital Circuit Design

The understanding of terms, which are common in digital circuit design, is important for one's orientation in the following chapters. So, let us briefly introduce some principles, structures and methods which are widely used in digital circuit design. Note that the following overview is mostly based on [109].

## 2.1 Digital Circuits – Principles

Digital logic encapsulates the analog world by mapping an infinite set of real values for a physical quality into two subsets which correspond to just two possible numbers or logic values, 0 and 1. As a result, digital logic circuits can be analyzed and designed functionally, using Boolean algebra, truth tables and other abstract means, to describe the operation by binary digits or bits (0s and 1s) in a circuit.

A logic circuit, whose output values depend only on its current input values, is called a *combinational circuit*. Its operation is fully described by a *truth table* that lists all combinations of input values and the output value(s) produced by each of them. A circuit with memory, whose outputs depend on the current input and the sequence of past inputs, is called a *sequential circuit*. The behavior of such a circuit may be described by a *state table* that specifies its output and the next state as functions of its current state and input.

The most basic digital combinational circuits are called *gates*. In general, a gate has one or more inputs and produces an output which is a function of the current input value(s). While the inputs and outputs may be analog effects such as voltage, they are modeled as taking on just two discrete logic values, 0 and 1. The most common implementations of gates are the AND, OR, NOT, NOR, NAND and XOR gates.

A combinational circuit may contain an arbitrary number of logic gates but no feedback loops. A *feedback loop* is a signal path of a circuit that allows the output of a gate to propagate back to the input of that same gate; such a loop generally creates sequential circuit behavior.

In a real design problem, we usually start out with an informal description of the circuit. Often the most challenging and creative part of design is to formalize the circuit description. A formal circuit description defines the circuit's input and output signals and specifies its functional behavior by means of the truth tables and logic expressions. Once we have created the formal description, we can usually follow a synthesis procedure to obtain a logic diagram for a circuit with required functional behavior.

The synthesis procedures are mostly introduced for a one-output circuit description,

but combinational circuits may have one or more outputs. Most synthesis techniques can be extended in an obvious way from a single-output to multiple-output circuit synthesis procedure, for instance, repeating the steps for each output of a circuit description.

## 2.2 Standard Representations of Logic Functions

Five popular representations for a combinational logic function are suggested [109]: a truth table; an algebraic sum of minterms (a canonical sum); a minterm list using  $\sum$  notation; an algebraic product of maxterms (a canonical product); and a maxterm list using  $\prod$  notation. Each one of these representations specifies exactly the same information. For the purpose of the thesis, we introduce the truth table representation and canonical sum.

#### Truth table

The most common representation of a logic function is the *truth table*. This representation simply lists the output of the circuit for every possible input combination. Traditionally, the input combinations are arranged in rows in ascending binary counting order, and the corresponding output values are written in a column that is next to the rows.

#### Canonical sum

The logic function can also be expressed algebraically. In order to do so, we first need to give some definitions: a *literal* is a variable or the complement of a variable; a *product term* is a single literal or a logical product of two or more literals; a *sum-of-product expression* is a logical sum of product terms; and a *minterm* is a product term in which no variable appears more than once.

There is a close correspondence between the truth table and minterms. A minterm can be defined as a product term that is logic 1 in exactly one row of the truth table. Based on the correspondence between the truth table and minterms, we can easily create an algebraic representation of a logic function from its truth table. The *canonical sum* of a logic function is a sum of the minterms corresponding to truth-table rows (input combinations) for which the function produces logic 1 at the output. The term *sum of products* (SOP) is widely used for the canonical sum.

# 2.3 Combinational-Circuit Synthesis

We can translate any logic expression into an equivalent sum-of-product expression, by "multiplying it out". Such an expression may be realized directly with the AND and OR gates. The inverters are also required for complement inputs [109]. The realized circuit is known as a two-level *AND-OR circuit*.

We may insert a pair of inverters between each AND-gate output and corresponding OR-gate input in a two-level AND-OR circuit. These inverters have no effect on the output function of the circuit. If these inverters are absorbed into AND and OR gates, we get AND-NOT gates at the first level and a NOT-OR gate at the second level. These are just two different symbols for the same type of gate, a NAND gate. Thus, a two-level AND-OR circuit can be transformed into a two-level NAND-NAND circuit by substituting some gates [109]. This simple transformation can save a considerable amount of transistors on a chip.

One should note that similarly, the canonical product can be realized by an OR-AND circuit and also this can be transformed into a NOR-NOR circuit.

It is often uneconomical to realize a logic circuit directly from the first logic expression. Canonical sum expressions are especially expensive because the number of possible minterms grows exponentially with the number of variables. Thus, we usually *minimize* a combinational circuit by reducing its number and size of gates that are necessary to realize the required function.

#### 2.3.1 Two-level minimization methods

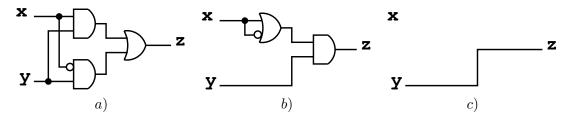

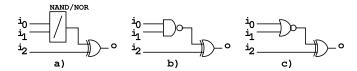

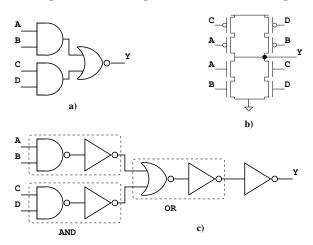

The traditional minimization methods have as their starting point a truth table or, equivalently, a minterm list. Most of the methods are based on a generalization of the combining theorems in Boolean algebra. That is, if two product terms differ only in the complementing or not of one variable, we can combine them into a single term with one less variable. So we save one gate and the remaining gate has one fewer input. Figure 2.1 shows an example of minimization of the logic term,  $z = x.y + \bar{x}.y \rightarrow z = (x + \bar{x}).y \rightarrow z = y$

Figure 2.1: Two-level minimization. The circuits (a), (b), (c) are logically equivalent.

#### Karnaugh maps

A logic function can be expressed graphically into a  $Karnaugh\ map\ [36,\ 107]$  which is a method to simplify a function expression. The Karnaugh map reduces the need for extensive calculations by taking advantage of humans' pattern-recognition capability, permitting the fast identification and elimination of potential race hazards. In the Karnaugh map, variables are transferred (generally from a truth table) and ordered according to the principles of the Gray code in which only one variable changes in between squares. Once the map is generated and the output possibilities are transcribed, the data is arranged into the largest possible groups containing  $2^n$  cells (where n is the number of inputs in an involved subexpression) and minterms are obtained by using basic Boolean operations.

#### Quine-McCluskey algorithm

The Quine-McCluskey algorithm [66, 55, 56] (also known as the method of prime implicants) is another method used for minimization of logic functions. It is functionally identical to Karnaugh mapping, but the tabular form makes it more efficient for use in computer algorithms, and it also gives a deterministic way to check that the minimal form of a logic function has been reached. It is sometimes referred to as the tabulation method. The algorithm, and also other algorithms based on this one, is characterized by an implementation of two phases which are known as a prime-implicant generation and a covering-problem solution.

Note that an implicant is a "covering" (a sum term) of one or more minterms in a sum of products of a logic function. A prime implicant of a function is an implicant that cannot be covered by a more general implicant.

#### Other minimization methods

The above mentioned methods may be considered as basic methods. Many researchers have discovered more effective ways to minimize combinational logic functions [109].

Some minimization problems are just too big to be solved by an "exact" algorithm. Rather than finding a provably minimal expression for a logic function, heuristic methods attempt to find a near-minimal one. Even for problems that can be solved by an "exact" method, a heuristic method may find a good solution much faster. The most successful heuristic program, Espresso-II [5], produces minimal or near-minimal results for a majority of problems.

Multiply-output minimization can be handled by straightforward, fairly mechanical modifications to single-output minimization methods. However, by looking at multiply-output minimization as a problem in multivalued (non-binary) logic, the designers of the Espresso-MV [68] algorithm were able to make substantial performance improvements over Espresso-II.

The number of inputs sometimes reaches hundreds or thousands. Thus, even advanced-minimization methods (such as Espresso) are unusable here, since their runtime is prohibitively large for such functions. *Boolean Minimizer* (BOOM) [15] is capable of handling the functions having thousands of input variables in a reasonable time.

#### 2.3.2 Multi-level representations

Multi-level representations of logic functions have become the key data structures in electronic design because they provide a good compromise between the compactness of representation and the efficiency of manipulation.

#### **Binary Decision Diagrams**

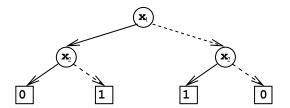

Binary Decision Diagrams (BDDs) [13] are data structures that allow for a canonical representation and efficient manipulation of logic functions [7]. BDD is an acyclic graph which is composed of decision nodes and terminal nodes. The BDD decision nodes are labeled by input variables. The nodes decide on the basis of binary values of the variables. Terminal nodes possess possible output values which are chosen by the input values of the nodes. An example of the two-input XOR function, which is represented in BDD, is shown in Figure 2.2.

The most common variation of BDD is Ordered Binary Decision Diagram (OBDD) [7] which has input variables in an ordered form. A special variation of BDD is Multi-Terminal BDD (MTBDD). As its terminal values can be integers, it supports a multivalued logic.

Note that the BDD representation can easily be implemented by multiplexers or look-up tables<sup>1</sup>).

<sup>&</sup>lt;sup>1</sup>Look-up table (LUT) is a programmable logic component that can implement an arbitrary logic function up to a fixed number of inputs.

Figure 2.2: Representation of the eXclusive-OR (XOR) function in Binary Decision Diagram (BDD). Dashed arrows represent 'false' decision (when  $x_1, x_2 = 0$ ). Solid arrows represent 'true' decision (when  $x_1, x_2 = 1$ ).

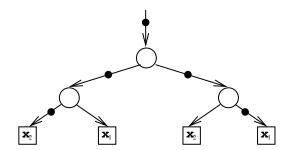

Figure 2.3: Representation of the eXclusive-OR (XOR) function in And-Invert Graph (AIG). Nodes represent the AND operators; terminal nodes represent input variables; and the marked edges represent negation.

#### And-invert graph

And-Invert Graph (AIG) [29, 63] is a directed, acyclic graph that represents a structural implementation of the logical functionality of a circuit or network. An AIG consists of: two-input nodes representing logical conjunction (the AND operators); terminal nodes labeled with variable names; and edges optionally containing markers indicating logical negation (see example of the XOR function in Figure 2.3). This representation of a logic function is rarely structurally efficient for large circuits, but is an efficient representation for manipulation of logic functions.

Conversion from the network of logic gates to AIGs is fast and scalable. It only requires that every gate can be expressed in terms of AND gates and inverters. AIGs allows also a reverse conversion (mapping) of them into networks composed of arbitrary gates.

#### 2.3.3 Synthesis tools

SIS [88], MVSIS [8] and ABC System [2] are the most common open synthesis tools used in the synthesis-algorithm community. The ABC System, supports various representations of logic functions, such as the sum of products, Binary Decision Diagrams, but primarily And-Invert Graphs. It can perform many operations over these representations (primarily over AIGs), such as conversions, minimizations, combinational equivalence checking and synthesis or mapping. The above mentioned tools can be freely used by the research community.

## 2.4 Application-Specific Circuits

The existence of hierarchy and modularity together with a frequent repetition of several basic building elements are the fundamental properties of digital circuits. It is natural that efficient design methods have appeared in the field of digital-circuit design [78, 109]. The methods have been developed from principles of decomposition, minimization and re-usability.

Application-specific designs are specialized implementations for certain tasks. Their main characteristics is that they are generic structures where the structures are designed using building components, such as full adders. The building components can either be generic structures or designed by minimization methods. Another advantage of the application-specific structures is that they are capable of outperforming the minimization methods in certain cases.

Some examples of application-specific circuits are introduced in the following subsections. They will be used as benchmark circuits in the following chapters. It should be noted that optimizations presented in the thesis are mostly focused on area reduction. Hence basic implementations of the generic circuits were chosen without considering delay or other targets.

#### 2.4.1 Combinational multiplier

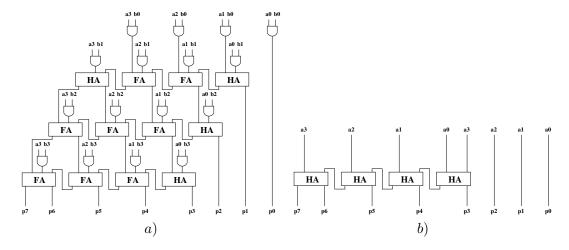

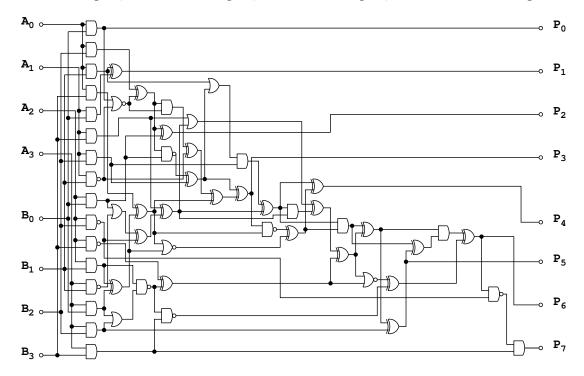

A combinational multiplier can be designed in a basic way as the Carry-Ripple multiplier or the Carry-Save multiplier. While the Carry-Ripple multiplier is more intuitive (see Figure 2.4a), the Carry-Save multiplier is faster but the size of both is the same in terms of gates. The multipliers are composed of full-adders (FA), half-adders (HA) and the AND gates. This implementation is perfectly scalable.

Figure 2.4: Examples of a binary multiplier: a) the 4bx4b multiplier b) a constant-coefficient multiplier which multiplies four-bit input by the 1001 binary value

#### Constant-coefficient multiplier

A constant-coefficient multiplier multiplies an input value by a single predefined constant. Multipliers of this type can be useful in the design of FIR filters [84]. The benefit of the

constant-coefficient multiplier ( with respect to a universal multiplier) is that it can be implemented on a smaller area and with shorter delay. This is because it does not utilize adders and the AND gates on positions where the constant vector holds the logic 0 (see Figure 2.4b).

#### 2.4.2 Binary sorters

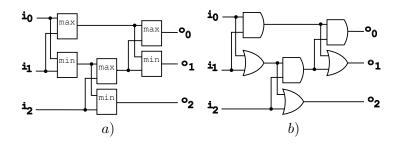

Generic sorters usually implement a common sorting algorithm, such as the Bubble sort or the Merge sort. However, the input-values exchanges are performed by minimum-and maximum-decision components in a circuit implementation which is usually based on sorting-network principles [40]. Binary sorters sort a binary vector. The transformation of an ordinary sorter into a binary sorter is a straightforward process. Minimum (min) and maximum (max) components (see Figure 2.5a) are just converted into AND and OR gates (see Figure 2.5b). Note that the area-optimal sorters have very different schemes for the various number of inputs [120].

Figure 2.5: Examples of the three-input sorter: a) scheme of the ordinary sorter b) scheme of the binary sorter

#### Binary majority circuits

A binary majority circuit detects the majority (dominance, median) of the input values. It returns logic 1 only, if more logic 1s than logic 0s are given at the circuit inputs. The majority circuit can be derived from binary sorters where the "middle" output ( $o_1$  in Figure 2.5b) is considered only. The decide components, which have no influence on the "middle" output, can be wiped out.

#### 2.4.3 Even parity

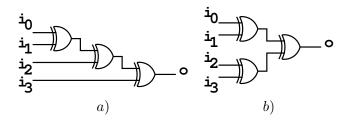

In some cases, it is inefficient to represent a logic function by the standard canonical form. Some problems can easily be expressed by *Reed-Muller canonical form* [24] which is usually an exclusive-or sum of products.

An even-parity circuit detects the even parity of the input values. The parity can be implemented in a serial way (see Figure 2.6a) or a cascade way (see Figure 2.6b) through the utilization of the XOR gates. The ways differ only in delays where the cascade implementation is faster. The area-cost is the same for both implementations.

Figure 2.6: An example of the four-input even parity: a) the scheme of the serial parity b) the scheme of the cascade parity

# Chapter 3

# Evolutionary Design of Digital Circuits and Evolvable Hardware

The aim of this chapter is to briefly introduce the evolutionary approach to engineering design which is needed for orientation in the following chapters. In particular, evolutionary algorithms will be employed for the design and optimization of digital circuits. A brief introduction to Evolvable Hardware is also included.

## 3.1 Evolutionary Algorithms

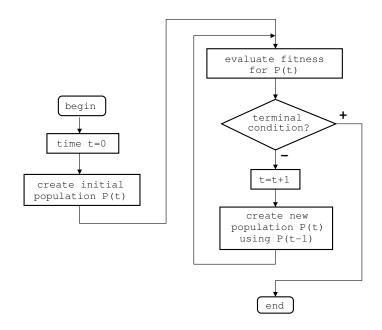

Evolutionary algorithms (EAs) are stochastic search algorithms inspired by Darwin's theory of evolution [47, 78]. The search space is a space which contains all possible considered solutions of the problem. Instead of working with one solution at a time (as random search, hill climbing algorithm or other search methods do [57]), these algorithms work with a population of candidate solutions (individuals). Every new population is formed by using genetically inspired operators (such as crossover and mutation) and by selection pressure which guides the evolution towards better areas of the search space. The evolutionary algorithms receive guidance by evaluating every candidate solution to define its fitness value. The fitness value, calculated by a fitness function, indicates how well the solution fulfills the problem objective (specification).

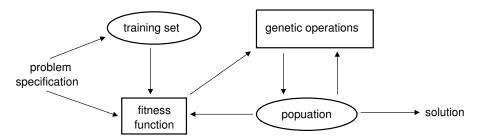

For the most part, a higher fitness value implies a greater chance that an individual will "live" for a longer period of time and produce offspring who will inherit a parental genetic information. This leads to the production of a novel genetic information and to novel solutions of the problem. The fundamental structure of an evolutionary algorithm is captured in Figure 3.1 and its data-flow diagram is illustrated in Figure 3.2.

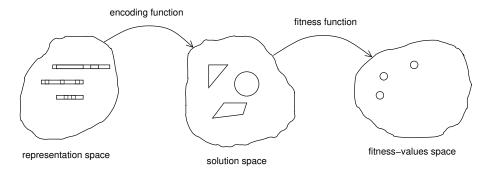

Because the objects in the search space can be arbitrary structures (e.g. real-valued vectors, circuits), it is often helpful to distinguish between a representation space (genotype space) and a solution space (phenotype space) [78]. As shown in Figure 3.3, encoded solutions (genotypes) have to be mapped onto actual solutions (phenotypes). In general, the problem representation consists of a representation space and the encoding function. The fitness function is applied to evaluate phenotypes. While the fitness function works with phenotypes, genetic operators (e.g. crossover, mutation) are defined over genotypes. There is one important rule in this concept of genotype-phenotype mapping: a small change in the genotype should induce a small change in the phenotype in order to obtain a reasonably efficient search algorithm.

Figure 3.1: Control-flow diagram of an evolutionary algorithm.

Figure 3.2: Data-flow diagram of an evolutionary algorithm.

Figure 3.3: The concept of genotype-phenotype mapping.

Any evolutionary algorithm can be viewed as utilizing one or more genetic operators which produce new candidate solutions from those previously visited in the search space. Effective algorithms achieve the balancing of two conflicting goals: *exploiting* the best solution which has been found up to now; and *exploring* the search space [57]. Each search space is different and even identical spaces can appear very different under different representations and fitness functions. So there is no way to choose a single search method that can serve well in all cases [57].

Traditionally, four main variants of an evolutionary algorithm are presented [47, 78]: Genetic Algorithm, Genetic Programming, Evolution Strategy and Evolutionary Programming. For the purpose of this thesis, Genetic Programming and Evolution Strategy are relevant and need to be introduced.

#### Genetic Programming

Genetic Programming (GP) [42, 43, 44] has been developed by John R. Koza to allow automatic programming and program induction. GP does not distinguish between the representation space and the solution space.

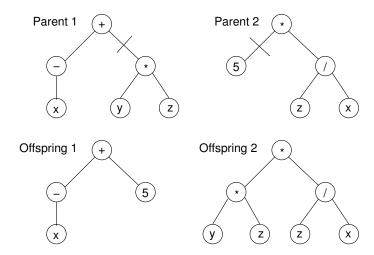

Programs (genotypes) are represented either as tree structures (Tree-based GP) or in a linear form (Linear GP) using machine-language instructions [78]. A crossover is considered as a major genetic operator for Genetic Programming. Figure 3.4 shows that the crossover interchanges randomly chosen subtrees of parents' trees without the disruption of the syntax. A mutation, another genetic operator, picks a random subtree and replaces it with a randomly generated one. A selection is typically implemented as a probabilistic operator, using the relative fitness, which determines the selection probability of an individual. The most important application of GP is symbolic regression.

Figure 3.4: A single-point crossover in Genetic Programming

An evolved program may contain segments which do not alter the result of the program execution when they are removed from it, that is, semantically redundant segments (e.g., i = i + 0). Such segments are referred to as *introns* [48]. The program size can also grow uncontrollably until it reaches the tree-depth maximum, while the fitness remains unchanged. This effect is called a *bloat* [58]. Problems and benefits of introns, bloat and their relationship are discussed in [48, 58].

#### **Evolution Strategy**

Evolution Strategy (ES) [76] was developed for optimization purposes in industrial application by Bienert, Rechenberg and Schwefel in the 1960s. Like Genetic Programming, Evolution Strategy does not distinguish between a genotype and phenotype. Each individual is represented as a real-valued vector. A mutation is regarded as the primary genetic

operator. It aggregates a normal-distributed random variable and a preselected standard deviation value which are applied on every gene of a candidate vector.

Evolution Strategy usually selects the parents deterministically. The algorithm provides two major selection scenarios:  $(\mu + \lambda)$ -ES and  $(\mu, \lambda)$ -ES. The  $(\mu + \lambda)$ -ES selects the best  $\mu$  individuals from both offspring and parent populations (of size  $\mu + \lambda$ ). If an offspring gets a better fitness value than its parent, the offspring becomes the new parent. Otherwise, the parent is mutated to create a new offspring. The  $(\mu, \lambda)$ -ES selects the best  $\mu$  individuals from only the offspring population (of size  $\lambda$ ).

#### Evolutionary design and optimization

Evolutionary algorithms can be utilized in various applications. Bentley's classification [14] defines four main categories of an evolutionary-algorithm application: creative evolutionary design, evolutionary design optimization, evolutionary art and evolutionary artificial-life forms. From the perspective of the thesis, creative evolutionary design and evolutionary design optimization are relevant for the following chapters.

In the *creative evolutionary design*, the evolutionary algorithms have the ability to generate entirely new designs when they start from little or nothing and are guided purely by functional performance criteria [14]. An emphasis is placed on novelty and originality. Creative evolutionary design is able to introduce new genes (variables) in a genotype and thus to define new search spaces.

In the evolutionary design optimization, an optimization process requires finding a set of free parameters under consideration, so that a certain quality criterion (the fitness value) is minimized (or maximized) [12]. Designers usually start the process with an existing design and parametrize its parts that need improvement. The parameters are encoded into a genotype and then the evolutionary algorithm is involved in finding a sufficient solution. Optimization places an emphasis on finding a solution which is as close to the global optimum as possible.

## 3.2 Evolvable Hardware

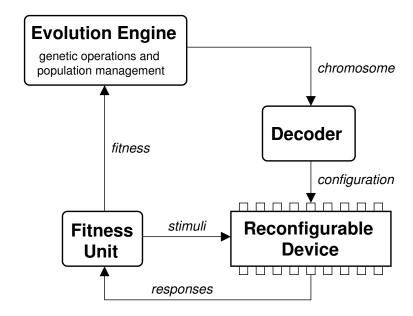

Evolvable hardware (EHW) [25, 30, 78, 100] involves evolutionary algorithms to create specialized hardware automatically. It brings together artificial intelligence methods and reconfigurable hardware. In some cases, EHW is capable of changing a hardware architecture and behavior dynamically and autonomously.

EHW problems fall into two categories [25]: evolutionary hardware design and adaptive systems. The *evolutionary hardware design* uses evolutionary algorithms to evolve a system that meets a predefined specification. The *adaptive systems* reconfigure an existing design to counteract faults or a changed operational environment. Figure 3.5 illustrates relations between an evolutionary algorithm (Evolution Engine and Fitness unit) and reconfigurable hardware.

Two scenarios have been developed for hardware evolution: extrinsic evolution and intrinsic evolution. In *extrinsic evolution*, all candidate circuits are simulated to obtain a fitness score and only the final best solution in the final population is usually physically implemented. In *intrinsic evolution*, every individual in every generation is evaluated in real hardware. The importance of intrinsic evolution was discovered by Thompson [100].

Most reconfigurable devices consist of configurable blocks where functionality and interconnections are controlled by a configuration bitstream. Many types of reconfigurable

Figure 3.5: High-level description of an evolvable hardware approach

devices have been utilized in EHW. Typical reconfigurable devices are Programmable Logic Arrays (PLAs), Field-Programmable Gate Arrays (FPGAs) for digital designs, Field-Programmable Analog Arrays (FPAAs) for analog designs and Field-Programmable Transistor Arrays (FPTAs) which have been applied to implement either digital or analog designs. Special devices have also been utilized such as a Reconfigurable Polymorphic Module (RE-POMO) [73] (see Section 4.2.1) or a Multi-Logic-unit Processor (MLP) [108]. More exotic reconfigurable devices include reconfigurable liquid crystals (Evolution in materio) [26], reconfigurable molecular array (NanoCell) [32], reconfigurable antenna array [51] and reconfigurable optics (deformable mirrors) [52].

Evolutionary hardware design was employed for the creation of innovative designs such as small combinational circuits [59], digital filters [31], image operators [78], classifiers [21] or diagnostic benchmark circuits [65].

Adaptive hardware was involved in several applications, for instance, in self-configurable integrated circuits [92], adaptive image compression methods [75], myoelectric prosthetic hand controller [33] or post-fabrication tuning of filters [64].

# 3.3 Cartesian Genetic Programming

Cartesian Genetic Programming (CGP) is a sub-domain of GP [62]. CGP is a widely-used method for evolution of programs and digital circuits [62, 59, 104, 35, 17]. In its basic version which is important for the thesis, candidate circuits are directly represented in the chromosome. Extensions of CGP have been proposed in recent years, for example, self-modifying CGP [27], modular CGP [110, 37] or multi-chromosome CGP [111].

#### 3.3.1 Basic CGP

CGP was introduced by Miller and Thompson a decade ago [62]. It resembles the concept of Genetic Programming but introduces some important modifications: (i) a candidate circuit is modeled using a directed acyclic graph; (ii) the graph is encoded as a fixed-size string

of integers; and (iii) a search is performed using a mutation-based Evolution Strategy (no crossover is employed). The main advantage of CGP is that it generates very compact solutions, that is, it can effectively reduce the total number of gates in the case of circuit evolution [104].

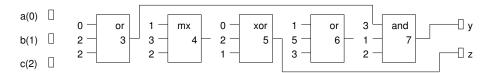

In the basic version of CGP, a candidate circuit is modeled in a matrix of  $n_c \times n_r$ of programmable  $n_a$ -input elements where  $n_c$  is the number of columns (the horizontal size) and  $n_r$  is the number of rows (the vertical size). The number of inputs,  $n_i$ , and outputs,  $n_o$ , of the circuit is fixed. Each gate input can be connected either to the output of a gate placed in the previous l columns or to one of the circuit inputs. The l-back (level-back) parameter, in fact, defines the level of connectivity, thus reducing/extending the search space. For example, if l=1 then only neighboring columns may be connected (useful in the design of pipeline architecture); if  $n_r = 1$  and  $l = n_c$  then full connectivity is allowed. Since only combinational circuits will be evolved (in this thesis), no feedback loops are allowed in candidate circuits. Each gate can be programmed to perform one of  $n_a$ -input logic operations defined in the  $\Gamma$  gate set. Each element is encoded as a list of  $n_a + 1$  (unsigned) integers where the first  $n_a$  components are elements indexes (connections of element inputs and elements outputs) and the last component is the index of a logic operation (from the  $\Gamma$  set). An element input can be connected to either the output of the preceding element or to a primary circuit input. Every individual is encoded as a list of elements using  $n_c.n_r.(n_a+1)+n_o$  integers, where the last  $n_o$  components are the elements indexes which represent the primary circuit outputs. As Figure 3.6 shows, while the size of chromosome is fixed, the size of phenotype is variable (i.e. some nodes are not used).

Figure 3.6: An example of a circuit in CGP with parameters:  $n_i = 3$ ,  $n_o = 1$ , l = 6,  $n_c = 6$ ,  $n_r = 1$ ,  $\Gamma = \{0 : AND, 1 : OR\}$ . Elements 4 and 8 are not utilized. Chromosome is: 1,2,1, 2,2,0, 1,2,0, 0,5,1, 3,6,0, 0,7,1, 7. Logic operations of elements are typed in bold. The last integer indicates the output of the circuit.

#### 3.3.2 Circuit evolution using CGP

The goal of the evolutionary circuit design, when it is applied to logic synthesis, is to obtain a perfectly working circuit (all assignments to the circuit inputs have to be tested). When the perfectly working circuit (correct circuit) is obtained, then it should be "optimized", that is, the number of utilized gates is minimized. Other optimization criteria can be included; however, this thesis mostly considers the number of gates only (except Chapter 8). In the case of the combinational circuit evolution, the fitness function to evaluate a candidate circuit is typically defined in CGP as [35]:

$$fitness = \begin{cases} b & when \quad b < n_o.2^{n_i}, \\ b + (n_c.n_r - z) & otherwise, \end{cases}$$

(3.1)

where b is the number of correct output bits obtained as the response for all possible assignments to the inputs; z denotes the number of gates utilized in a particular candidate circuit; and  $n_c.n_r$  is the total number of available elements. It can be seen that the term

$n_c.n_r-z$  is considered only if the circuit behavior is perfect, that is, if  $b=n_o.2^{n_i}$ . We can observe that the evolution is forced (by the fitness function) to first discover a perfect working solution while the size of circuit is not important. After discovering the correct solution, the evolution is forced to minimize the number of gates of the correct circuit.

CGP operates with the population of  $1 + \lambda$  individuals ( $\lambda$  is from 4 to 15 typically). The initial population is either randomly generated or created by a heuristic procedure. The initial population can be created using conventional methods or synthesis tools (such as ABC System, SIS) in the case of the heuristic procedure.

Every new population consists of the best individual of the previous population (previous generation) which acts as the parental individual. The offspring individuals are created by a point mutation operator which modifies h randomly selected genes of the parental individual where h is a user-defined value. The implementation of the mutation operator has to ensure that the modification of gene is legal. The algorithm is usually terminated when the maximum number of generations is reached or a sufficient working solution is obtained.

There is an important rule for the selection of the parental individual. In the case when two or more individuals are able to become the parent, the individual which has not been a parent in the previous population will be selected as the new parent. In the case when there are more candidates then the parent is chosen randomly. This strategy is important because it ensures diversity in the population. The strategy has been proven to be very useful in [59, 106].

CGP has been successfully utilized in many applications [59, 17, 77, 41, 39]. It has been investigated experimentally [61] and extended to support modularity, self-modification and other features [110, 28]. In particular, it was shown that multipliers evolved by CGP [104] are smaller than the best known designs of that time (when the number of 2-inputs gates is the decision criterion).

#### Redundancy and neutrality

The encoding used in CGP is redundant since there may be genes that are entirely inactive. These genes do not influence the phenotype and hence the fitness score. This phenomenon is often referred to as *neutrality*. The role of neutrality has been investigated in detail [115, 105, 61]. For example, it was discovered that the most evolvable representations occur when the genotype is extremely large and in which over 95% of the genes are inactive [61]. But in another example, Collins has shown that for some specific problems, the neutrality-based search is not the best solution [11]. Miller has also identified that the problem of bloat is insignificant for CGP [58].

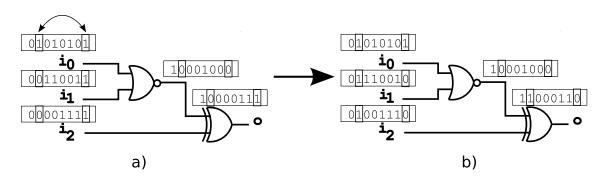

#### Parallel simulation

Parallel simulation is the technique that can be used to accelerate the circuit evaluation [59]. The idea of the parallel simulation is to utilize bitwise operators which operate on multiple bits at a high-level language (such as the C language). The technique performs more than one evaluation of a gate in a single step. For example, when a combinational circuit under simulation has three inputs and it is possible to concurrently perform bitwise operations over  $2^3 = 8$  bits in the simulator, then the circuit can be completely simulated by applying a single 8-bit test vector at each circuit input (see the encoding in Figure 3.7). In contrast, when it is impossible then the eight three-bit test vectors must be applied sequentially. Practically, current processors allow us to operate with 64 bit operands, that

means, it is possible to evaluate the truth table of a six-input circuit by applying a single 64-bit test vector at each input. Therefore, the obtained speedup is 64 against the sequential simulation. In the case that a circuit has more than 6 inputs, then the speedup is constant (i.e. 64). This technique has been applied in all evolutionary design and optimization experiments reported in the thesis.

Figure 3.7: Parallel evaluation of a candidate circuit

## 3.4 Scalability Problem

In the context of the evolutionary circuit design, the *scalability problem* is often mentioned in the literature [106, 114, 23]. The implication of the scalability problem is that only relatively simple circuits have been evolved so far.

The main problem of the evolutionary combinational-circuit design is that the evaluation time of a candidate circuit grows exponentially with the increasing number of inputs (assuming that all possible input combinations are evaluated by the fitness function) [106]. Hence, the evaluation time becomes the main bottleneck of the evolutionary approach when complex circuits with many inputs are evolved. Another problem is that the genotype size grows with the increasing complexity of target circuits. Long chromosomes imply large search spaces that are usually difficult for EA.

We will briefly introduce some techniques that were developed to suppress the influence of the scalability problem of the evolutionary circuit design. The most common techniques are: incremental evolution, the multi-chromosome approach and development.

Incremental evolution and the multi-chromosome approach are based on the decomposition of a complex problem into sub-problems. The sub-problems can be evolved in a reasonable time. The technique uses a training set and training vector partitioning [102]. For solving the sub-problems, CGP can be used. The bidirectional incremental evolution [34] incorporates two approaches: divide-and-conquer [101] and incremental evolution [22]. Bidirectional incremental evolution is based on gradual decomposition of a complex problem into sub-problems of decreasing complexity and afterwards, on gradual evolution of sub-problems of increasing complexity into a complex problem. This approach utilizes the training set and training vector partitioning. The multi-chromosome approach [111] is based on a genotype which consists of several chromosomes. Each chromosome represents a solution for one output of a target circuit. The output solutions (chromosomes) are evolved simultaneously. An individual is represented by the genotype (not by a single chromosome). This approach utilizes training vector partitioning.

Computational development [3, 45, 82] is usually considered as a non-trivial and indirect mapping from genotypes to phenotypes in an evolutionary algorithm. In such a case, the genotype has to contain a prescription for construction of the target object. While the

genetic operators work with genotypes, the evaluation of candidate solutions (the fitness evaluation) is applied on phenotypes created by means of development. The principles and selected application of development are summarized in [46, 4]. Lindenmayer systems (L-systems), cellular automata, graph-generation grammars and an instruction-based development are major approaches to development. These models were applied to design digital circuits. The main problem of current development is that resulting circuits are not competitive with conventional synthesis [4].

# Chapter 4

# Polymorphic Electronics

Polymorphic electronics is a new unconventional sub-area of electronics. It was introduced by A. Stoica's group at the NASA Jet Propulsion Laboratory as a new class of electronic devices that exhibit a new style of (re)configuration [97]. Polymorphic electronics<sup>1</sup> has a superimposed built-in functionality. A change of function does not need reconfiguration/switches as in traditional approaches. The changes of functionality come from an environment, such as temperature, light, power supply voltage and control signal. Polymorphic electronics can be understood as a new reconfigurable technology capable of integrating logic functions with sensing in a single compact structure. In fact, the fundamental building components, polymorphic logic gates, merge the capability of performing logic operations with sensing. Hence polymorphic gates would also be very useful in building the embodied intelligence—intelligent devices, whose functionality emerges in interaction with a physical environment [6]. Although polymorphic gates can be implemented relatively effectively using current CMOS technology, we can expect an expansion of polymorphic devices with further development of nanoelectronics and molecular electronics.

Current research in the area of polymorphic electronics can be split into three fields: design of reliable polymorphic gates, development of synthesis algorithms and development of applications. We will briefly survey them in the following sections.

# 4.1 Polymorphic Gates

Polymorphic gates play a central role in polymorphic electronics. The polymorphic gate is capable of switching among two or more logic operations (functions). However, the selection of the operation is performed unconventionally. The logic operation of a polymorphic gate depends on some external factors, for example, on the level of the power supply voltage  $(V_{dd})$ , temperature, light or some other external signals [74, 93, 94, 95, 96, 97, 98, 118, 119].

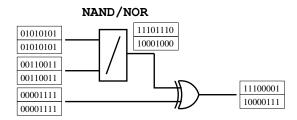

A polymorphic gate implements several logic operations according to a control signal which can hold different values. For purposes of this thesis, we denote a bi-functional polymorphic gate as  $X_1/X_2$ , where  $X_1$  is the logic operation of the first mode (mode 1) and  $X_2$  of the logic operation of the second mode (mode 2). For example, Stoica's polymorphic bi-functional NAND/NOR gate [93] controlled by  $V_{dd}$  operates as the NOR gate for  $V_{dd} = 1.8 \text{ V}$  (mode 1) and the NAND gate for  $V_{dd} = 3.3 \text{ V}$  (mode 2).

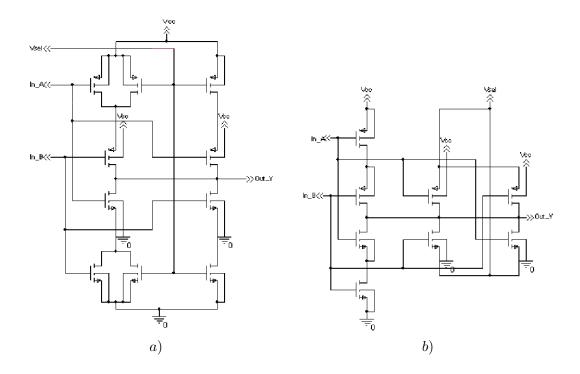

Table 4.1 surveys the polymorphic gates reported in the literature. The gates were designed mostly through an evolutionary approach [94, 98, 116]. Only three of them have

<sup>&</sup>lt;sup>1</sup>Polymorphic electronics is also known as polytronics [97]

been fabricated so far; the remaining polymorphic gates were either simulated or tested in a field programmable transistor array (FPTA-2). The six-transistor NAND/NOR gate [93] controlled by the power-supply voltage,  $V_{dd}$ , was fabricated in the 0.5-micron HP technology. The ten-transistor NAND/NOR gate [95] controlled by  $V_{dd}$  was fabricated in the 0.5-micron HP technology. Another eight-transistor NAND/NOR gate [74] controlled by  $V_{dd}$  was fabricated in the 0.7-micron AMIS technology.

Table 4.1: Existing polymorphic gates. The 'Trans.' label denotes utilized transistors and the 'Ref.' label denotes references in the literature.

| Gate                         | Control Values                    | Control        | Trans. | Ref.  |

|------------------------------|-----------------------------------|----------------|--------|-------|

| AND/OR                       | 27/125°C                          | temperature    | 6      | [97]  |

| NAND/NOR                     | $80/120^{\circ}{ m C}$            | temperature    | 12     | [96]  |

| AND/OR/XOR                   | 3.3/0.0/1.5  V                    | control signal | 10     | [97]  |

| AND/OR                       | 3.3/0.0  V                        | control signal | 6      | [97]  |

| NAND/NOR/NXOR/AND            | 0/0.9/1.1/1.8 V                   | control signal | 11     | [118] |

| NAND/WIRE/AND                | 0.0/1.0/-1.8 V                    | control signal | 9      | [119] |

| WIRE/OR/XOR/AND2b/NAND/AND1b | 0.0/0.2/0.4-0.8/1.0/1.2-1.6/1.8 V | control signal | 19     | [94]  |

| NAND/NOR                     | $0/2.5 \mathrm{~V}$               | control signal | 10     | [89]  |

| NOR/NAND                     | $0/2.5 \mathrm{~V}$               | control signal | 8      | [72]  |

| NAND/XOR                     | 0/2.5  V                          | control signal | 9      | [70]  |

| AND/OR                       | 1.2/3.3  V                        | supply voltage | 8      | [98]  |

| NAND/NOR                     | 3.3/1.8  V                        | supply voltage | 6      | [93]  |

| NAND/NOR                     | 3.3/1.8  V                        | supply voltage | 10     | [95]  |

| NAND/NOR                     | $5/3.3~\mathrm{V}$                | supply voltage | 8      | [74]  |

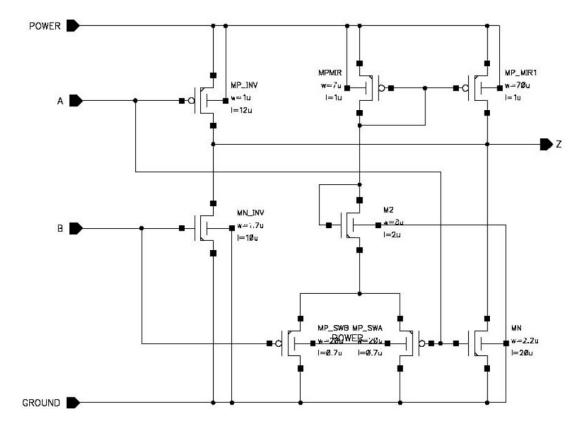

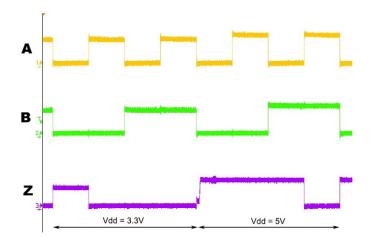

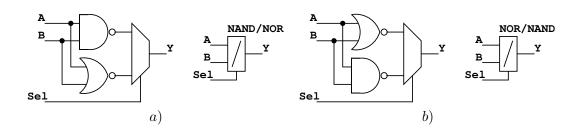

Figure 4.1 shows one of possible designs of the polymorphic NAND/NOR gate which was published in [74]. Logic operations of this circuit are controlled by the power supply voltage. Circuit responses (the Z label) are demonstrated for all possible input combinations (the A, B labels) in Figure 4.2. The waveforms come from measurements of the gate implementation in the 0.7-micron AMIS technology.

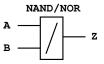

Figure 4.3 shows a circuit symbol of a polymorphic gate. If logic operations of a gate are not obvious from the context, the logic operations are given as a part of the gate symbol. Because the circuit symbols for any polymorphic gates are not yet under any international (even national) standard, thus the symbol given in Figure 4.3 is presented for local usage in circuit schemes of this thesis.

However, some gates, which are introduced in Table 4.1, do not exhibit electronic properties as good as standard CMOS gates. For example, very high power consumption was reported for the NAND/NOR gate [74]. Due to this fact, the spectrum of applications is limited for polymorphic electronics nowadays.

# 4.2 Polymorphic Circuits

Having polymorphic gates, researchers have begun to develop new methods for synthesis of digital circuits that contain polymorphic gates [18, 53, 79, 87]. The main motivation is to obtain reconfigurable (and thus potentially adaptive) circuits for a very low cost and without the necessity to implement a reconfiguration infrastructure, such as switches, multiplexers or configuration registers. Figure 4.4a shows an example of a *polymorphic digital circuit* and

Figure 4.1: Transistor-level implementation of the NAND/NOR gate published in [74]. The gate realizes the NAND operation for  $V_{dd}$  from 3.9 to 5.0 V and the NOR operation for  $V_{dd}$  from 3.0 to 3.7 V. The A,B labels denote the inputs and the Z label denotes the output.

Figure 4.2: Behavior of the NAND/NOR polymorphic gate [74] measured at 5 kHz. The A, B labels denote the inputs and the Z label denotes the output.

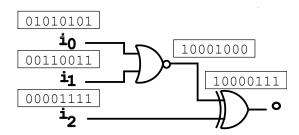

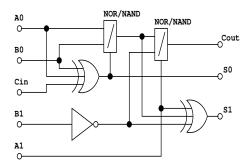

Figures 4.4b,c show its equivalent behavior in both modes of the polymorphic NAND/NOR gate. The equivalent functions are  $f_1 = \overline{i_0 \wedge i_1} \oplus i_2$  in mode 1 and  $f_2 = \overline{i_0 \vee i_1} \oplus i_2$  in mode 2.

Figure 4.3: A circuit symbol of a polymorphic NAND/NOR gate.

Figure 4.4: a) Example of a polymorphic circuit; b) Equivalent circuit in  $mode\ 1$ ; c) Equivalent circuit in  $mode\ 2$

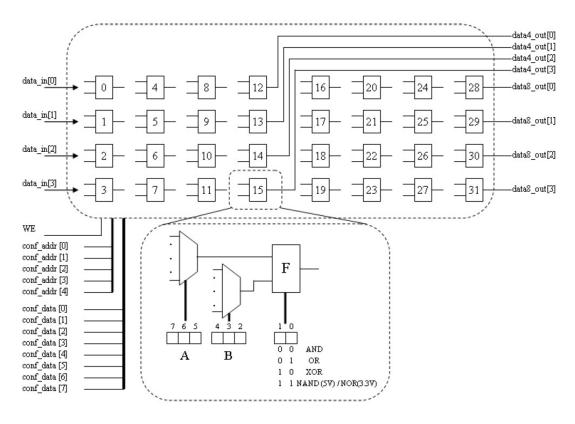

#### 4.2.1 REPOMO32 platform

A Reconfigurable Polymorphic Module (REPOMO) [73, 85, 103] has been developed in order to investigate electrical properties of polymorphic circuits and to demonstrate the applications of polymorphic electronics. The REPOMO32 platform contains an array of 32 configurable logic elements; each of them can perform the AND, OR, XOR and polymorphic NAND/NOR logic operation. Since the set of logic operations is complete, the platform can perform any logic function (of course, functionality is limited by the chip size). This chip utilizes the NAND/NOR gates [74] controlled by power supply voltage,  $V_{dd}$ . When  $V_{dd} = 5.0 \ V$  the polymorphic gate exhibits the NAND operation and when  $V_{dd} = 3.3 \ V$  the gate exhibits the NOR operation. The remaining ordinary (conventional) gates do not change their logic operations with a shift of  $V_{dd}$  (from 3.0 V to 5.0 V). Figure 4.5 shows the block structure of the REPOMO32 platform.

# 4.3 Applications of Polymorphic Electronics

Papers [97, 98] suggest various areas in which polymorphic gates can be utilized. Applications of polymorphic electronics, which were reported or proposed so far, are given as references in the following summary:

- (i) Automatic change of circuit behavior when a power supply is not sufficient [84].

- (ii) Implementation of low-cost reconfigurable/adaptive systems that are able to adjust their behavior inherently in response to certain control signals, such as multi-functional counters [70, 118].

- (iii) Implementation of novel concepts for testing and diagnosing of electronic circuits, such as self-checking adders [54, 74] utilization or reduction of test vector volume [90].

- (iv) Implementation of a hidden function (invisible for the user) which can be activated in a specific environment [97, 98].

- (v) Intelligent sensors for biometrics, robotics and industrial measurement [97, 98].

- (vi) Reverse engineering protection [97, 98].

In the following paragraphs we briefly introduce some applications that have been developed at FIT BUT.

Figure 4.5: The REPOMO32 block structure published in [85].

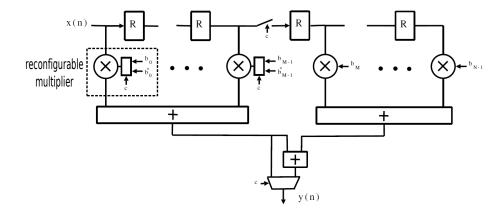

#### 4.3.1 Polymorphic FIR filter

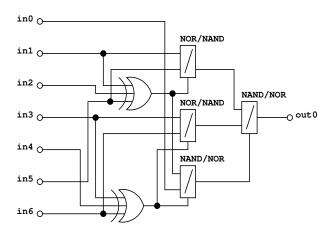

The polymorphic FIR filter [84] with backup mode enabling power saving (see Figure 4.6) can operate in two modes. In the first mode (standard mode), the filter performs a normal function. In the second mode (backup mode), the filter operates with a reduced power supply voltage. In this mode, some filter coefficients are reconfigured and the rest of the filter is disconnected. Experiments have indicated that power consumption can significantly be reduced in the backup mode while the quality of filtering remains reasonable. One should note that the reconfigurable constant-coefficient multipliers of the FIR filter are implemented using the NAND/NOR polymorphic gates.

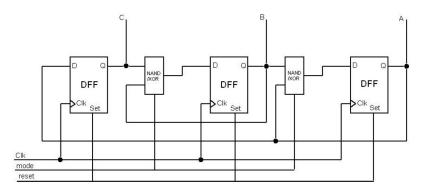

#### 4.3.2 Polymorphic controller

Let us imagine that an intelligent controller is needed in some application. A feature of that controller is that it can skip less important states under some circumstances, such as low power or high temperature. An example of such a controller is the three-bit *polymorphic controller* published in [69, 70, 71] (see Figure 4.7). This controller has seven states in the normal mode and five states in the backup mode. Note that in this design, the next-state logic is implemented utilizing the NAND/XOR polymorphic gates.

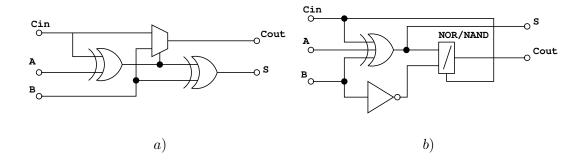

#### 4.3.3 Self-checking adder

The polymorphic self-checking adder [74, 80, 81, 85] does not utilize any additional signals to indicate the fault. The adder is able to detect a reasonable number of stuck-at-faults

Figure 4.6: FIR filter with backup mode enabling power savings published in [84].

Figure 4.7: Multi-functional circuit which operates as a controller [69] with different operational modes.

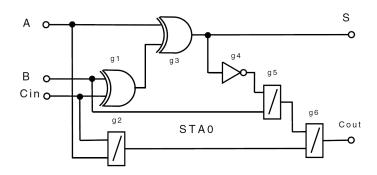

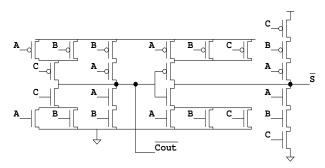

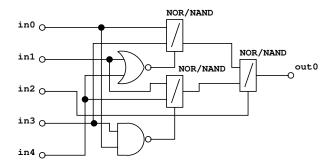

by oscillations at the  $C_{out}$  output while the control signal of polymorphic gates oscillates. The logic circuitry of the self-checking full-adder can be seen in Figure 4.8. Note that this adder utilizes the NAND/NOR gates and has reasonable area overhead.

Figure 4.8: Full adder with the self-checking feature taken from [81]. It utilizes NAND/NOR polymorphic gates.

# Chapter 5

# Goals

Previous chapters have shown that Cartesian Genetic Programming is applicable to design and optimization of the digital circuits. However, we would like to improve some parts of the algorithm in order to get better solutions.

At the beginning, we need to put several questions to ourselves in the field of circuit design and optimization that will lead our research. Is it possible to optimize current implementations of application-specific circuits with the evolutionary algorithm? And what algorithm or its extension is suitable to be involved in the optimization process? How shall we modify conventional circuit synthesis methods in order to allow them to operate with polymorphic gates? Can we minimize the number of gates in polymorphic circuits that we have designed by "adapted" conventional methods? What benchmarks should be utilized to compare the results?

For answering these questions, we have defined the following goals for the doctoral thesis:

- To employ Cartesian Genetic Programing and its modifications as an evolutionary algorithm in the ordinary-circuit optimization with the goal of improving existing results of combinational circuit synthesis.

- To utilize specific polymorphic gates in ordinary circuits to minimize the circuit size in terms of the number of utilized gates. Cartesian Genetic Programing will be used with the modified fitness function.

- To propose and investigate new approaches to polymorphic-circuit design based on polymorphic multiplexing and polymorphic Binary Decision Diagrams. We will compare the solutions obtained by these two new approaches with solutions obtained from Cartesian Genetic Programing. Since there is not available any benchmark set of polymorphic circuits, we will introduce a new set of benchmark circuits to evaluate and compare the synthesis algorithms.

- There is a possibility that the polymorphic multiplexing and polymorphic Binary Decision Diagrams will not be able to produce area-inefficient solutions. Thus, the goal is to employ the extended Cartesian Genetic Programing to optimize a polymorphic circuit at the gate level.

In order to fairly compare the results of various methods, the solutions will mainly be sought in the form of circuits composed of the two-input gates.

# Chapter 6

# Extensions of Standard Cartesian Genetic Programming

For purposes of this thesis, it is useful to extend Cartesian Genetic Programming (CGP). The extension is necessary for improving the search-space-exploration capabilities and reducing the computation overhead. The extension is derived from the standard CGP introduced in Section 3.3. It should be noted that the definition of a chromosome and its phenotype remains unchanged.

## 6.1 Design Phase and Optimization Phase

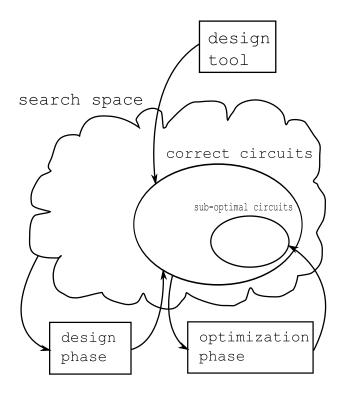

For our experiments, it is suitable to divide the CGP runtime into two phases. I call them as the design phase and the optimization phase. The design phase is usually performed before the optimization phase in CGP (see Figure 6.1). The design phase is typically performed for searching of a brand-new correct circuit. The search is usually conducted from an initial population of random individuals. It employs a fitness function which evaluates the circuit behavior only. When a candidate circuit conforms to the behavioral specification, then the number of gates becomes important. The optimization phase is typically performed to optimize (e.g., the number of gates) a fully functional circuit.

The division into two phases offers us better conditions for setting the CGP. Each phase can utilize different parameters, such as the size of a population, mutation operator, selection method or fitness function. Note that the design phase and optimization phase can be executed independently. In other words, the optimization phase does not have to follow the design phase and also the design phase does not have to precede the optimization phase. The design phase can be substituted by conventional design tools, such as SIS or the ABC System.

## 6.2 Modified Fitness Functions

In order to avoid a conditionally defined fitness function (see the when-otherwise condition in Equation 3.1), it is useful to define a new fitness function where priorities are set for various objectives. The intended approach allows us to aggregate various objectives into a single fitness value. Since the goal is to minimize, the new definition also has a new global extreme, the minimum, which is the value of 1. Note that the problem is not considered as multi-objective in this thesis.

Figure 6.1: Relations among the search space, design phase and optimization phase.

The new fitness function of one objective is defined as follows:

$$fitnessp_1 = 1 + q_1.g_1;$$

(6.1)

$g_1 = 1,$

where  $q_1$  is the objective (the goal is to minimize  $q_1$  here) and  $g_1$  is generic constant.

The new fitness function of two objectives (priorities) is defined as follows:

$$fitnessp_{2} = 1 + q_{2}.g_{2} + q_{1}.g_{1};$$

$$g_{1} = 1,$$

$$g_{2} = (f_{max}(q_{1}) + 1).g_{1},$$

$$(6.2)$$

where  $q_2$  is the more preferred objective over  $q_1$ ;  $g_1, g_2$  are generic constants and  $f_{max}(q_1)$  gives the maximum value of the  $q_1$  objective.

The resulting generic fitness function for n objectives (priorities) is defined as follows:

$$fitnessp_n = 1 + q_n \cdot g_n + ... + q_1 \cdot g_1;$$

$$g_1 = 1,$$

$$g_i = (f_{max}(q_{i-1}) + 1) \cdot g_{i-1}, i = 2..n,$$

(6.3)

where  $q_j$  is j-th objective,  $g_j$  is a generic constant and  $f_{max}(q_j)$  is the maximum possible value of  $q_j$  for j = 1..n. Furthermore, it holds that  $q_j$  is preferred objective over  $q_{j-1}$ . One can observe that the objectives are mutually disjunctive.

The standard fitness function for circuit evolution (Equation 3.1) can be redefined ac-

cording to Equation 6.2 as follows:

$$fitnessp'_{2} = 1 + \bar{b}.g'_{2} + z.g_{1} = 1 + \bar{b}.(n_{c}.n_{r} + 1) + z,$$

$$= 1 + \bar{b}.n_{c}.n_{r} + \bar{b} + z;$$

$$g_{1} = 1,$$

$$g'_{2} = (f_{max}(z) + 1).g'_{1} = n_{c}.n_{r} + 1,$$

$$(6.4)$$

where  $\bar{b}$  is the number of incorrect bits obtained for all possible input combinations; z is the number of utilized gates; and  $n_c.n_r$  is the total number of programmable elements. The number of incorrect bits,  $\bar{b}$ , can be understood as Hamming distance between the truth table of the candidate circuit and the truth table of the desired circuit.