Received 12 July 2023, accepted 29 August 2023, date of publication 4 September 2023, date of current version 11 September 2023. Digital Object Identifier 10.1109/ACCESS.2023.3311518

# **RESEARCH ARTICLE**

# 0.3-V, 357.4-nW Voltage-Mode First-Order Analog Filter Using a Multiple-Input VDDDA

# FABIAN KHATEB<sup>®1,2,3</sup>, MONTREE KUMNGERN<sup>®4</sup>, TOMASZ KULEJ<sup>®5</sup>, VIERA STOPJAKOVA<sup>6</sup>, AND COSTAS PSYCHALINOS<sup>107</sup>, (Senior Member, IEEE) <sup>1</sup>Department of Microelectronics, Brno University of Technology, 601 90 Brno, Czech Republic

<sup>2</sup>Faculty of Biomedical Engineering, Czech Technical University in Prague, 272 01 Kladno, Czech Republic

<sup>3</sup>Department of Electrical Engineering, University of Defence, 662 10 Brno, Czech Republic

<sup>4</sup>Department of Telecommunications Engineering, School of Engineering, King Mongkut's Institute of Technology Ladkrabang, Bangkok 10520, Thailand

<sup>5</sup>Department of Electrical Engineering, Częstochowa University of Technology, 42-201 Częstochowa, Poland

<sup>6</sup>Institute of Electronics and Photonics, Faculty of Electrical Engineering and Information Technology, Slovak University of Technology in Bratislava, 811 07

Bratislava, Slovakia

<sup>7</sup>Electronics Laboratory, Physics Department, University of Patras, 265 04 Patras, Greece

Corresponding author: Montree Kumngern (montree.ku@kmitl.ac.th)

This work was supported in part by the University of Defence, Brno, within the Organization Development Project VAROPS, and in part by the Slovak Research and Development Agency under Grant APVV-19-0392.

**ABSTRACT** In this paper, a new versatile first-order voltage-mode analog filter using a single multiple-input voltage differencing differential difference amplifier for extremely low-voltage supply and low-frequency applications is presented. Using multiple-input MOS transistor technique, the filter can realize the first-order transfer functions of non-inverting and inverting low-pass, high-pass, and all-pass filters in a single topology with high input and low output impedance. This is particularly useful for voltage-mode circuits. The filter's pole frequency can be controlled electronically. The filter was used to implement a new quadrature oscillator to confirm its advantages. The multiple-input was applied to bulk-driven differential pairs operating in weak inversion; therefore, the proposed circuit operated from a supply voltage of 0.3 V and consumed 357.4 nW. The circuit was designed in the Cadence program using 0.13  $\mu$ m UMC CMOS technology. The performance and robustness of the design was validated by intensive simulations, including Monte Carlo and Process, Voltage and Temperature corner analyses.

**INDEX TERMS** Voltage differencing differencial difference amplifiers, analog filters, first-order filters, ultra-low power circuits.

## I. INTRODUCTION

The active building block called a voltage differencing differential difference amplifier (VDDDA) was first introduced in [1]. This device has the advantages of an operational transconductance amplifier, such as the possibility of electronic tuning, and of a differential difference current conveyor (DDCC), such as the possibility of arithmetic operations in voltage mode. Unlike the differential difference transconductance amplifier (DDTA), which has high input and output impedance, the VDDDA is more suitable for voltage-mode operation and filter cascading due to its high input and low output impedance [1], [2], [3], [4], [5], [6], [7], [8]. VDDDA has been successfully used in various applications reported

The associate editor coordinating the review of this manuscript and approving it for publication was Yuh-Shyan Hwang<sup>10</sup>.

in the literature [1], [2], [3], [4], [5], [6], [7], [8]. The utility of VDDDA with conventional CMOS structure was demonstrated in [1] on a novel first-order resistorless voltagemode all-pass filter and in the design of a voltage-mode quadrature oscillator with a supply voltage of  $\pm 0.9$  V and a power consumption of 0.99 mW. In [2], the VDDDA was used to implement a universal voltage-mode filter using commercially available integrated circuits (LT1228 from Linear Technology Inc. and AD830 from Analog Device Inc.) with a supply voltage of  $\pm 5$  V. In [3], a VDDDA-based voltagemode shadow filter with a conventional CMOS structure and a supply voltage of  $\pm 0.9$  V was presented. Reference [4] presents an electronically tunable quadrature sinusoidal oscillator based on VDDDA with commercially available integrated circuits and a supply voltage of  $\pm 5V$ . In [5], the implementation of a grounded inductance simulator using

a single VDDDA with a conventional CMOS structure and a supply voltage of  $\pm 0.9$  V and a power consumption of 127  $\mu$ W was presented. In [6], a capacitive multiplier implementation using a VDDDA with commercially available ICs and a voltage of  $\pm 5$  V was used. In [7], a universal filter based on a compact multiple-input gate-driven CMOS VDDDA structure with a supply voltage of  $\pm 0.9$  V and a power consumption of 0.99 mW was presented. In [8], an analog current mode VDDDA filter using 32 nm CNTFET technology, conventional CMOS topology with  $\pm 0.9$  V supply and 166  $\mu$ W power consumption was used. As mentioned above, the VDDDA CMOS structures in [1], [3], and [5] are standard and not innovative. All VDDDAs [1], [2], [3], [4], [5], [6], [7], [8] are incompatible with extremely low supply voltage and low power consumption, which makes them impossible to use in extremely low voltage applications powered by batteries or power harvesting sources.

Low-voltage, low-power CMOS analog circuits are an important design consideration in modern portable and battery-powered electronics, sensors, and in biomedical and energy harvesting applications where energy efficiency is critical to maximize uptime. Ultra-low voltage circuits typically operate with a supply voltage  $(V_{DD})$  around or even below the threshold voltage  $(V_{TH})$  of a single MOS transistor, i.e.  $V_{DD} < V_{TH}$ . They use specialized and unconventional design techniques to operate reliably at such extremely low supply voltages while maintaining acceptable performance specifications such as input common mode range, gain, bandwidth, and noise. Techniques such as the following are widely used in literature to achieve low-voltage operation: weak inversion MOS transistors, bulk-driven (BD), multiple-input floating-gate (MIFG), quasi-floating-gate (QFG), multipleinput MOS transistors (MI-MOST), self-cascode MOS transistors, which are widely used in the literature [9], [10], [11], [12], [13], [14], [15], [16], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26]. Low power consumption can be achieved through the minimization of the number of active components and reduction of their operating voltages and currents.

For first-order filters, three filter functions can be implemented, namely a low-pass (LP) filter, a high-pass (HP) filter, and an all-pass (AP) filter. These first-order filters can be used in signal processing, for example, as high-order filters, sinusoidal oscillators, frequency-selective filters with a quality factor, group delay filters, or phase equalizers [27], [28], [29], [30]. There are many versatile first-order filters in the literature that can implement LP, HP, and AP filters from a single topology. This paper focuses on first-order voltage-mode universal filters. These filters should provide high input and low output impedance, which is valuable for voltage-mode circuits. First-order voltage-mode and mixed-mode filters have been published in the open literature [31], [32], [33], [34], [35], [36], [37], [38], [39], [40], [41], [42], [43], [44], [45], [46], [47], [48], [49], [50]. The filters in [31], [32], [35], [37], [38], [39], [41], and [50] use capacitors and/or resistors into the input signal path, which is not ideal for cascading voltagemode circuits. In [33], [34], and [36], some filter functions do not provide low output impedance. The filters in [13], [14], [15], [16], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26], [27], [28], [29], [30], [31], [31], [32], [32], [33], [33], [34], [34], [35], [35], [36], [36], [37], [37], [38], [39], [39], [40], [40], [41], [42], [43], [44], [45], and [46] offer only three transfer functions of LP, HP, AP filters. The filters in [38] and [41] offer voltage-gain of transfer functions; however, they offer only four transfer functions of LP, HP, AP filters (noninverting and inverting AP). Although the filter in [47] can provide all first-order noninverting and inverting universal responses, the circuit uses two differential voltage-current conveyors (DVCCs). Filters including voltage mode (VM), trans-admittance mode (TAM), current mode (CM), and trans-impedance mode (TIM) are described in [48], [49], and [50], but the VM of these filters only provides three transfer functions of LP, HP, AP filters. It should be noted that the universal filters in [31], [32], [33], [34], [35], [36], [37], [38], [39], [40], [41], [42], [43], [44], [45], [46], [47], [48], [49], and [50] are implemented using high-power supply (i.e., >1 V) and high-power consumption devices, which are not suitable for low-power signal processing applications.

This paper introduces the multiple-input VDDDA (MI-VDDDA). It incorporates several design techniques such as a bulk-driven MOS transistor operating in weak inversion to minimize the voltage supply and achieve the ability to operate at  $V_{DD}$  lower than  $V_{TH}$ . In addition, the MI-MOST technique is used to minimize the number of active components by maintaining a single differential pair, thus reducing power consumption. As a result, the circuit can operate at 0.3 V, 357.4 nW while providing a rail-to-rail input voltage range. The MI-VDDDA was used to implement the first-order transfer functions of non-inverting and inverting low-pass, high-pass and all-pass filters in a single topology with high input and low output impedance. Thus, it is ideally suited for voltage-mode circuits. The rest of this paper is organized as follows: in Section II, the CMOS structure of the MI-VDDDA and the proposed first-order universal voltage filter are presented, and their theoretical description is given. In Section III, an example application of the quadrature oscillator is presented. Intensive simulation results of the filter and oscillator are presented in Section IV, while Section V concludes this paper.

# **II. PROPOSED CIRCUIT**

#### A. THE MI-VDDDA

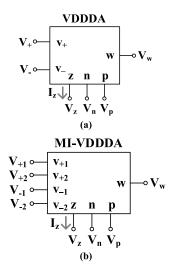

Fig. 1 (a) shows the symbol of the conventional voltage differencing differential difference amplifier (VDDDA) that was introduced in [1]. This device is composed of a transconductance amplifier (TA) as a first stage, followed by a differential difference current conveyor (DDCC) as a second stage. The port characteristic of the conventional VDDDA in Fig. 1 (a) can be expressed by:

$$I_{z} = g_{m} (V_{+} - V_{-}) V_{w} = V_{z} - V_{n} + V_{p}$$

(1)

FIGURE 1. Symbol of (a) a conventional VDDDA, (b) the proposed MI-VDDDA.

This device has a high-impedance differential voltage input  $V_+$  and  $V_-$ , a high-impedance current output z, high-impedance voltage inputs  $V_n$  and  $V_p$ , and a low-impedance voltage output w. The differential voltage  $V_+-V_-$  is transferred to the current output  $I_z$  with the transconductance  $g_m$ .

Fig. 1 (b) shows the electrical symbol of the multiple-input VDDDA proposed in this work. Its port characteristics are like those of the conventional VDDDA [1], except for a differential voltage input. The proposed MI-VDDDA has multiple differential voltage inputs; thus, its operation can be expressed as:

$$I_{z} = g_{m} \left( V_{+1} - V_{-1} + \ldots + V_{+(n)} - V_{-(n)} \right)$$

$$V_{w} = V_{z} - V_{n} + V_{p}$$

(2)

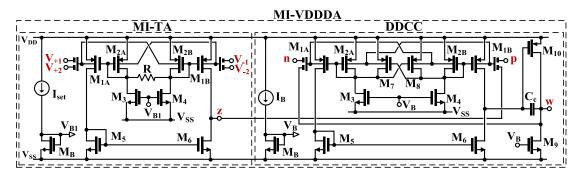

Fig. 2. shows the CMOS implementation of the proposed MI-VDDDA. The multiple-input MOS transistor (MOST) technique [24], [26], as shown in Fig. 3 (a)-(c), is used to realize this multiple input device; hence, the MI-VDDDA is realized without increasing the number of active components by maintaining one differential pair and preserving the same power consumption. Unlike the low-voltage DDTA (DDCC followed by TA) presented in [25], the proposed MI-VDDDA is a multiple-input TA (MI-TA) followed by DDCC. This provides a high-input, low-output impedance active block suitable for voltage-mode applications. Thanks to the MI-MOST technique that used for both, the differential pair of the TA and DDCC, the input terminals and the versatility of the MI-VDDDA is increased.

The adapted transconductance amplifier is based on the non-tailed differential pair  $M_{1A,B}$  and  $M_{2A,B}$ , biased by the current sinks  $M_3$  and  $M_4$  and the linearization resistance *R*. The transistors  $M_5$  and  $M_6$  operate as active load and provide single-ended output for the TA. The non-tailed architecture allows the device to operate from a very low supply voltage. The basic form of the amplifier, i.e., without MI transistors at the input, was first proposed and validated experimentally

using 0.13  $\mu$ m technology in [11]. Here, the input transistors M<sub>1A</sub> and M<sub>1B</sub> were replaced by MI devices, thus realizing a mathematical summing of the input voltages  $V_1$  and  $V_2$ , as described by the first equation of (2).

Assuming equal capacitances  $C_B$  in the input transistors (see Fig.3.b) for frequencies where the voltage gain of the input capacitive divider is determined by the capacitances  $C_B$ only (i.e.,  $1/\omega C_B \ll R_{MOS}$ ), the circuit transconductance is given by:

$$g_m = \beta_1 g_{mo} \tag{3}$$

where  $\beta_1 = 1/2$  is the attenuation factor for the input capacitive divider and  $g_{mo}$  is the transconductance of the TA determined from the bulk terminals of M<sub>1A</sub> and M<sub>1B</sub> [11]:

$$g_{mo} = 2g_{mb1,2} \frac{R + \frac{1}{g_{m1,2}}}{R + \frac{2}{g_{m1,2}}}$$

(4)

where  $g_{m1,2}$  is the transconductance of the input transistors  $M_{1A,B}$  and  $M_{2A,B}$  (assumed identical) and  $g_{mb1,2}$  is their bulk transconductance.

As shown in [11], the circuit linearity depends on the value of the linearization resistance R, and optimum linearity is achieved if the following condition is met:

$$R = \frac{1}{g_{m1,2}} \tag{5}$$

Note that the circuit linearity remains good even for relatively large incompatibilities between R and  $1/g_{m1,2}$ , allowing transconductance tuning. Moreover, in the proposed circuit, the input capacitive divider further increases the linear range of the TA. For optimal linearity, the circuit transconductance is given by:

$$g_m = \beta_1 \frac{4}{3} \cdot \eta \frac{1}{R} \tag{6}$$

where  $\eta = g_{mb1,2}/g_{m1,2}$  is the bulk to gate transconductance ratio for the input transistors at the operating point. Due to the non-cascode structure of the TA, the voltage gain of the circuit is relatively low and can be expressed as:

$$A_{VTA} = g_m \left( r_{ds1,2} || r_{ds5,6} \right) \tag{7}$$

The second block of the proposed MI-VDDDA is the differential-difference current conveyor. The DDCC is a twostage structure, where the first stage is a differential difference amplifier ( $M_1$ - $M_6$ ). The two differential input ports were realized using MI devices, eliminating the need for a second pair of transistors, and thus simplifying the overall structure and saving power. The core of the input stage (with conventional transistors at the inputs) was first proposed in [9] and validated experimentally in [10]. It consists of a non-tailed differential pair with partial positive feedback (PPF), introduced by the cross-coupled transistors  $M_7$  and  $M_8$ . The PPF circuit was introduced to improve the voltage gain of the first

FIGURE 2. CMOS structure of the multiple-input VDDDA.

FIGURE 3. MI-BD MOST: (a) symbol, (b) realization, and (c) possible implementation of  ${\rm R}_{\rm MOS}.$

stage, which, neglecting the input capacitive divider, can be expressed as:

$$A_{v1} = \frac{2g_{mb1,2}}{1-m} \left( r_{ds1} || r_{ds5} \right) \tag{8}$$

where the coefficient  $m = g_{m7,8}/g_{m1,2}$ .

The second stage of the DDCC is a common-source amplifier based on the transistor  $M_{10}$  loaded by the current sink based on  $M_9$ , with a voltage gain of:

$$A_{v2} = g_{m10} \left( r_{ds9} || r_{ds10} \right) \tag{9}$$

The overall voltage gain of the DDCC can be expressed as:

$$A_{\nu} = \frac{\beta_2 A_{\nu 1} A_{\nu 2}}{1 + \beta_2 A_{\nu 1} A_{\nu 2}} \tag{10}$$

where  $\beta_2 = 1/2$  is the voltage gain of the input capacitive divider at the bulk terminals of M<sub>1,2</sub>. Due to the relatively high value of the open-loop gain ( $\beta_2 A_{\nu 1} A_{\nu 2}$ ), the voltage gain  $A_{\nu}$  is very close to unity, as is required in this application.

The circuit stability in closed loop configuration is provided by the capacitance  $C_C$ , and the GBW product of the DDCC is given by:

$$GBW = \beta_2 \frac{2g_{mb1,2}}{(1-m) C_C}$$

(11)

As in other two-stage amplifiers, the GBW product in practice is limited by the frequency of the output pole  $(g_{m10}/C_{Lw})$ , which depends on the load capacitance of the w terminal  $(C_{Lw})$  and should not exceed around a half of this frequency.

The output resistance of the DDCC (MI-VDDDA), seen from the w terminal, can be approximated as:

$$r_{outW} \cong \frac{1}{\beta_2 A_{\nu 1} g_{m 10}} \tag{12}$$

VOLUME 11, 2023

Thus, it is equal to the reciprocal value of  $g_{m10}$  multiplied by the voltage gain of the first stage, which makes it possible to obtain a relatively low value of this resistance.

It should be noted here that although the presented VDDDA in Fig. 2 appears to be somewhat more complex compared to the conventional VDDDA design, it can operate with extremely low supply voltages, even much lower than the threshold voltage of a single MOS transistor (i.e.,  $V_{DD} =$  $0.3 < V_{TH} = 0.5V$ ). The proposed block offers suitable parameters for low-frequency applications, such as rail-torail input voltage range, high linearity, and low power consumption. Furthermore, using MI-MOST simply increases the number of VDDDA inputs without the need for additional input differential pairs that result in additional power consumption and CMOS structure complexity. Ultimately, an MI-VDDDA based application is less complex with a minimum number of active blocks compared to an application using a conventional VDDDA structure. It is worth noting here that the circuit is intended for low frequency applications, such as biosignal processing. The spectrum of these biosignals ranges from sub-hertz to 10 kHz.

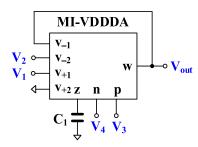

# B. PROPOSED VOLTAGE-MODE FIRST-ORDER UNIVERSAL ANALOG FILTER

Fig. 4 shows the proposed voltage-mode first-order universal filter using MI-VDDDA. The proposed first-order filter with four-inputs and one-output employs one MI-VDDDA and one grounded capacitor. The input signals  $V_1$ ,  $V_2$ ,  $V_3$ , and  $V_4$  supply through the high-impedance terminals  $V_{+1}$ ,  $V_{-2}$ , p, and n of the MI-VDDDA. The output signal  $V_{out}$  is connected to the low-impedance terminal w of the MI-VDDDA. Therefore, the proposed filter provides high-input impedance and low-output impedance which is optimal for voltage-mode circuits.

Using (2) and nodal analysis, the output voltage of Fig. 4 can be expressed by:

$$V_{out} = \frac{sC_1 (V_3 - V_4) + g_m (V_1 - V_2)}{sC_1 + g_m}$$

(13)

From (13), the first-order LP, HP, and AP filters can be obtained by appropriately applying the input signals. The variant filtering functions of first-order filters are shown in Table 1. It is evident from Table 1 that both non-inverting and

FIGURE 4. Proposed voltage-mode first-order universal analog filter.

| Fil | tering Function              | Input                | Transfer Function                             |  |  |

|-----|------------------------------|----------------------|-----------------------------------------------|--|--|

| LP  | Non-inverting                | $V_1 = V_{in}$       | $H(s) = \frac{g_{m1}}{sC_1 + g_{m1}}$         |  |  |

|     | Inverting                    | $V_2 = V_{in}$       | $H(s) = -\frac{g_{m1}}{sC_1 + g_{m1}}$        |  |  |

| HP  | Non-inverting                | $V_3 = V_{in}$       | $H(s) = \frac{sC_1}{sC_1 + g_{m1}}$           |  |  |

|     | Inverting                    | $V_4 = V_{in}$       | $H(s) = -\frac{sC_1}{sC_1 + g_{m1}}$          |  |  |

| AP  | Non-inverting<br>(phase lag) | $V_1 = V_4 = V_{in}$ | $H(s) = -\frac{sC_1 - g_{m1}}{sC_1 + g_{m1}}$ |  |  |

|     | Inverting<br>(phase lead)    | $V_2 = V_3 = V_{in}$ | $H(s) = \frac{sC_1 - g_{m1}}{sC_1 + g_{m1}}$  |  |  |

TABLE 1. Obtaining variant filtering functions of the first-order analog filter.

inverting transfer functions of LP, HP, and AP filters can be obtained from Fig. 4. The proposed multiple-input universal filter with high-input impedance does not require additional circuits, such as buffer circuits, nor does it require inverting amplifiers to generate inverting input signals.

The pole frequency  $(\omega_o)$  of all filters can be given by:

$$\omega_o = \frac{g_m}{C_1} \tag{14}$$

Thus, the pole frequency of the filters can be electronically controlled using  $g_m$  via the bias current of the MI-VDDDA.

#### C. NON-IDEALITY ANALYSIS

This section shows the effect of the non-ideality of the MI-VDDDA on the performances of the proposed first-order filter. Because the proposed MI-VDDDA is expected to work within a limited operating frequency, the parasitic parameters at the input and output terminals of the MI-VDDDA, such as impedances and capacitances, are absent from consideration. There are two non-ideal characteristics that are considered: the transconductance gain error  $(g_{mn})$  and voltage gain errors  $(\beta)$ . Thus, the terminal relationships in (2) can be rewritten as:

$$I_{z} = g_{mn} \left( V_{+1} - V_{-1} + \dots + V_{+(n)} - V_{-(n)} \right) V_{w} = \beta_{z} V_{z} - \beta_{n} V_{n} + \beta_{p} V_{p}$$

(15)

FIGURE 5. Proposed quadrature oscillator circuit using MI-VDDDA-based all-pass filter.

where  $g_{nn}$  is the transconductance gain error and  $\beta_z$ ,  $\beta_n$ , and  $\beta_p$  are the voltage gain errors from the z-, n-, and p-terminals to the w-terminal. Ideally, these voltage gains are equal to unity. In the frequency range near its cutoff frequency, the transconductance gain error can be expressed by [51]:

$$g_{mn} \cong g_m \left(1 - \mu s\right) \tag{16}$$

where  $\mu = 1/\omega_{gm}$ ,  $\omega_{gm}$  denotes the first-order pole. Using (15), (13) can be rewritten as:

$$V_{out} = \frac{sC_1 \left(\beta_p V_3 - \beta_n V_4\right) + \beta_z g_{mn} \left(V_1 - V_2\right)}{sC_1 + \beta_z g_{mn}}$$

(17)

Thus, the inverting and non-inverting transfer functions of LP, HP, and AP filters can be rewritten respectively as

$$H(s) = \frac{\beta_{z}g_{mm}}{sC_1 + \beta_{z}g_{mm}}$$

$$H(s) = -\frac{\beta_{z}g_{mm}}{sC_1 + \beta_{z}g_{mm}}$$

$$(18)$$

$$H(s) = \frac{\beta_p s C_1}{s C_1 + \beta_z g_{ggn}}$$

$$H(s) = -\frac{\beta_p s C_1}{s C_1 + \beta_z}$$

$$(19)$$

$$H(s) = -\frac{\beta_n sC_1 - \beta_z g_{mn}}{sC_1 + \beta_z g_{mn}}$$

$$H(s) = \frac{\beta_p sC_1 - \beta_z g_{mn}}{sC_1 + \beta_z g_{mn}}$$

$$(20)$$

Using (15), the denominator (D(s)) of these transfer functions can be expressed as:

$$D(s) = sC_1 \left(1 - \frac{\beta_z \mu g_m}{C_1}\right) + \beta_z g_m \tag{21}$$

It can be made negligible by satisfying the following condition:

$$\frac{\beta_z \mu g_m}{C_1} \ll 1 \tag{22}$$

The pole frequency in (14) becomes:

$$\omega_o = \frac{\beta_z g_m}{C_1} \tag{23}$$

It follows from (18)-(20) and (23) that the non-idealities of the MI-VDDDA slightly affect the circuit characteristics.

If consider the parasitic effect on the VDDDA [7], the parasitic impedances at z-terminal  $(R_z//C_z)$  and w-terminal  $(R_w)$  will be considered. The parasitic capacitance can be minimized by setting the value of  $C_1 \gg C_z$  while the parasitic resistance  $R_z$  can be minimized by setting the value of

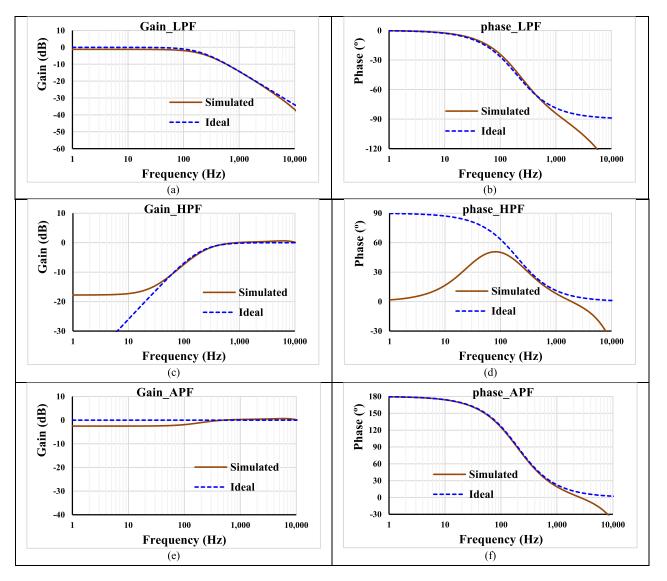

FIGURE 6. Gain and phase characteristics: (a,b) LPF; (c,d) HPF; (e,f) APF.

$1/g_m \gg R_z$ , the parasitic resistance  $R_w$  can be minimized by using the value of load resistance  $R_L$  higher than  $R_w$  $(R_L > R_w)$ . Usually,  $R_w$  of VDDDA is low. Note, that the effect of parasitic impedance, which occurs at much higher frequencies than the bio-signals has negligible effect on the performance of the application.

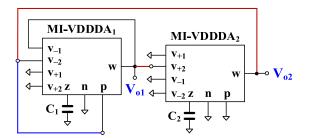

### **III. APPLICATION EXAMPLE**

Fig. 5 shows the proposed quadrature oscillator circuit using the MI-VDDDA-based first-order all-pass filter. The circuit consists of an inverting first-order AP filter (MI-VDDDA<sub>1</sub> and  $C_1$ ) and a lossless integrator (MI-VDDDA<sub>2</sub> and  $C_2$ ).

The nodes  $V_{o1}$  and  $V_{o2}$  of the circuit possess a low impedance level, hence loads can be directly connected without buffer circuits. Using the transfer function of the inverting AP filter from Table 1 and letting the unity loop (LG) gain (LG=1), we obtain:

$$\left(\frac{sC_1 - g_{m1}}{sC_1 + g_{m1}}\right) \left(\frac{g_{m2}}{sC_2}\right) = 1$$

(24)

The characteristic equation of the oscillator can be given by:

$$s^{2}C_{1}C_{2} + s\left(C_{2}g_{m1} - C_{1}g_{m2}\right) + g_{m1}g_{m2} = 0$$

(25)

Letting  $g_{m1} = g_{m2}$ , the condition of oscillation can be given as:

$$C_2 = C_1 \tag{26}$$

The frequency of oscillation is:

$$\omega_o = \sqrt{\frac{g_{m1}g_{m2}}{C_1 C_2}} \tag{27}$$

The condition of oscillation can be given by  $C_1$  and  $C_2$  whereas the frequency of oscillation can be controlled electronically by  $g_m(g_m = g_{m1} = g_{m2})$ . The proposed oscillator

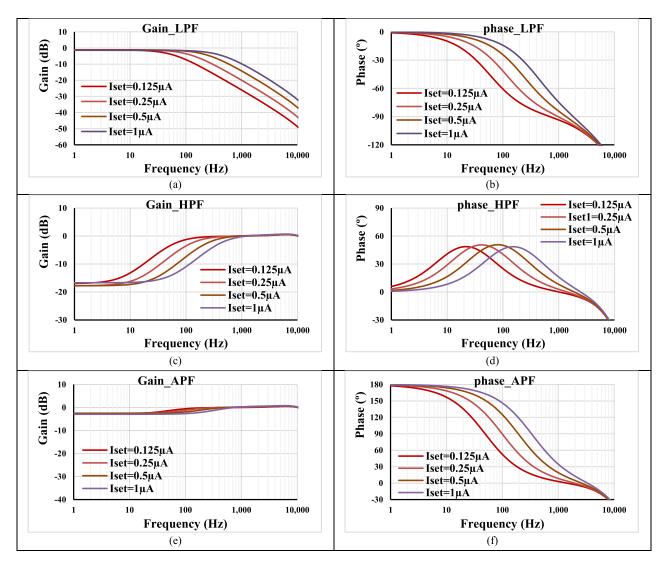

FIGURE 7. Gain and phase characteristics: (a,b) LPF; (c,d) HPF; (e,f) APF with various I<sub>set</sub>.

also possesses orthogonally controlled condition and frequency of oscillation. Considering the MI-VDDDA<sub>2</sub> and  $C_2$ are composed as a lossless integrator, the transfer function between nodes  $V_{o2}$  and  $V_{o1}$  can be expressed by:

$$\frac{V_{o2}}{V_{o1}} = \frac{g_{m2}}{sC_2}$$

(28)

At oscillating frequency  $(\omega_o)$ , the magnitude of the signal is  $|g_{m2}/C_2|$  and the phase difference between  $V_{o1}$  and  $V_{o2}$  is 90°.

## **IV. SIMULATION RESULTS**

The Cadence Virtuoso Analog Design Environment, using 130 nm CMOS technology from UMC, was used to design the circuit. Table 2 includes the transistor aspect ratio of the MI-VDDDA and values of passive components. The voltage supply was 0.3 V ( $\pm 0.15$ V), the nominal value of the setting current was  $I_{set} = 0.5 \ \mu$ A, the bias current  $I_B = 50$  nA, and the nominal power consumption of the

96642

TABLE 2. Transistor aspect ratios and passive components of the MI-VDDDA.

| Device                                 | W/L (μm/μm)             |  |

|----------------------------------------|-------------------------|--|

| $M_{1A}, M_{2A}, M_{1B}, M_{2B}$       | 20/3                    |  |

| M <sub>7</sub> , M <sub>8</sub>        | 15/3                    |  |

| $M_3$ - $M_6$ , $M_B$                  | 10/3                    |  |

| M <sub>9</sub>                         | $6 \times 10/3$         |  |

| M <sub>10</sub>                        | $6 \times 20/3$         |  |

| M <sub>R</sub>                         | 5/3                     |  |

| MIM capacitor: $C_B = 0.2$ pI          | $F, C_c = 4 \text{ pF}$ |  |

| Poly-resistor $R = 90 \text{ k}\Omega$ |                         |  |

MI-VDDDA was 357.4 nW. The MI-TA linear resistor's R was a high-resistance poly-resistor. The input and compensation capacitors were highly linear metal-isolator-metal capacitors (MIM). The open-loop gain of the DDCC (i.e. without the unity gain feedback) was simulated as 73.9 dB and the phase margin was 56.2° for 20 pF load capacitor. The low-frequency gain for  $V_w/V_p$  and  $V_w/V_n$  is 14 mdB

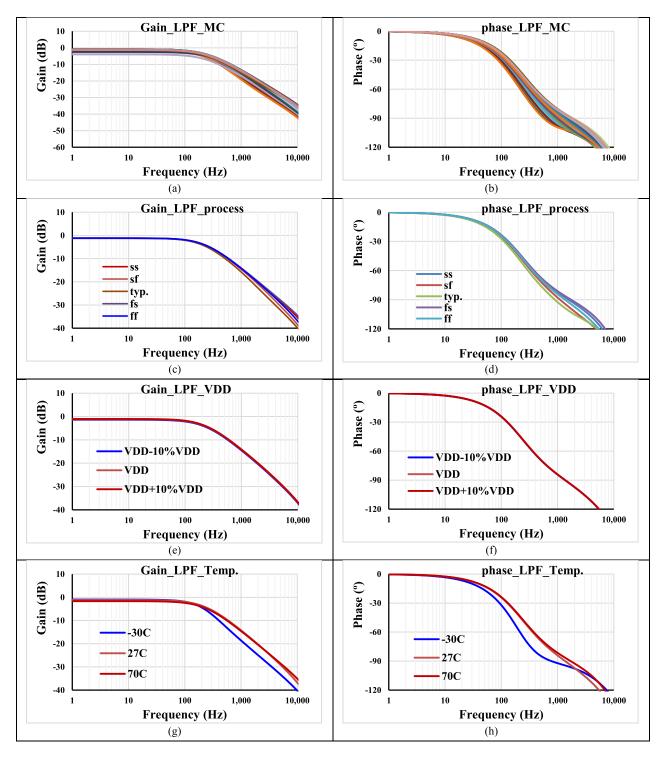

FIGURE 8. Frequency responses of gain and phase for LPF: (a,b) MC; (c,d) process corners; (e,f) voltage supply corners; (g,h) temp. corners.

and 57.29 mdB while the -3dB bandwidth is 22.24 kHz and 22.23 kHz, respectively. The simulated DC transfer characteristics of the DDCC shows rail-to-rail operation capability. The simulated gain and phase characteristics for the TA (without MI) and  $I_{set} = 0.5 \ \mu$ A and 20 pF load capacitance shows that the low DC gain is 23.2 dB and the bandwidth

is 19.65 kHz while the phase error is  $3.8^{\circ}$  [11]. The DC characteristic of the output current and the transconductance of the TA versus fully differential input voltage for  $I_{set} = 0.125 \ \mu\text{A}$ , 0.25  $\ \mu\text{A}$ , 0.5  $\ \mu\text{A}$  confirms a rail-to-rail operation with high linearity. To the best of the authors' knowledge, this is the first VDDDA with the lowest supply voltage presented

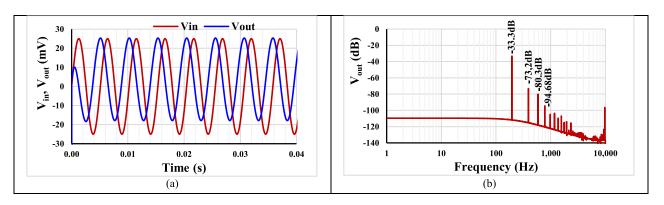

FIGURE 9. The transient response of the APF (a) and the spectrum of the V<sub>out</sub> using FFT (b).

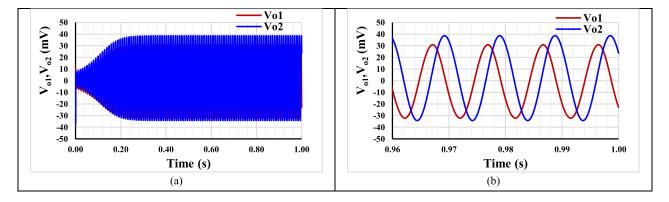

**FIGURE 10.** The running oscillation (a) and the steady state (b).

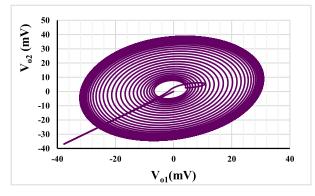

**FIGURE 11.** The quadrature relationship between  $V_{01}$  and  $V_{02}$ .

in the literature. Despite the extremely low supply voltage, the circuit offers rail-to-rail operation capability and high linearity.

The proposed voltage-mode first-order universal filter from Fig. 4 was simulated with  $C_1 = 1$  nF and the setting current  $I_{set} = 0.5 \ \mu A \ (g_m = 1.25 \ \mu S)$ . Fig. 6 shows the ideal and simulated filter gain and phase characteristics. The designed and simulated cut-off frequencies were very close i.e., 197.4 Hz and 195.6 Hz, respectively.

The electronic turnability of the filter is confirmed in Fig. 7. The gain and phase characteristics were repeated for

96644

$C_1 = 1$  nF and various  $I_{set} = (0.125, 0.25, 0.5, 1) \mu$ A. The cut-off frequency was (50, 100, 195.6, 332) Hz, respectively.

The filter performance was evaluated under varying process and mismatch conditions using Monte Carlo (MC) analysis and under the effects of process, voltage, and temperature (PVT) corners. Fig. 8 shows the gain and phase characteristics of the LPF for  $C_1 = 1$  nF and  $I_{set} = 0.5 \ \mu$ A, with: (a,b) 200 runs Monte Carlo analysis; (c,d) process slow-slow (ss), slow-fast (sf), fast-slow (fs) and fast-fast (ff); (e,f) voltage supply corners  $V_{DD} \pm 10\% V_{DD}$ ; (g,h) temperature corners -30°C and 70°C. As it is evident, the curves are almost overlapped, ensuring reliable operation under the range of the operating conditions. The slight deviation in the temperature corners analysis is expected due the operation in weak inversion that is sensitive to temperature variation.

The transient response of the APF with  $C_1 = 1$  nF and setting current  $I_{set} = 0.5\mu$ A is shown in Fig. 9 (a). The input of the filter  $V_{in}$  was supplied by a sine wave signal with 50 mV<sub>pp</sub>@ 195 Hz. Fig. 9 (b) shows the spectrum of the output signal  $V_{out}$  using Fast Fourier Transform (FFT). The total harmonic distortion of  $V_{out}$  was found to be -39.09 dB (1.1%).

To start the oscillation of the oscillator in Fig.5, the following values were selected: capacitors  $C_1 = C_2 = 1$  nF, the setting current  $I_{set2} = 0.5 \ \mu$ A, and  $I_{set1} = 0.22 \ \mu$ A. Fig. 10 (a) and (b) shows the running oscillation and steady

Sim

| Features                                   | Proposed        | [38] 2021       | [40] 2022       | [44] 2022    | [50] 2023       | [52] 2023       |

|--------------------------------------------|-----------------|-----------------|-----------------|--------------|-----------------|-----------------|

| Active and passive elements                | 1 VDDDA, 1      | 1 LT1228, 1     | 2 CFOA, 1 C,    | 2 CFOA, 1 C, | 1 VGA, 1 R, 1   | 2 OTA, 1 C      |

| *                                          | С               | C, 2 R          | 4 R             | 4 R          | C               |                 |

| Realization                                | CMOS            | Commercial      | CMOS            | Commercial   | CMOS            | CMOS            |

|                                            | structure (0.13 | IC (LT1228)     | structure (0.18 | IC (AD844)   | structure (0.18 | structure (0.18 |

|                                            | μm)             |                 | μm)             |              | μm)             | μm)             |

| Mode operation                             | VM              | VM              | VM              | VM           | MM              | VM              |

| Type of filter                             | MISO            | MISO            | SIMO            | MISO         | MIMO            | MISO            |

| Number of filtering functions              | 6 (LP+, LP-,    | 4 (LP+, HP+,    | 3 (LP+, HP+,    | 3 (LP-, HP+, | 3 VM (LP+,      | 6 (LP+, LP-,    |

|                                            | HP+, HP-,       | AP+, AP-)       | AP+)            | AP+)         | HP+, AP+)       | HP+, HP-,       |

|                                            | AP+, AP-)       |                 |                 |              |                 | AP+, AP-)       |

| High-input & low-output impedances         | Yes & Yes       | No & Yes        | Yes & No        | Yes & Yes    | No/Yes (VM)     | Yes & No        |

| Electronic control of parameter $\omega_o$ | Yes             | Yes             | No              | No           | Yes             | Yes             |

| Using grounded capacitor/resistor          | Yes/Yes         | No/No           | Yes/No          | Yes/No       | No/Yes          | Yes/Yes         |

| Pole frequency (kHz)                       | 0.197           | 90              | 1591.5          | 159          | 1590            | 0.220           |

| Total harmonic distortion (%)              | 1.1@50mVpp      | $1@200 mV_{pp}$ | 1@200mVpp       | -            | 0.15@40mVpp     | 0.36@40mVpp     |

|                                            |                 |                 |                 |              | (VM)            |                 |

| Power supply voltages (V)                  | 0.3             | ±5              | ±1.25           | ±12          | ±0.9            | 0.5             |

| Power consumption (µW)                     | 0.3574          | 57600           | 3910            | -            | 1310            | 0.0595          |

| Applications                               | QSO             | QSO             | QSO             | -            | QSO             | High-Q BPF      |

| Verification of result                     | Sim.            | Exp.            | Sim./Exp.       | Exp.         | Sim/Exp         | Post-layout     |

TABLE 3. Comparison of the proposed first-order filter and some previous works.

Note: QSO = quadrature sinusoidal oscillator, High-Q BPF = high-Q bandpass filter, MISO = multiple-input single-output, SIMO = single-input multipleoutput, MIMO = multiple-input multiple-output.

state of the oscillator, respectively. The THDs were around 0.8%. The outputs  $V_{o1}$  and  $V_{o2}$  were in quadrature with a frequency of 103 Hz. Fig. 11 shows the relation between  $V_{o1}$  and  $V_{o2}$  that confirms the quadrature relationship of the output signals.

Table 3 shows the comparison of the proposed first-order filter with some previous works, namely the recent publications in [38], [40], [44], [50], and [52]. Compared to [38], [40], [44], and [50], the proposed filter can realize more transfer functions and offers both lower supply voltage and lower power consumption. Like [52], the proposed filter offers six transfer functions, but the filter in [52] uses two OTAs and does not provide low-output impedance. The circuits in [38] and [50] excite the input signal via the capacitor, which is not ideal for voltage-mode circuits. Compared to [40] and [44], the proposed filter has an electronic tuning capability. Finally, the proposed circuit operates with the lowest voltage supply of 0.3V.

#### **V. CONCLUSION**

This paper presents a universal 0.3 V voltage-mode firstorder analog filter using a single multiple-input VDDDA. The CMOS structure of the MI-VDDDA is capable of operating at extremely low supply voltages without degrading circuit performance due to various design aspects. Thanks to the multiple-input technique, the first-order filter provides non-inverting and inverting low-pass, high-pass and all-pass filters in a single topology with high input and low output impedance. The filter circuit has been used to implement a quadrature oscillator. The robustness of the design is supported by intensive simulation results, such as MC and PVT corner analyses.

#### REFERENCES

- [1] N. Herencsar, R. Sotner, B. Metin, J. Koton, and K. Vrba, "VDDDA-new 'voltage differencing' device for analog signal processing," in Proc. 8th Int. Conf. Elect. Electron. Eng. (ELECO), Bursa, Turkey, 2013, pp. 17-20, doi: 10.1109/ELECO.2013.6713927.

- [2] P. Supavarasuwat, M. Kumngern, S. Sangyaem, W. Jaikla, and F. Khateb, "Cascadable independently and electronically tunable voltage-mode universal filter with grounded passive components," AEU Int. J. Electron. Commun., vol. 84, pp. 290-299, Feb. 2018, doi: 10.1016/j.aeue.2017.12.002.

- [3] P. Huaihongthong, A. Chaichana, P. Suwanjan, S. Siripongdee, W. Sunthonkanokpong, P. Supavarasuwat, W. Jaikla, and F. Khateb, "Single-input multiple-output voltage-mode shadow filter based on VDDDAs," AEU Int. J. Electron. Commun., vol. 103, pp. 13-23, May 2019, doi: 10.1016/j.aeue.2019.02.013.

- [4] D. Satipar, P. Intani, and W. Jaikla, "Electronically tunable quadrature sinusoidal oscillator using VDDDAs," in Proc. 9th Int. Electr. Eng. Congr. (iEECON), Pattaya, Thailand, Mar. 2021, pp. 353-356, doi: 10.1109/iEECON51072.2021.9440261.

- [5] M. Konal and F. Kacar, "Grounded inductance simulator realization with single VDDDA," Anal. Integr. Circuits Signal Process., vol. 110, no. 2, pp. 279-288, Feb. 2022, doi: 10.1007/s10470-021-01957-1.

- [6] W. Jaikla, P. Huaihongthong, S. Siripongdee, A. Chaichana, and P. Suwanjan, "Single active element based electronically controllable capacitance multiplier," J. Circuits, Syst. Comput., vol. 31, no. 10, Jul. 2022, Art. no. 2250175, doi: 10.1142/S0218126622501754.

- [7] W. Jaikla, F. Khateb, T. Kulej, and K. Pitaksuttayaprot, "Universal filter based on compact CMOS structure of VDDDA," Sensors, vol. 21, no. 5, p. 1683, Mar. 2021, doi: 10.3390/s21051683.

- [8] Y. Ozcelep, I. Mamatov, and F. Kacar, "VDDDA based low power filter using 32 nm CNTFET technology," Anal. Integr. Circuits Signal Process., vol. 112, pp. 391-399, May 2022, doi: 10.1007/s10470-022-02043-w

- [9] T. Kulej, "0.4-V bulk-driven operational amplifier with improved input stage," Circuits, Syst., Signal Process., vol. 34, no. 4, pp. 1167-1185, Apr. 2015, doi: 10.1007/s00034-014-9906-2.

- [10] T. Kulej and F. Khateb, "Design and implementation of sub 0.5-V OTAs in 0.18-µm CMOS," Int. J. Circuit Theory Appl., vol. 46, no. 6, pp. 1129-1143, Jun. 2018, doi: 10.1002/cta.2465.

- [11] T. Kulej, F. Khateb, D. Arbet, and V. Stopjakova, "A 0.3-V high linear rail-to-rail bulk-driven OTA in 0.13 μm CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 4, pp. 2046–2050, Apr. 2022, doi: 10.1109/TCSII.2022.3144095.

- [12] G. D. Colletta, L. H. C. Ferreira, T. C. Pimenta, "A 0.25-V 22-nS symmetrical bulk-driven OTA for low frequency G<sub>m</sub>-C applications in 130-nm digital CMOS process," *Anal. Integr. Circuits Signal Process.*, vol. 81, pp. 377–383, Aug. 2014, doi: 10.1007/s10470-014-0385-y.

- [13] E. D. Cotrim and L. H. C. Ferreira, "An ultra-low-power CMOS symmetrical OTA for low-frequency G<sub>m</sub>-C applications," *Analog Integr. Circ. Signal Process.*, vol. 71, no. 2, pp. 275–282, 2012, doi: 10.1007/s10470-011-9618-50.

- [14] S. Vlassis and G. Raikos, "Bulk-driven differential voltage follower," *Electron. Lett.*, vol. 45, no. 25, pp. 1276–1277, Dec. 2009, doi: 10.1049/el.2009.1551.

- [15] G. Raikos and S. Vlassis, "0.8 V bulk-driven operational amplifier," Anal. Integr. Circuits Signal Process., vol. 63, no. 3, pp. 425–432, Jun. 2010, doi: 10.1007/s10470-009-9425-4.

- [16] G. Raikos, S. Vlassis, and C. Psychalinos, "0.5 V bulk-driven analog building blocks," *AEU Int. J. Electron. Commun.*, vol. 66, no. 11, pp. 920–927, Nov. 2012, doi: 10.1016/j.aeue.2012.03.015.

- [17] F. Khateb and T. Kulej, "Design and implementation of a 0.3-V differential difference amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 2, pp. 513–523, Feb. 2019, doi: 10.1109/TCSI.2018. 2866179.

- [18] A. J. Lopez-Martin, J. Ramirez-Angulo, R. G. Carvajal, and L. Acosta, "CMOS transconductors with continuous tuning using FGMOS balanced output current scaling," *IEEE J. Solid-State Circuits*, vol. 43, no. 5, pp. 1313–1323, May 2008, doi: 10.1109/JSSC.2008. 920333.

- [19] H. D. Rico-Aniles, J. Ramirez-Angulo, A. J. Lopez-Martin, and R. G. Carvajal, "360 nW gate-driven ultra-low voltage CMOS linear transconductor with 1 MHz bandwidth and wide input range," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 11, pp. 2332–2336, Nov. 2020, doi: 10.1109/TCSII.2020.2968246.

- [20] F. Khateb, P. Prommee, and T. Kulej, "MIOTA-based filters for noise and motion artifact reductions in biosignal acquisition," *IEEE Access*, vol. 10, pp. 14325–14338, 2022, doi: 10.1109/ACCESS.2022.3147665.

- [21] M. Kumngern, N. Aupithak, F. Khateb, and T. Kulej, "0.5 V fifth-order Butterworth low-pass filter using multiple-input OTA for ECG applications," *Sensors*, vol. 20, p. 7343, Nov. 2020, doi: 10.3390/s20247343.

- [22] W. Jaikla, F. Khateb, M. Kumngern, T. Kulej, R. K. Ranjan, and P. Suwanjan, "0.5 V fully differential universal filter based on multiple input OTAs," *IEEE Access*, vol. 8, pp. 187832–187839, 2020, doi: 10.1109/ACCESS.2020.3030239.

- [23] P. Prommee, K. Karawanich, F. Khateb, and T. Kulej, "Voltage-mode elliptic band-pass filter based on multiple-input transconductor," *IEEE Access*, vol. 9, pp. 32582–32590, 2021, doi: 10.1109/ACCESS.2021.3060939.

- [24] M. Kumngern, F. Khateb, T. Kulej, and C. Psychalinos, "Multiple-input universal filter and quadrature oscillator using multiple-input operational transconductance amplifiers," *IEEE Access*, vol. 9, pp. 56253–56263, 2021, doi: 10.1109/ACCESS.2021.3071829.

- [25] F. Khateb M. M Kumngern, T. Kulej, and D. Biolek, "0.3-volt rail-to-rail DDTA and its application in a universal filter and quadrature oscillator," *Sensors*, vol. 22, p. 2655, Mar. 2022, doi: 10.3390/s22072655.

- [26] F. Khateb, T. Kulej, M. Akbari, and K.-T. Tang, "A 0.5-V multipleinput bulk-driven OTA in 0.18-μm CMOS," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 30, no. 11, pp. 1739–1747, Nov. 2022, doi: 10.1109/TVLSI.2022.3203148.

- [27] T. Kugelstadt, "Active filter design techniques," in *Op Amps for Everyone*. Boston, MA, USA: Newnes, 2009, pp. 365–438, doi: 10.1016/B978-075067701-1/50019-5.

- [28] E. Yuce, R. Verma, N. Pandey, and S. Minaei, "New CFOA-based firstorder all-pass filters and their applications," *AEU Int. J. Electron. Commun.*, vol. 103, pp. 57–63, May 2019, doi: 10.1016/j.aeue.2019.02.017.

- [29] T. C. Donald, T. C. David, and R. G. Jason, "A high-frequency integrable bandpass filter configuration," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 44, pp. 856–860, 1997, doi: 10.1109/82. 633445.

- [30] A. Paul, J. Ramírez-Angulo, A. J. Lopez-Martin, and R. Gonzalez Carvajal, "CMOS first-order all-pass filter with 2-Hz pole frequency," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 27, no. 2, pp. 294–303, Feb. 2019, doi: 10.1109/TVLSI.2018.2878017.

- [31] I. Myderrizi, S. Minaei, and E. Yuce, "An electronically fine-tunable multi-input-single-output universal filter," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 58, no. 6, pp. 356–360, Jun. 2011, doi: 10.1109/TCSII.2011.2158168.

- [32] M. I. Masud, A. K. B. A'ain, and I. A. Khan, "Reconfigurable CNTFET based fully differential first order multifunctional filter," in *Proc. Int. Conf. Multimedia, Signal Process. Commun. Technol. (IMPACT)*, Aligarh, India, Nov. 2017, pp. 55–59, doi: 10.1109/MSPCT.2017.8363973.

- [33] A. Abaci and E. Yuce, "Voltage-mode first-order universal filter realizations based on subtractors," AEU Int. J. Electron. Commun., vol. 90, pp. 140–146, Jun. 2018, doi: 10.1016/j.aeue.2018.04.017.

- [34] K. Chinpark, W. Jaikla, S. Siripongdee, and P. Suwanjan, "Electronically controllable first-order multifuntion filter with using single active building block," in *Proc. 3rd Int. Conf. Control Robot. Eng. (ICCRE)*, Nagoya, Japan, Apr. 2018, pp. 192–195, doi: 10.1109/ICCRE.2018.8376462.

- [35] P. Singh, V. Varshney, A. Kumar, and R. K. Nagaria, "Electronically tunable first order universal filter based on CCDDCCTA," in *Proc. IEEE Conf. Inf. Commun. Technol.*, Allahabad, India, Dec. 2019, pp. 1–6, doi: 10.1109/CICT48419.2019.9066264.

- [36] W. Jaikla, P. Talabthong, S. Siripongdee, P. Supavarasuwat, P. Suwanjan, and A. Chaichana, "Electronically controlled voltage mode first order multifunction filter using low-voltage low-power bulk-driven OTAs," *Microelectron. J.*, vol. 91, pp. 22–35, Sep. 2019, doi: 10.1016/j.mejo.2019.07.009.

- [37] K. Banerjee, P. K. Bnadopadhyaya, B. Sarkar, and A. Biswas, "Multi input single output using operational transresistance amplifier as first order filter," in *Proc. IEEE VLSI Device Circuit Syst. (VLSI DCS)*, Jul. 2020, pp. 271–274, doi: 10.1109/VLSIDCS47293.2020.9179938.

- [38] W. Jaikla, U. Buakhong, S. Siripongdee, F. Khateb, R. Sotner, P. Silapan, P. Suwanjan, and A. Chaichana, "Single commercially available IC-based electronically controllable voltage-mode first-order multifunction filter with complete standard functions and low output impedance," *Sensors*, vol. 21, no. 21, p. 7376, Nov. 2021, doi: 10.3390/s21217376.

- [39] S. Kumari and D. Nand, "DDCC-based MISO type voltagemode first-order universal filter," in *Proc. 2nd Int. Conf. Intell. Technol. (CONIT)*, Hubli, India, Jun. 2022, pp. 1–6, doi: 10.1109/CONIT55038.2022.9847828.

- [40] M. Dogan and E. Yuce, "A first-order universal filter including a grounded capacitor and two CFOAs," *Anal. Integr. Circuits Signal Process.*, vol. 112, no. 2, pp. 379–390, Aug. 2022, doi: 10.1007/s10470-022-02021-2.

- [41] D. Duangmalai and P. Suwanjan, "The voltage-mode first order universal filter using single voltage differencing differential input buffered amplifier with electronic controllability," *Int. J. Electr. Comput. Eng.*, vol. 12, no. 2, pp. 1308–1323, 2022, doi: 10.11591/ijece.v12i2.pp1308-1323.

- [42] P. Singh and R. K. Nagaria, "Voltage mode and trans-admittance mode first-order universal filters employing DV-EXCCCII," *Austral. J. Electr. Electron. Eng.*, vol. 19, no. 4, pp. 396–406, Oct. 2022, doi: 10.1080/1448837X.2022.2088571.

- [43] K. Rohilla, K. L. Pushkar, R. Kumar, and A. Raj, "Resistorless first-order universal filter structures employing OTAs with independent controllability of gain and pole frequency," *IETE J. Res.*, pp. 1–21, Oct. 2022, doi: 10.1080/03772063.2022.2132305.

- [44] A. Raj, D. R. Bhaskar, R. Senani, and P. Kumar, "Extension of recently proposed two-CFOA-GC all pass filters to the realisation of first order universal active filters," *AEU-Int. J. Electron. Commun.*, vol. 146, Mar. 2022, Art. no. 154119, doi: 10.1016/j.aeue.2022.154119.

- [45] P. Singh and R. K. Nagaria, "First order universal filters employing single DV-EXCCCII," *Int. J. Electron. Lett.*, vol. 11, no. 3, pp. 316–338, Jul. 2023, doi: 10.1080/21681724.2022.2087913.

- [46] M. Dogan, E. Yuce, and Z. Dicle, "CFOA-based first-order voltage-mode universal filters," AEU Int. J. Electron. Commun., vol. 161, Mar. 2023, Art. no. 154550, doi: 10.1016/j.aeue.2023.154550.

- [47] T. Unuk, E. Yuce, and S. Minaei, "Differential input first-order universal filter with two DVCC+s," J. Circuits, Syst. Comput., vol. 32, no. 7, May 2023, Art. no. 2350122, doi: 10.1142/S0218126623501220.

- [48] A. Raj, "Mixed-mode electronically-tunable first-order universal filter structure employing operational transconductance amplifiers," *J. Circuits, Syst. Comput.*, vol. 31, no. 13, Sep. 2022, Art. no. 2250234, doi: 10.1142/S0218126622502346.

- [49] D. R. Bhaskar, A. Raj, S. Raj, and P. Kumar, "CFOA-based simple mixedmode first-order universal filter configurations," *Int. J. Circuit Theory Appl.*, vol. 50, pp. 264–2631, Apr. 2022, doi: 10.1002/cta.3289.

- [50] N. Roongmuanpha, N. Likhitkitwoerakul, M. Fukuhara, and W. Tangsrirat, "Single VDGA-based mixed-mode electronically tunable first-order universal filter," *Sensors*, vol. 23, no. 5, p. 2759, Mar. 2023, doi: 10.3390/s23052759.

- [51] T. Tsukutani, M. Higashimura, N. Takahashi, Y. Sumi, and Y. Fukui, "Versatile voltage-mode active-only biquad with lossless and lossy integrator loop," *Int. J. Electron.*, vol. 88, no. 10, pp. 1093–1101, Oct. 2001, doi: 10.1080/00207210110071279.

- [52] F. Khateb, M. Kumngern, and T. Kulej, "0.5-V nano-power voltage-mode first-order universal filter based on multiple-input OTA," *IEEE Access*, vol. 11, pp. 49806–49818, 2023, doi: 10.1109/ACCESS.2023.3277252.

**FABIAN KHATEB** received the M.Sc. degree in electrical engineering, the M.Sc. degree in business and management, the Ph.D. degree in electrical engineering and communication, and the Ph.D. degree in business and management from the Brno University of Technology, Czech Republic, in 2002, 2003, 2005, and 2007, respectively. He is currently a Professor with the Department of Microelectronics, Faculty of Electrical Engineering and Communication, Brno University of Tech-

nology; the Department of Electrical Engineering, University of Defence, Brno; and the Department of Information and Communication Technology in Medicine, Faculty of Biomedical Engineering, Czech Technical University in Prague. He holds five patents. He has authored or coauthored more than 140 publications in journals and proceedings of international conferences. His expertise is in new principles of designing low-voltage low-power analog circuits, particularly for biomedical applications. He is a member of the Editorial Board of the Microelectronics Journal, Sensor, Machines, Electronics, and Journal of Low Power Electronics and Applications. He is an Associate Editor of IEEE Access, Circuits, Systems, and Signal Processing, IET Circuits, Devices and Systems, and International Journal of Electronics. He was a Lead Guest Editor of the Special Issues on Low Voltage Integrated Circuits and Systems on Circuits, Systems, and Signal Processing, in 2017, IET Circuits, Devices and Systems, in 2018, and Microelectronics Journal, in 2019. He was a Guest Editor of the Special Issue on Current-Mode Circuits and Systems; Recent Advances, Design and Applications on International Journal of Electronics and Communications, in 2017.

**MONTREE KUMNGERN** received the B.S.Ind.Ed. degree in electrical engineering from the King Mongkut's University of Technology Thonburi, Thailand, in 1998, and the M.Eng. and D.Eng. degrees in electrical engineering from the King Mongkut's Institute of Technology Ladkrabang, Thailand, in 2002 and 2006, respectively. In 2007, he was a Lecturer with the Department of Telecommunications Engineering, Faculty of Engineering, King Mongkut's Institute of Technol-

ogy Ladkrabang. From 2010 to 2017, he was an Assistant Professor. He is currently an Associate Professor. He has authored or coauthored more than 200 publications in journals and proceedings of international conferences. His research interests include analog and digital integrated circuits, discrete-time analog filters, non-linear circuits, data converters, and ultra-low voltage building blocks for biomedical applications.

**TOMASZ KULEJ** received the M.Sc. and Ph.D. degrees from Gdańsk University of Technology, Gdańsk, Poland, in 1990 and 1996, respectively. He was a Senior Design Analysis Engineer with the Polish branch of Chipworks Inc., Ottawa, Canada. He is currently an Associate Professor with the Department of Electrical Engineering, Częstochowa University of Technology, Poland, where he conducts lectures on electronics fundamentals, analog circuits, and computer aided

design. He has authored or coauthored more than 100 publications in peer-reviewed journals and conferences. He holds three patents. His research interests include analog integrated circuits in CMOS technology, with emphasis on low voltage and low power solutions. He serves as an Associate Editor for the *Circuits, Systems, and Signal Processing* and *IET Circuits, Devices and Systems*. He was a Guest Editor of the Special Issues on Low Voltage Integrated Circuits on *Circuits, Systems, and Signal Processing*, in 2017; *IET Circuits, Devices and Systems*, in 2018; and *Microelectronics Journal*, in 2019.

VIERA STOPJAKOVA received the M.S. and Ph.D. degrees in electronics from the Slovak University of Technology in Bratislava, Slovakia, in 1992 and 1997, respectively. She is currently a Professor with the Institute of Electronics and Photonics, Faculty of Electrical Engineering and Information Technology, Slovak University of Technology in Bratislava. She has been involved in more than 20 EU funded research projects and national research projects. She has published more than

200 papers in various journals and conferences proceedings and a co-inventor of two U.S. patents in the field of on-chip supply current testing. Her research interests include low-voltage, low-power ASIC design, on-chip testing, design and test of mixed-signal ICs, on-chip energy harvesting, smart sensors, and biomedical monitoring.

**COSTAS PSYCHALINOS** (Senior Member, IEEE) received the B.Sc. and Ph.D. degrees in physics and electronics from the University of Patras, Greece, in 1986 and 1991, respectively.

From 1993 to 1995, he was a Postdoctoral Researcher with the VLSI Design Laboratory, University of Patras. From 1996 to 2000, he was an Adjunct Lecturer with the Department of Computer Engineering and Informatics, University of Patras. From 2000 to 2004, he was an Assistant

Professor with the Electronics Laboratory, Department of Physics, Aristotle University of Thessaloniki, Greece. In 2004, he was a Faculty Member with the Electronics Laboratory, Department of Physics, University of Patras. He is currently a Full Professor. His research interests include the development of CMOS analog integrated circuits, including fractional-order circuits and systems, continuous and discrete-time analog filters, amplifiers, and low voltage/low power building blocks for analog signal processing.

Prof. Psychalinos is a member of the Nonlinear Circuits and Systems Technical Committee of the IEEE CAS Society. He serves as the Editor-in-Chief for the Circuit and Signal Processing Section of the MDPI Electronics journal. He serves as an Area Editor for the International Journal of Electronics and Communications journal, and an Editor for the International Journal of Circuit Theory and Applications. He is an Associate Editor of the Circuits, Systems, and Signal Processing journal, and the Journal of Advanced Research. He is a member of the Editorial Board of the Microelectronics Journal, Analog Integrated Circuits and Signal Processing journal, IETE Journal of Education, Fractal and Fractional journal, and Journal of Low Power Electronics and Applications.