Article

# Universal Filter Based on Compact CMOS Structure of VDDDA

Winai Jaikla 1,\* D, Fabian Khateb 2,3 D, Tomasz Kulej 4 D and Koson Pitaksuttayaprot 5

- Department of Engineering Education, Faculty of Industrial Education and Technology, King Mongkut's Institute of Technology Ladkrabang, Bangkok 10520, Thailand

- Department of Microelectronics, Brno University of Technology, Technická 10, 601 90 Brno, Czech Republic; khateb@feec.vutbr.cz

- <sup>3</sup> Faculty of Biomedical Engineering, Czech Technical University in Prague, nám.Sítná 3105, Kladno, 166 36 Prague, Czech Republic

- Department of Electrical Engineering, Technical University of Czestochowa, 42-201 Czestochowa, Poland; kulej@el.pcz.czest.pl

- Department of Technology Electronic, Faculty of Agricultural and Industrial Technology, Phetchabun Rajabhat University, Phetchabun 67000, Thailand; koson@pcru.ac.th

- \* Correspondence: winai.ja@kmitl.ac.th; Tel.: +66-81305-1643

Abstract: This paper proposes the simulated and experimental results of a universal filter using the voltage differencing differential difference amplifier (VDDDA). Unlike the previous complementary metal oxide semiconductor (CMOS) structures of VDDDA that is present in the literature, the present one is compact and simple, owing to the employment of the multiple-input metal oxide semiconductor (MOS) transistor technique. The presented filter employs two VDDDAs, one resistor and two grounded capacitors, and it offers low-pass: LP, band-pass: BP, band-reject: BR, high-pass: HP and all-pass: AP responses with a unity passband voltage gain. The proposed universal voltage mode filter has high input impedances and low output impedance. The natural frequency and bandwidth are orthogonally controlled by using separated transconductance without affecting the passband voltage gain. For a BP filter, the root mean square (RMS) of the equivalent output noise is 46  $\mu$ V, and the third intermodulation distortion (IMD3) is -49.5 dB for an input signal with a peak-to peak of 600 mV, which results in a dynamic range (DR) of 73.2 dB. The filter was designed and simulated in the Cadence environment using a 0.18-µm CMOS process from Taiwan semiconductor manufacturing company (TSMC). In addition, the experimental results were obtained by using the available commercial components LM13700 and AD830. The simulation results are in agreement with the experimental one that confirmed the advantages of the filter.

Keywords: VDDDA; biquad filter; operational transconductance amplifier; multiple-input technique

Citation: Jaikla, W.; Khateb, F.; Kulej, T.; Pitaksuttayaprot, K. Universal Filter Based on Compact CMOS Structure of VDDDA. *Sensors* **2021**, *21*, 1683. https://doi.org/10.3390/s21051683

Academic Editor: Mario Luiso

Received: 20 January 2021 Accepted: 22 February 2021 Published: 1 March 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

## 1. Introduction

Analog filters are very useful in an analog signal processing system [1–4]. They are used to pass the desired frequency band from the input section to the output section. Therefore, the frequency filter is an essential element of any signal processing system that will be indispensable. Especially, in sensor applications, a filter is very important to detect the wanted signal, for example, in the phase sensitive detection [5], electrocardiographic (ECG) system [6], biosensors [7], etc. The biquad active filter has been a very popular research topic for last three decades. The main reason for the popularity of the biquad filter design is that it can be modified to obtain five filtering functions, which are the low-pass: LP, band-pass: BP, band-reject: BR, high-pass: HP and all-pass: AP functions. Compared to the first-order configuration, this filter can give only three LP, HP and BP functions, as well as the higher order filter, which mostly gives only one filtering response. The versatile biquad filter that gives multiple filtering functions within the same configuration is well-known as the universal or multifunction filter. In the open literature, this type of active filter has been proposed continuously [8–12].

Sensors **2021**, 21, 1683 2 of 22

The voltage differencing differential difference amplifier (VDDDA) [13] is a very useful and versatile building block for the voltage-mode active biquad filtering design. With the operational transconductance amplifier (OTA) at the input stage of the VDDDA, the filtering characteristics (for example, the passband voltage gain, bandwidth, quality factor, the cut-off frequency or phase response of the VDDDA-based filer) can be controlled via the transconductance  $(g_m)$ . Moreover, with the unity gain voltage differential difference amplifier (DDA) at the output stage of the VDDDA, it is very useful for the voltage-mode filter design without the use of additional or external voltage summing or a voltage differencing circuit, especially in the two-integrator loop filter design. Additionally, some VDDDA-based voltage-mode filters can cascade without the requirement of additional buffer devices. In this point of view, several active biquad filters using the VDDDA have been reported [13–24]. The voltage mode biquad filters using the voltage differential difference device (called the differential difference current conveyor transconductance amplifier (DDCCTA)) have been also proposed in references [25-27]. These biquad filters can be classified into two categories based on their design techniques, which are based on two integrator loops [13-15,17,19-22,25,27] and based on a passive resistorinductor-capacitor (RLC) circuit [16,18,23,24,26]. The RLC based biquad filters proposed in [16,18,23,24] have very simple circuitry with a single VDDDA. However, these biquad filter realized from the RLC circuit have the following disadvantages: they consist of a floating capacitor [16,18,24,26], the natural frequency  $(f_0)$  and quality factor (Q) are not orthogonally controlled by changing the transconductance of the VDDDA [16,18,23,24], high impedance nodes at the input stage and a low impedance node at the output stage are not obtained [16,18,23,24,26] and additional circuits such as the unity gain inverting voltage amplifier or double-gain voltage amplifier are required for obtaining many filtering functions [16,18,24,26]. Two-integrator loop-based biquad filters with high input impedance were obtained in references [13–15,17,19–22,27]. Additionally, a low output impedance property for all output nodes was obtained in references [19,21,22]. In [13,14,20–22], the  $f_0$  and Q were orthogonally controlled by the separated transconductance. However, the biquad filter proposed in references [13,14,20-22] requires three VDDDAs. Additionally, the passband voltage gain of three VDDDA-based filters in references [13,14,22] is not constant during tuning the  $f_0$  and Q for some filtering responses. The two-integrator loop filter in references [15,17] cannot provide five filter responses. Additionally, two VDDDA-based biquad filters in references [15,17,19] and the biquad filter using DDCCTA in references [25,27] cannot achieve the orthogonal control of the  $f_0$  and Q by separated transconductance. As reviewed above, it was found that the two VDDDA-based universal biquad filters with the feature of orthogonal control of the  $f_0$  and Q by the separated transconductance were been available in the open literature.

The multiple-input MOS transistor (MI-MOST) is an effective technique that may reduce the count of the transistors needed to build some active blocks and simplify their CMOS topologies. This technique was, for the first time, presented and experimentally confirmed by Khateb et al. [28–30]. Recently, several active functional blocks, such as the differential difference amplifier (DDA) [28], differential difference current conveyors (DDCC) [30–32], fully differential difference amplifier (FDDA) [33] and multiple-input OTA [6,34–36], were designed based on this technique. It was shown that applications based on the MI-MOST technique can be realized with less numbers of active blocks, smaller chip areas and reduced power consumptions compared to conventional designs [6,28–36].

In the past, a multiple-input OTA was used to reduce the number of components, silicon area, and power dissipation in the OTA-C filter design where a third-order elliptic low-pass filter was built by five double-input OTAs instead of seven single-input OTAs [37]. Another example is the use of a two-input-stage OTA instead of a conventional OTA to build a leapfrog realization of a seventh-order elliptic filter in order to facilitate the signal addition required in the feedback paths of the leapfrog realization [38]. In both the aforementioned examples, additional active transistors were used to realize the multiple-input terminals. Another way to obtain multiple-input MOST is the utilizing of a multiple-input floating-

Sensors **2021**, 21, 1683 3 of 22

gate transistor (MIFG) [39]. However, this technique is based on charge conservation; hence, it cannot be used in CMOS technologies with gate leakage [40].

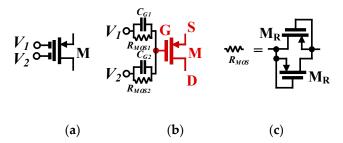

Figure 1 shows an example of multiple-input gate-driven MOST with two inputs. Each input ( $V_1$  and  $V_2$ ) is connected to the gate (G) of the MOST (M) by a parallel connection of an input capacitor ( $C_1$  and  $C_2$ ) and high resistance ( $R_{MOS1}$  and  $R_{MOS2}$ ) created by two MOST ( $M_R$ ) operating as a diode in the cut-off region. Due to using the transistor  $M_R$ , the chip area is saved. Note that the multiple-input technique could be applied to the gate terminal [6,36], bulk terminal [28], bulk-gate terminal [34] or bulk-quasi-floating-gate terminal of the MOST [29]. However, unlike the aforementioned multiple-input techniques, the multiple-input gate-driven MOST offers the advantage of that regardless of the CMOS technology used; both transistor types (N-MOS and PMOS) could be created with a multiple-input signal.

**Figure 1.** The multiple-input metal oxide semiconductor transistor (MOST): (**a**) symbol, (**b**) realization and (**c**) realization of  $R_{MOS}$  [28].

This paper presents a universal filter based on the compact CMOS structure of the multiple-input gate-driven VDDDA. The paper is organized as follows: Section 2 presents the CMOS structure of the VDDDA and the proposed universal filter. Sections 3 and 4 present the simulation and experimental results, respectively. The comparison of the proposed biquad filter with other filters using VDDDA is discussed and explained in Section 5, and finally, Section 6 concludes the paper.

## 2. Proposed Universal Filter

## 2.1. Basic Concept of the VDDDA

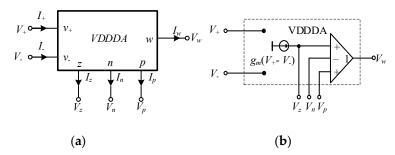

The VDDDA is a connection of OTA and a unity gain DDA. The basic version of the VDDDA with circuit symbols, as in Figure 2a, is an analog functional block with five terminals. The high-impedance input voltage terminals are  $v_+$ ,  $v_-$ , z, n and p. The low-impedance output voltage terminal is w. Note that the z terminal is also the output current terminal. An ideal corresponding equivalent circuit of the VDDDA is illustrated in Figure 2b. The circuit performance is described by the matrix Equation (1):

$$I_{+} = I_{-} = I_{n} = I_{p} = 0; I_{z} = g_{m}(V_{+} - V_{-}); V_{w} = V_{z} - V_{n} + V_{p},$$

(1)

**Figure 2.** Voltage differencing differential difference amplifier (VDDDA): (a) electrical symbol and (b) equivalent circuit [13].

Sensors **2021**, 21, 1683 4 of 22

## 2.2. The CMOS Structure of the VDDDA

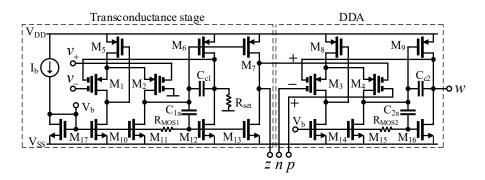

The VDDDA consists of a transconductance stage  $(g_m)$  followed by a differential difference amplifier (DDA), as shown in Figure 3. The transconductance stage is formed by a differential stage  $(M_1, M_2, M_5, M_{10})$  and  $M_{11}$  and a doubled output stage  $(M_6, M_{12})$  $M_7$  and  $M_{13}$ ). Thanks to the negative feedback between the output (drain of  $M_6$ ) and the input terminals of M<sub>1</sub>, the linearity of the transconductance is increased. The capacitor  $C_{1a}$  and the MOS resistor  $R_{MOS1}$  are used to obtain a class AB output stage. The capacitor  $C_{c1}$  creates the compensation network of the transconductor. The resistor  $R_{set}$  is used to set the transconductance value in such a way that  $g_{m,set} \approx 1/R_{set}$  for  $R_{set} >> 1/g_m$ , where  $g_m$  is the internal transconductance of this stage [41]. Note that the tuning mechanism is very simple; the difference of the input voltages  $(V_+ - V_-)$  will appear across  $R_{set}$  due to the negative unity feedback. The resistor current  $I_{Rset}$  will be controlled by the value of  $R_{set}$ . The output current  $I_z$  is a copy of  $I_{Rset}$ . The DDA is created in similar manner as the transconductance stage. The bias current  $I_h$  and the transistor  $M_{17}$  create the bias current and voltage needed for the circuit. It is worth noting that the minimum voltage supply of the proposed VDDDA structure is given by one gate-source and one drain-source voltage, i.e.,  $V_{DDmin} = V_{GSM5} + V_{DSM10}$ . Hence, the structure is suitable for low-voltage supply applications.

Figure 3. The CMOS structure of the VDDDA.

## 2.3. The Universal Biquad Filter based on VDDDAs

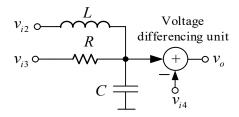

Most of the published papers on universal biquad filters have not shown the method to design the topology. Therefore, new researchers or designers do not understand how to get the completed circuits. In this paper, a simple method to design the biquad filter is also presented to achieve the important goal of this design, which is to use only two VDDDAs to get the orthogonal tune of the quality factor and the natural frequency by using separated transconductance. The proposed biquad universal filter is designed from the parallel RLC circuit connecting with the voltage differencing circuit, as shown in Figure 4. There are three input voltages applied to the circuit:  $v_{i2}$  is applied through the inductor,  $v_{i3}$  is applied to the resistor and  $v_{i4}$  is applied at the inverting input of the voltage differencing circuit. For a conventional design, other input voltages can be applied through the capacitor. However, using a grounded capacitor is required for this design to ensure the reduction in fabrication space and the compensation of parasitic effects.

Figure 4. Method to design the proposed biquad filter.

Sensors **2021**, 21, 1683 5 of 22

Considering the circuit shown in Figure 4, the following output voltage,  $v_o$ , is obtained:

$$v_0 = \frac{\frac{1}{LC}v_{i2} + s\frac{1}{CR}v_{i3} - \left(s^2 + s\frac{1}{CR} + \frac{1}{LC}\right)v_{i4}}{s^2 + s\frac{1}{CR} + \frac{1}{LC}},$$

(2)

Based on Equation (2), several filter responses can be obtained from the same topology by appropriately applying the input signal to the input voltage nodes  $v_{i2}$ ,  $v_{i3}$  and  $v_{i4}$  of the filter, and this detail will be described later. The natural frequency, bandwidth (BW) and quality factor for Equation (2) are obtained by

$$\omega_0 = \sqrt{\frac{1}{LC'}},\tag{3}$$

$$BW = \frac{1}{RC},\tag{4}$$

and

$$Q = R\sqrt{\frac{C}{L}},\tag{5}$$

Equations (3) and (4) indicate that the  $\omega_0$  and BW (or the Q) are orthogonally controlled. It is vital to note that the Q is controlled through the resistor R without affecting the natural frequency. To get the required natural frequency and bandwidth for the practical design, the natural frequency must be first designed by setting the inductance (L) and capacitance (C) values. Then, the required bandwidth or quality factor can be achieved by independently setting the resistance value without disturbing the natural frequency.

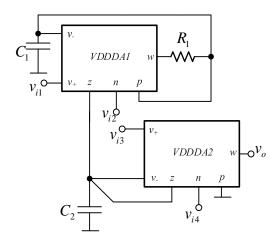

Considering the method to design the filter in Figure 4, there are four sub-circuits, which are the inductor, resistor, grounded capacitor and the voltage summing circuit. These passive inductor and resistors can be replaced by active simulators using the VDDDA. The active inductor used in this design is modified from the floating lossless inductance simulator using two VDDDAs proposed in reference [42]. Only one VDDDA is required for the active inductor in our work. Additionally, the active resistor and voltage differencing circuit can be realized from one VDDDA. Based on this principle, the proposed universal biquad filter is illustrated in Figure 5. The proposed filter comprises two VDDDAs, two grounded capacitors and one resistor, where the VDDDA<sub>1</sub>,  $C_1$  and  $R_1$  operate as the active inductors. The active resistor and voltage differencing circuit is constructed from VDDDA<sub>2</sub>, and the grounded capacitor  $C_2$  acts as C in Figure 4. There are four input voltage nodes:  $v_{i1}$ ,  $v_{i2}$ ,  $v_{i3}$  and  $v_{i4}$ , which is slightly different from the principle in Figure 4. The input voltage nodes  $v_{i2}$ ,  $v_{i3}$  and  $v_{i4}$  are the same as the principle in Figure 4. The additional  $v_{i1}$ node is added to get the all-pass response, which will be given more detail later. It is found that all input voltage nodes of the proposed universal biquad filter are high impedance, while the output voltage  $(v_0)$  node is low impedance. The proposed universal biquad filter can cascade without the requirement of any voltage buffers at the input and output stages. Moreover, it consists of all the grounded capacitors, which ensures a reduction in the fabrication space and compensation of the parasitic effects.

Considering the circuit shown in Figure 5, the following output voltage,  $v_o$ , is obtained.

$$v_{o} = \frac{s\frac{g_{m1}}{C_{2}}v_{i1} + \frac{g_{m1}}{C_{1}C_{2}R_{1}}v_{i2} + s\frac{g_{m2}}{C_{2}}v_{i3} - \left(s^{2} + s\frac{g_{m2}}{C_{2}} + \frac{g_{m1}}{C_{1}C_{2}R_{1}}\right)v_{i4}}{s^{2} + s\frac{g_{m2}}{C_{2}} + \frac{g_{m1}}{C_{1}C_{2}R_{1}}},$$

(6)

Based on Equation (6), several filter responses can be given from the same filtering topology in Figure 5 by applying the appropriate input voltage signal to the input nodes of the filter as follows:

• Noninverting low-pass filter with unity voltage gain is given at the output voltage node  $v_0$  of the proposed filter by applying the input signal into the input voltage node  $v_{i2}$  while the other input voltage nodes are grounded.

Sensors **2021**, 21, 1683 6 of 22

• Noninverting band-pass filter with unity voltage gain is given at the output voltage node  $v_0$  of the proposed filter by applying the input signal into the input voltage node  $v_{i3}$  while the other input voltage nodes are grounded.

- Inverted high-pass filter with unity voltage gain is given at the output voltage node  $v_o$  of the proposed filter by applying the input signal into the input voltage nodes  $v_{i2}$ ,  $v_{i3}$  and  $v_{i4}$  while the input voltage node  $v_{i1}$  is grounded.

- Inverted band-stop filter with unity voltage gain is given at the output voltage node  $v_0$  of the proposed filter by applying the input signal into the input voltage nodes  $v_{i3}$  and  $v_{i4}$  while other nodes are grounded.

- Inverted all-pass filter with unity voltage gain is given at the output voltage node  $v_0$  of the proposed filter by setting  $g_{m1} = g_{m2}$  and applying the input signal into the input voltage nodes  $v_{i1}$ ,  $v_{i3}$  and  $v_{i4}$  while the input voltage node  $v_{i2}$  is grounded. Although it requires the matching conditions of  $g_{m1}$  and  $g_{m2}$ , this is the active matching condition that is easier to control than the passive matching one.

- Inverted all-pass filter without the matching condition is given at the output voltage node  $v_0$  of the proposed filter by connecting the z terminal to the p terminal of the VDDDA<sub>2</sub>, then applying the input signal into the input voltage nodes  $v_{i3}$  and  $v_{i4}$  while the other input voltage nodes are grounded.

Figure 5. The universal filter based on the VDDDA.

From the above statement, it is found that the selection of filter responses does not require additional circuits—for example, inverting or double-gain amplifiers. The natural frequency, bandwidth and quality factor for Equation (6) are obtained by

$$\omega_0 = \sqrt{\frac{g_{m1}}{C_1 C_2 R_1}},\tag{7}$$

$$BW = \frac{g_{m2}}{C_2},\tag{8}$$

and

$$Q = \frac{1}{g_{m2}} \sqrt{\frac{g_{m1}C_2}{C_1 R_1}},\tag{9}$$

Equations (7) and (8) indicate that the  $\omega_0$  and BW (or the Q in Equation (9)) are orthogonally controlled. In a practical design to get the required natural frequency and bandwidth, the natural frequency must be first designed by setting the  $g_{m1}$ ,  $R_1$ ,  $C_1$  and  $C_2$ . Then, the required bandwidth or quality factor can be achieved by independently setting the  $g_{m2}$  without disturbing the natural frequency.

Sensors **2021**, 21, 1683 7 of 22

## 2.4. Effects of Nonideal VDDDA Characteristics

The nonideal properties of the VDDDA will affect the performances of the proposed universal biquad filter. Therefore, these nonideal cases will be considered and studied in this section. There are two nonideal characteristics, which are the voltage tracking errors and parasitic impedances, at the VDDDTA terminals. Firstly, the voltage tracking error in the voltage differencing stage of the VDDDA will be considered. The VDDDA property with the voltage tracking errors is given by

$$\begin{pmatrix}

I_{+} \\

I_{-} \\

I_{z} \\

I_{n} \\

I_{p} \\

V_{w}

\end{pmatrix} = \begin{pmatrix}

0 & 0 & 0 & 0 & 0 & 0 & 0 \\

0 & 0 & 0 & 0 & 0 & 0 & 0 \\

g_{m} & g_{m} & 0 & 0 & 0 & 0 & 0 \\

0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\

0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\

0 & 0 & \beta_{z} & -\beta_{n} & \beta_{n} & 0

\end{pmatrix} \begin{pmatrix}

V_{v+} \\

V_{v-} \\

V_{z} \\

V_{n} \\

V_{p} \\

I_{zv}

\end{pmatrix}, (10)$$

Here,  $\beta_z = 1 - \varepsilon_z$  and  $\varepsilon_z$  ( $|\varepsilon_z| <<1$ ) denotes the voltage tracking error from the z to w terminal,  $\beta_n = 1 - \varepsilon_n$  and  $\varepsilon_n$  ( $|\varepsilon_n| <<1$ ) denotes the voltage tracking error from the n to w terminal and  $\beta_p = 1 - \varepsilon_p$  and  $\varepsilon_p$  ( $|\varepsilon_n| <<1$ ) denotes the voltage tracking error from the p to w terminal. Considering these errors, the output voltage of the proposed universal filter can be expressed as follows:

$$v_{o} = \frac{\left[ (1 - \varepsilon_{z2}) \left( s \frac{g_{m1}}{C_{2}} + \frac{\varepsilon_{p1}g_{m1}}{C_{1}C_{2}R_{1}} \right) v_{i1} + (1 - \varepsilon_{n1}) (1 - \varepsilon_{z2}) \frac{g_{m1}}{C_{1}C_{2}R_{1}} v_{in2} + \left[ (1 - \varepsilon_{z2}) \left( s \frac{g_{m2}}{C_{2}} + \frac{\varepsilon_{p1}g_{m2}}{C_{1}C_{2}R_{1}} \right) v_{i3} - (1 - \varepsilon_{n2}) D^{*}(s) v_{i4} \right]}{D^{*}(s)},$$

(11)

where

$$D^*(s) = s^2 + s \left[ \frac{\varepsilon_{p1}}{C_1 R_1} + \frac{1}{C_2} g_{m2} \right] + \frac{\varepsilon_{p1} g_{m2} + (1 - \varepsilon_{z1}) g_{m1}}{C_1 C_2 R_1}, \tag{12}$$

Therefore, the  $\omega_0$ , BW and Q with nonideal gains are, respectively, given as

$$\omega_0^* = \sqrt{\frac{\varepsilon_{p1} g_{m2} + (1 - \varepsilon_{z1}) g_{m1}}{C_1 C_2 R_1}},\tag{13}$$

$$BW^* = \frac{\varepsilon_{p1}}{C_1 R_1} + \frac{1}{C_2} g_{m2},\tag{14}$$

and

$$Q^* = \frac{C_1 C_2 R_1}{\varepsilon_{\nu 1} C_2 + C_1 R_1 g_{m2}} \sqrt{\frac{\varepsilon_{\nu 1} g_{m2} + (1 - \varepsilon_{z1}) g_{m1}}{C_1 C_2 R_1}}.$$

(15)

It is noticeable that the voltage gain, natural frequency, bandwidth and the quality factor are affected by the voltage tracking errors. Additionally, it is found in Equation (14) that the transconductance,  $g_{m2}$  will slightly affect the natural frequency due to the  $\varepsilon_{p1}$ . However, these voltage tracking errors are much less than one; their effects can be neglected at low-frequency operations.

The effects of parasitic impedances at the input and output terminals of the VDDDA are considered next. These parasitic impedances are the parallel  $C_+$  and  $R_+$  at the  $v_+$  terminal, the parallel  $C_-$  and  $R_-$  at the  $v_-$  terminal, the parallel  $C_z$  and  $R_z$  at the z terminal, the parallel  $C_n$  and  $R_n$  at the n terminal, the parallel  $C_p$  and  $R_p$  at the p terminal and the  $R_w$  (series at the p terminal) at the low output impedance p terminal, as shown in Figure 6.

Sensors **2021**, 21, 1683 8 of 22

Figure 6. The parasitic effects on the VDDDA.

Considering theses parasitic impedances, the output voltage under the parasitic effect is given by

$$v_{o} = \frac{\left(s\frac{g_{m1}}{C_{2}^{*}R_{1}^{*}} + \frac{G_{1}^{*}g_{m1}}{C_{1}^{*}C_{2}^{*}R_{1}^{*}}\right)v_{i1} + g_{m1}v_{in2} + \left(s\frac{g_{m2}}{C_{2}^{*}R_{1}^{*}} + \frac{G_{1}^{*}g_{m2}}{C_{1}^{*}C_{2}^{*}R_{1}^{*}}\right)v_{i3} - D^{**}(s)v_{n2}}{D^{**}(s)}, \quad (16)$$

where

$$D^{**}(s) = s^2 + s \left( \frac{G_1^*}{C_1^*} + \frac{G_2^*}{C_2^*} + \frac{g_{m2}}{C_2^*} \right) + \frac{G_1^* g_{m2} R_1 + G_1^* G_2^* R_1^* + g_{m1}}{C_1^* C_2^* R_1^*}, \tag{17}$$

and  $C_1^* = C_1 + C_{-1} + C_{p1}$ ,  $C_2^* = C_2 + C_{z1} + C_{-2} + C_{z2}$ ,  $G_1^* = G_{-1} + G_{p1}$ ,  $G_2^* = G_{z1} + G_{-2} + G_{z2}$ ,  $R_1^* = R_1 + R_{w1}$ ,  $G_{-1} = 1/R_{-1}$ ,  $G_{p1} = 1/R_{p1}$ ,  $G_{z1} = 1/R_{z1}$ ,  $G_{-2} = 1/R_{-2}$  and  $G_{z2} = 1/R_{z2}$ . The  $\omega_0$ , BW and Q with parasitic effects are respectively given as

$$\omega_0^{**} = \sqrt{\frac{G_1^* g_{m2} R_1 + G_1^* G_2^* R_1^* + g_{m1}}{C_1^* C_2^* R_1^*}},$$

(18)

$$BW^{**} = \frac{G_1^*}{C_1^*} + \frac{G_2^*}{C_2^*} + \frac{g_{m2}}{C_2^*},\tag{19}$$

and

$$Q^{**} = \frac{C_1^* C_2^* R_1^*}{C_2^* G_1^* R_1 + C_1^* G_2^* R_1^* + C_1^* g_{m2} R_1^*} \sqrt{\frac{G_1^* g_{m2} R_1 + G_1^* G_2^* R_1^* + g_{m1}}{C_1^* C_2^* R_1^*}}.$$

(20)

It is noticeable that the voltage gain, natural frequency, bandwidth, the quality factor and operational frequency range of the proposed filter are affected by the parasitic impedances in the VDDDA. Additionally, it is found from Equation (20) that the transconductance,  $g_{m2}$ , will slightly affect the natural frequency due to the parasitic impedance,  $G_1^*$ . However, the effect of the parasitic capacitances can be minimized by setting the value of  $C_1 >> C_{-1}$  and  $C_p$  and  $C_p$  and  $C_p$  and  $C_p$ . While the parasitic resistance  $R_{w1}$  can be minimized by setting the value of  $R_1 >> R_{w1}$ . As mentioned above, using grounded capacitors is advantageous for the compensation of parasitic effects.

## 3. Simulation Results

The CMOS circuit of the VDDDA and the filter application were designed and simulated in the Cadence environment using a 0.18-µm CMOS process from TSMC. The voltage supply is  $V_{DD}=-V_{SS}=0.9$  V, the bias current is  $I_b=50$  µA and the total power consumption is 0.99 mW. The transistors aspect ratio of the VDDDA shown in Figure 3 are  $M_1-M_4=90$  µm/3 µm;  $M_5-M_9=2\times90$  µm/3 µm;  $M_{10},M_{11},M_{14},M_{15}$  and  $M_{17}=30$  µm/3 µm;  $M_{12},M_{13}$  and  $M_{16}=2\times30$  µm/3 µm and  $M_R=4$  µm/5 µm. The values of the passive components are  $C_{c1},C_{c2},C_{1a}$  and  $C_{2a}=2.6$  pF and  $C_G=0.5$  pF.

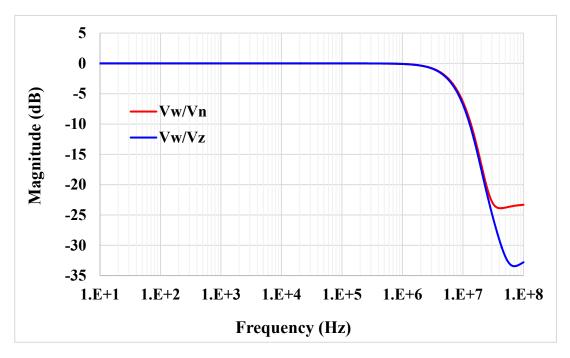

Figure 7 shows the frequency responses of  $V_w/V_n$  and  $V_w/V_z$  ( $V_w/V_p$ ), where the gain at low frequency is -7 mdB and 5 mdB and the -3 dB bandwidth is 6.3 MHz and 6.1 MHz,

Sensors **2021**, 21, 1683 9 of 22

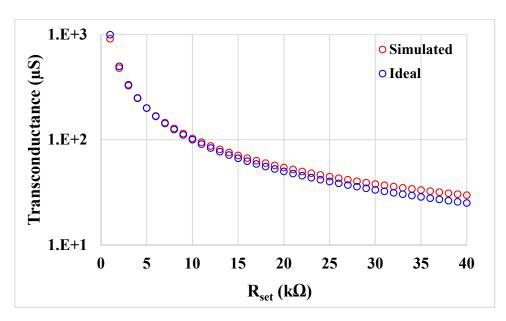

respectively. Figure 8 shows the relation of the simulated and ideal transconductance versus the  $R_{set}$ . Note that the curves match for the lower value of  $R_{set}$ .

**Figure 7.** The frequency responses of  $|V_w/V_n|$  and  $|V_w/V_z|$ .

**Figure 8.** The transconductance value of the simulated and ideal transconductor versus  $R_{set}$ .

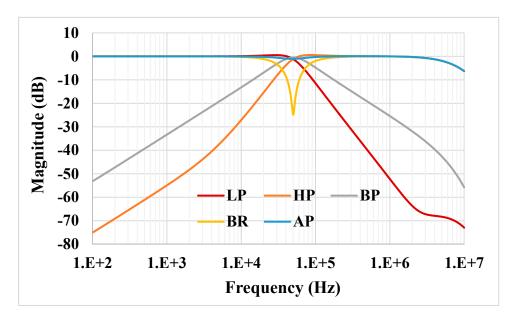

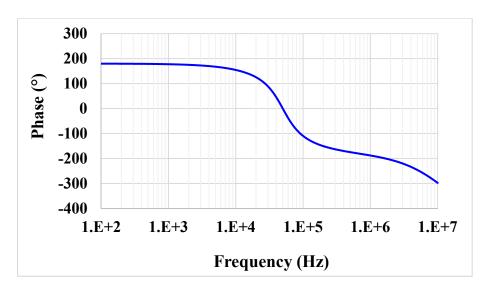

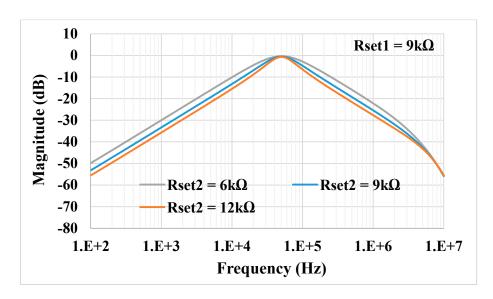

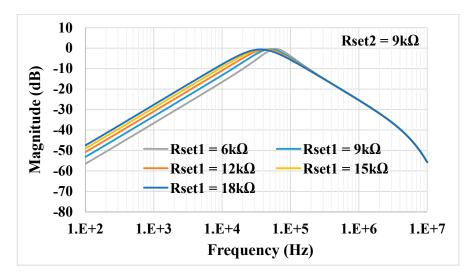

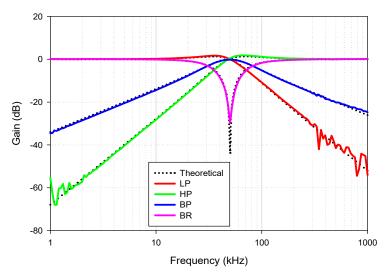

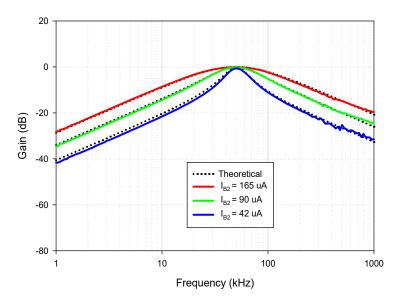

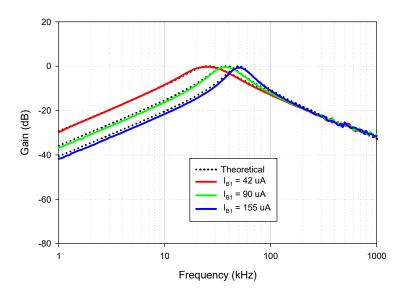

For the proposed filter in Figure 5, the values of the passive components were selected as  $C_1 = C_2 = 335$  pF,  $R_1 = 10$  k $\Omega$ , and the value of the resistor of the transconductors was  $R_{set1} = R_{set2} = 9$  k $\Omega$ . Figure 9 shows the frequency characteristics of the LP, HP, BP, BR and AP filters, while the phase response of the AP filter is shown in Figure 10. However, for the BR response, the attenuation was obtained around -26 dB due to nonideal characteristics of the VDDDA, as explained in Section 2.4. The simulated natural frequency was  $f_0 = 50$  kHz. Figure 11 shows the tunability of the BP filter for  $R_{set2} = 6$  k $\Omega$ , 9 k $\Omega$  and 12 k $\Omega$ , while  $R_{set1} = 9$  k $\Omega$ . Figure 12 shows the tunability of the BP filter for  $R_{set1} = 6$  k $\Omega$ , 9 k $\Omega$ , 12 k $\Omega$ , 15 k $\Omega$  and 18 k $\Omega$ , while  $R_{set2} = 9$  k $\Omega$ . The frequency  $f_0$  was 60.9 kHz, 50.1 kHz, 44.1 kHz,

Sensors 2021, 21, 1683 10 of 22

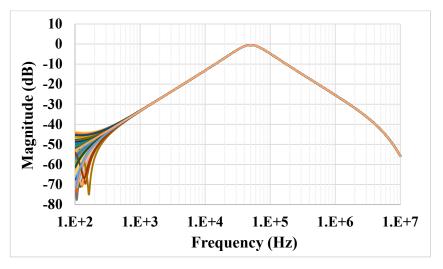

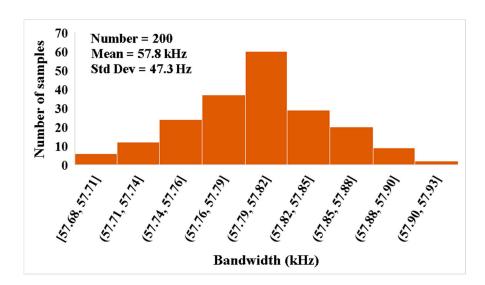

39.3 kHz and 36.3 kHz, respectively. The Monte Carlo analysis (including transistors and passive device mismatches) of the BP filter with 200 runs is shown in Figure 13. The curves are overlapped and confirm the stability of the circuit. Figure 14 shows the histogram of the bandwidth (BW) of the BP filter with 200 runs of the Monte Carlo analysis. While the mean value is 57.8 kHz, the standard deviation is only 47.3 Hz.

Figure 9. Frequency characteristics of the proposed universal filter.

Figure 10. Phase characteristics of the all-pass (AP) filter.

Sensors **2021**, 21, 1683 11 of **22**

**Figure 11.** Tunability of the band-pass (BP) filter for different  $R_{set2}$  and the constant  $R_{set1}$ .

**Figure 12.** Tunability of the BP filter for different  $R_{set1}$  and the constant  $R_{set2}$ .

Figure 13. Monte Carlo analysis of the frequency characteristics of the BP filter with 200 runs.

Sensors **2021**, 21, 1683

Figure 14. The histogram of the bandwidth of the BP filter with 200 runs of the Monte Carlo analysis.

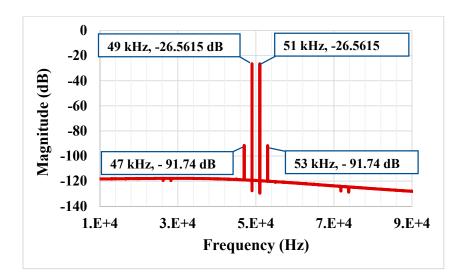

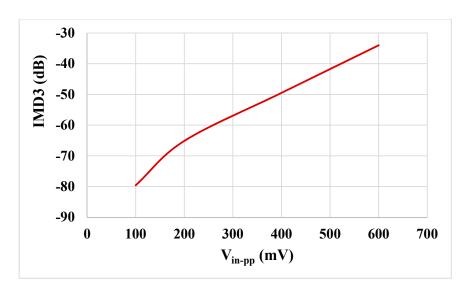

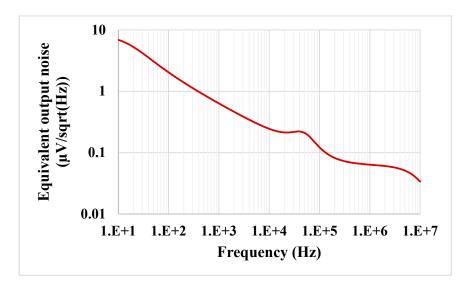

The results of the process, voltage and temperature (PVT) corner analysis of the BP filter are shown in Figure 15. The process corners for the MOST were fast-fast, fast-slow, slow-fast and slow-slow, for capacitor and resistor corners were fast and slow, the voltage supply corners VDD = -VSS were 890 mV and 910 mV and, finally, the temperature corners were -20 and 80 °C. While the nominal value of the BW is 57.8 kHz, the minimum BW is 57.17 kHz, and the maximum BW is 58.55 kHz under all corner variations. To test the third intermodulation distortion of the BP filter, two closely spaced tones were applied to the input of the BP filter. The first tone was a sine wave signal with 100-mVpp @ 49 kHz and the second tone with 100-mVpp @ 51 kHz. The spectrum of the output signal is shown in Figure 16. The third intermodulation distortion (IMD3) was -65.148 dB. Figure 17 shows the IMD3 of the BP filter versus the peak-to-peak value of the input signal. It is clear that the filter offers IMD3 of -34 dB for the 600-mVpp input signal. As shown in Figure 18, the RMS value of the output noise integrated in the pass band of the filter (29.11 kHz–86.9 kHz) is 46  $\mu$ Vrms, and the RMS value of the input signal for 2% IMD3 is 0.2121 V; hence, the dynamic range of the BP filter is 73.27 dB.

Figure 15. The process, voltage and temperature (PVT) corner analysis of the BP filter.

Sensors **2021**, 21, 1683

Figure 16. The spectrum of the output signal of the BP filter.

**Figure 17.** The third intermodulation distortion (IMD3) of the BP filter versus the peak-to-peak value of the input signal.

Figure 18. The equivalent output noise of the BP filter.

Sensors **2021**, 21, 1683 14 of 22

## 4. Experimental Results

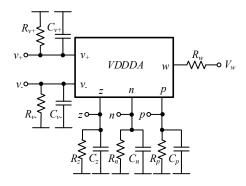

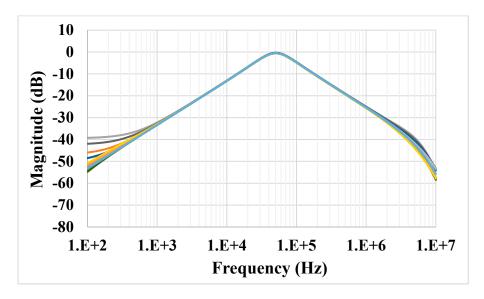

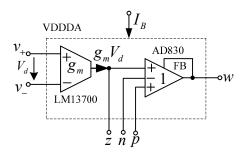

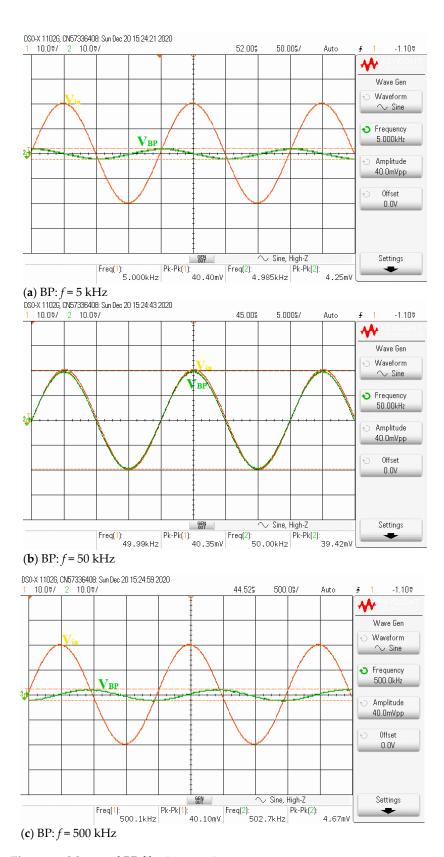

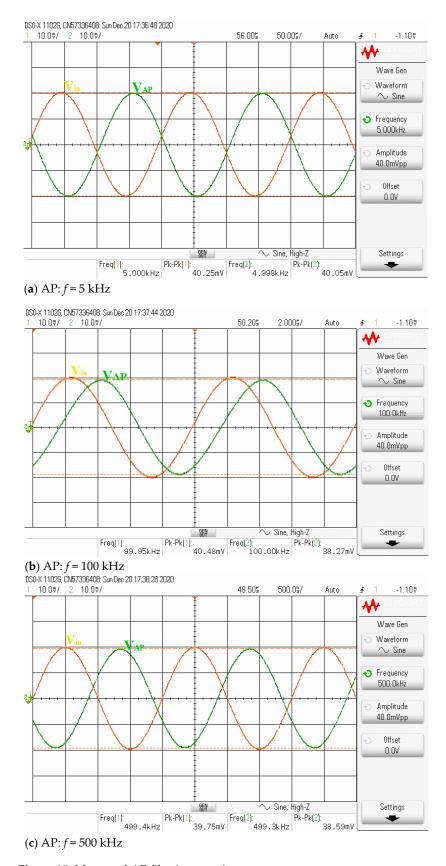

Theoretically described behaviors of the proposed universal filter were also verified experimentally by implementing the VDDDA from LM13700 (transconductance stage) and AD830 (differential difference amplifier stage), as shown in Figure 19. The transconductance (gm) of LM13700 is electronically controlled with  $g_m = I_B/2V_T$ , where  $I_B$  is the bias current, and  $V_T$  is the thermal voltage. The bias currents and supply voltages were chosen as  $I_{B1}$  = 115  $\mu$ A,  $I_{B2}$  = 90  $\mu$ A and  $V_{CC}$  =  $-V_{EE}$  = 5 V, respectively. The values of the grounded capacitors and resistor were chosen as  $C_1$  =  $C_2$  = 5.5 nF and  $R_1$  = 1 k $\Omega$ , respectively. The calculated natural frequency and quality factor were  $f_0 = 50$  kHz and Q = 1, respectively. Figure 20 shows the frequency characteristics of the LP, HP, BP and BR filters. The experimental natural frequency was  $f_0 = 49$  kHz. However, for the experimental BR response, the attenuation was obtained around -35 dB due to nonideal characteristics of the VDDDA, as explained in Section 2.4. Figure 21 shows the gain response of the band-pass filter at different  $I_{B2}$  values (42  $\mu$ A, 90  $\mu$ A and 165  $\mu$ A). It is observed that the natural frequency is electronically tuned by the bias current  $I_{B2}$  without disturbing the bandwidth or quality factor. The electronic adjustability of the natural frequency via the bias current  $I_{B1}$  is shown in Figure 22. The experimental result shows that the natural frequency  $f_0 = 26 \text{ kHz}$ , 38 kHz and 49 kHz was obtained. The measured input and output waveforms of the BP filtering function are, respectively, shown in Figure 23, where a sine wave signal with a peak-to-peak value of 40 mVpp @ 5 kHz, 50 kHz and 500 kHz was applied to the input of the filter.

Figure 19. VDDDA based on the commercial components.

Figure 20. Experimental frequency characteristics of the proposed universal filter.

Sensors **2021**, 21, 1683 15 of 22

**Figure 21.** Experimental BP response for different bias current ( $I_{B2}$ ) values ( $I_{B1}$  = 155  $\mu$ A,  $R_1$  = 1  $k\Omega$  and  $C_1$  =  $C_2$  = 5.5 nF).

**Figure 22.** Experimental BP responses for different  $I_{B1}$  values ( $I_{B2}$  = 195  $\mu$ A,  $R_1$  = 1  $k\Omega$  and  $C_1$  =  $C_2$  = 5.5 nF).

Sensors 2021, 21, 1683 16 of 22

Figure 23. Measured BP filtering transient response.

Sensors **2021**, 21, 1683 17 of 22

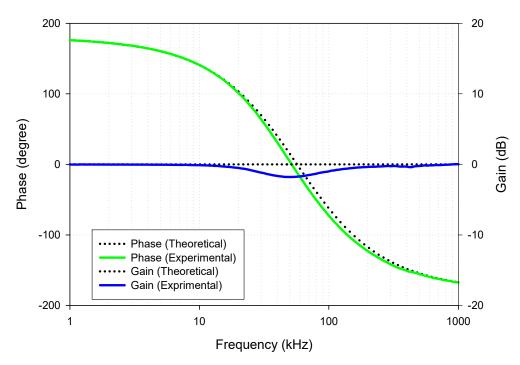

Next, the inverting all-pass biquad filter with unity voltage gain was tested by setting the transconductances  $g_{m1} = g_{m2}$  ( $I_{B1} = I_{B2} = 200 \,\mu\text{A}$ ) and applying the input voltage signal to the input voltage nodes,  $v_{i1}$ ,  $v_{i3}$  and  $v_{i4}$ , while the input voltage node  $v_{i2}$  was grounded. Although it requires the matching conditions of  $I_{B1}$  and  $I_{B2}$ , this is the active matching condition that is easier to control than the passive matching condition. The passive elements were still chosen as the resistor  $R_1 = 1 \, \text{k}$  and the capacitors  $C_1 = C_2 = 5.5 \, \text{nF}$ . Figure 24 shows the experimental phase and magnitude response of the proposed voltage-mode universal biquad filter. The graph shows that the output phase response of the AP filter is shifted from -180 to 180 degrees. However, at the frequency close to the natural frequency, the experimental voltage gain is slightly different from the ideal due to nonideal characteristics of the VDDDA, as explained in Section 2.4. The measured input and output waveforms of the AP filtering function are, respectively, shown in Figure 25a–c, where a sine wave signal with a peak-to-peak value of  $40 \, \text{mVpp} @ 5 \, \text{kHz}$ ,  $100 \, \text{kHz}$  and  $500 \, \text{kHz}$  was applied to the input of the filter. It appeared that the proposed filter can be used as the phase shifter circuit with constant output amplitude.

**Figure 24.** Experimental gain and phase response of the AP filer ( $I_{B1} = I_{B2} = 200 \mu A$ ,  $R_1 = 1$  k and  $C_1 = C_2 = 5.5$  nF).

Sensors 2021, 21, 1683 18 of 22

Figure 25. Measured AP filtering transient response.

Sensors **2021**, 21, 1683

## 5. Comparison

Table 1 compares the proposed universal biquad filter with previous biquad filters using the VDDDA [13-24]. These biquad filters are the multiple input multiple output (MIMO) [13,14,23], multiple input single output (MISO) [16,18,19,21,24] and single input multiple output (SIMO) [14,17,20,22] configurations. The design technique used in [13-15,17,19-22] were based on two integrator loops, while the filters in [16,18,23,24] were based on a passive RLC circuit. The proposed filter was designed from the parallel RLC circuit connecting with the voltage differencing circuit, and the VDDDA is very useful for this design. The RLC-based biquad filters proposed in references [16,18,23,24] were very simple circuitry with a single VDDDA as the active building block. Additionally, in [18,24], the  $f_0$  and Q were orthogonally controlled via the passive resistor. However, these biquad filters realized from the RLC circuit had the following disadvantages: for example, they consisted of a floating capacitor [16,18,24], the  $f_0$  and Q were not orthogonally controlled by changing the separated transconductance of the VDDDA [16,18,23,24], none of the highimpedance nodes and low-impedance nodes were given in references [16,18,23,24] and the unity gain inverting voltage amplifier or double-gain voltage amplifier was required for obtaining several filtering functions [16,18,24]. These limitations of the RLC-based filers have been improved in this work. The two-integrator loop-based biquad filters with high input impedance were obtained from references [13–15,17,22–25], and the low output impedance property for all output nodes was obtained from references [14,22,25]. In [13,14,20–22], the  $f_0$  and Q were orthogonally controlled by the separated transconductance. Additionally, the two VDDDA-based filters in reference [15] achieved orthogonal control of the  $f_0$  and Q via the passive resistor. Additionally, the  $f_0$  and Q of the proposed filters in references [13,14,20-22] could be linearly and independently controlled by simultaneously setting the transconductances in the integrator circuits. However, the biquad filter proposed in references [13,14,20-22] required three VDDDAs. Additionally, the passband voltage gain of the three VDDDA-based filters in references [13,14,22] were not constant during tuning the  $f_0$  and Q for some filtering responses. The two-integrator loop filter in references [15,17] could not provide five filter responses. Additionally, two VDDDA-based biquad filters in references [15,17,22] could not achieve orthogonal control of the  $f_0$  and Q by separated transconductance. The performances of the universal filers in references [13-18,23,24] were proved via simulation only, while both simulation and experiment were verified in this work.

Sensors **2021**, 21, 1683

**Table 1.** Comparison of the proposed biquad filter and other filters using VDDDA.

| Ref                | Filtering<br>Category | No. of<br>VDDDA | No. of R + C | Use of all<br>Grounded<br>Capacitors | High<br>Impedance<br>of all Input<br>Nodes | Low output<br>Impedance<br>for all<br>Output<br>Node | Electronic<br>Tune of Q<br>without<br>Affecting<br>$\omega_0$ | Filtering<br>Functions | Constant Passband Gain during Tuning ω <sub>0</sub> and Q for all Responses | Technology                               | Additional<br>Circuit                      | Results                        | Power supply<br>Voltages &<br>Power<br>Consumption* | Dynamic<br>Range &<br>Noise |

|--------------------|-----------------------|-----------------|--------------|--------------------------------------|--------------------------------------------|------------------------------------------------------|---------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------|------------------------------------------|--------------------------------------------|--------------------------------|-----------------------------------------------------|-----------------------------|

| [13]               | MIMO                  | 3               | 1 + 2        | Yes                                  | Yes                                        | No                                                   | Yes                                                           | LP, BP, HP,<br>BR, AP  | No                                                                          | 0.18 μm TSMC<br>CMOS                     | No                                         | Simulation                     | ±0.9 V & N/A                                        | N/A                         |

| [14]               | MIMO                  | 3               | 1 + 2        | Yes                                  | Yes                                        | No                                                   | Yes                                                           | LP, BP, HP,<br>BR, AP  | No                                                                          | 0.18 μm TSMC<br>CMOS                     | No                                         | Simulation                     | ±0.9 V & N/A                                        | N/A                         |

| [15]               | SIMO                  | 2               | 2 + 2        | Yes                                  | Yes                                        | No                                                   | No                                                            | LP, BP, HP             | Yes                                                                         | 0.18 μm TSMC<br>CMOS                     | No                                         | Simulation                     | ±0.9 V & N/A                                        | N/A                         |

| [16]               | MISO                  | 1               | 1 + 2        | No                                   | No                                         | No                                                   | No                                                            | LP, BP, HP,<br>BR, AP  | Yes                                                                         | 0.25 μm TSMC<br>CMOS                     | Inverting<br>Amp. &<br>double gain<br>Amp. | Simulation                     | ±1.25 V & 1.58<br>mW                                | N/A                         |

| [17]               | SIMO                  | 2               | 0 + 2        | Yes                                  | Yes                                        | No                                                   | No                                                            | LP, BP, HP,<br>BR      | Yes                                                                         | 0.18 μm TSMC<br>CMOS                     | No                                         | Simulation                     | ±0.9 V & 0.21<br>mW                                 | N/A                         |

| [18]               | MISO                  | 1               | 2 + 2        | No                                   | No                                         | No                                                   | No                                                            | LP, BP, HP,<br>BR, AP  | Yes                                                                         | 0.25 μm TSMC<br>CMOS                     | Inverting<br>Amp.                          | Simulation                     | ±1.25 V & N/A                                       | N/A                         |

| [19]               | MISO                  | 2               | 0 + 2        | Yes                                  | Yes                                        | Yes                                                  | No                                                            | LP, BP, HP,<br>BR, AP  | Yes                                                                         | Commercial ICs                           | No                                         | Simulation<br>&<br>Experiment  | ± 5 V                                               | N/A                         |

| [20]               | SIMO                  | 3               | 1 + 2        | Yes                                  | Yes                                        | No                                                   | Yes                                                           | LP, BP, HP,<br>BR, AP  | Yes                                                                         | 0.18 μm TSMC<br>CMOS &<br>Commercial ICs | No                                         | Simulation &<br>Experiment     | ±0.9 V & 0.34<br>mW                                 | N/A                         |

| [21]               | MISO                  | 3               | 1 + 2        | Yes                                  | Yes                                        | Yes                                                  | Yes                                                           | LP, BP, HP,<br>BR, AP  | Yes                                                                         | Commercial ICs                           | No                                         | Simulation<br>&Experi-<br>ment | ±5 V & N/A                                          | N/A                         |

| [22]               | SIMO                  | 3               | 1 + 2        | Yes                                  | Yes                                        | No                                                   | Yes                                                           | LP, BP, HP,<br>BR, AP  | No                                                                          | 0.18 μm TSMC<br>CMOS &<br>Commercial ICs | No                                         | Simulation &<br>Experiment     | ±0.9 V & N/A                                        | N/A                         |

| [23]               | MIMO                  | 1               | 1 + 2        | Yes                                  | Yes                                        | No                                                   | No                                                            | LP, BP                 | Yes                                                                         | 0.18 μm TSMC<br>CMOS                     | No                                         | Simulation                     | ±0.9 V & 0.73<br>mW                                 | N/A                         |

| [24]               | MISO                  | 1               | 2 + 2        | No                                   | No                                         | No                                                   | No                                                            | LP, BP, HP,<br>BR, AP  | Yes                                                                         | Commercial ICs                           | Inverting<br>Amp.                          | Simulation                     | ±5 V & N/A                                          | N/A                         |

| Proposed<br>Filter | MISO                  | 2               | 1 + 2        | Yes                                  | Yes                                        | Yes                                                  | Yes                                                           | LP, BP, HP,<br>BR, AP  | Yes                                                                         | 0.18 μm TSMC<br>CMOS &<br>Commercial ICs | No                                         | Simulation &<br>Experiment     | ±0.9 V & 0.99<br>mW                                 | 73.27 dB &<br>46 μVrms      |

<sup>\*</sup> The power consumption, dynamic range and noise are taken from the simulation. N/A: information not available/shown.

Sensors **2021**, 21, 1683 21 of 22

## 6. Conclusions

In this work, a new universal biquad filter using VDDDAs was proposed. The design technique used in this work was based on the parallel RLC circuit connecting with a voltage differencing circuit. The proposed filter is composed of two VDDDAs, one resistor and two grounded capacitors, which ensure reduction in a fabrication space and the compensation of parasitic effects. Five filtering responses with unity passband voltage gain are obtained. The AP response is achieved without matching by connecting the z terminal to the p terminal of VDDDA2. The  $f_0$  and Q are orthogonally controlled from separated transconductance ( $f_0$  is tuned by  $g_{m1}$ , and Q is tuned by  $g_{m2}$ ). This feature can be electronically controlled by implementing the VDDDA from the commercially available ICs. The performance and functionality of the proposed universal biquad filter were demonstrated with a simulation and experimental results, confirming the theory.

**Author Contributions:** Conceptualization, W.J. and F.K.; Methodology, W.J., F.K. and T.K.; Validation, W.J., F.K. and T.K.; Formal Analysis, W.J., F.K. and K.P.; Investigation, W.J., F.K. and K.P.; Writing—Original Draft Preparation, W.J. and F.K.; Writing—Review and Editing, W.J., F.K.; T.K. and K.P. All authors have read and agreed to the published version of the manuscript.

**Funding:** The research described in the paper was supported by the Faculty of Industrial Education and Technology, King Mongkut's Institute of Technology Ladkrabang (KMITL) under grant 2564-02-03-004.

**Acknowledgments:** The authors would like to thank the anonymous reviewers for providing valuable comments which helped improve the paper substantially.

**Conflicts of Interest:** The authors declare no conflict of interest.

## References

- 1. Myderrizi, I.; Minaei, M.; Yuce, E. An Electronically Fine-Tunable Multi-Input-Single-Output Universal Filter. *IEEE Trans. Biomed. Circuits Syst. II Express Briefs* **2011**, *58*, 356–360. [CrossRef]

- 2. Psychalinos, C. Log-domain SIMO and MISO low-voltage universal biquads. *Analog Integr. Circuits Signal Process.* **2011**, 67, 201–211. [CrossRef]

- 3. Yuce, E.; Tez, S. A Novel Voltage-Mode Universal Filter Composed of Two Terminal Active Devices. *AEU Int. J. Electron. Commun.* **2018**, *86*, 202–209. [CrossRef]

- 4. Ballo, A.; Grasso, A.D.; Pennisi, S.; Venezia, C. High-Frequency Low-Current Second-Order Bandpass Active Filter Topology and Its Design in 28-nm FD-SOI CMOS. *J. Low Power Electron. Appl.* **2020**, *10*, 27. [CrossRef]

- 5. Wang, S.F.; Chen, H.P.; Ku, Y.; Zhong, M.X. Voltage-mode multifunction biquad filter and its application as fully-uncoupled quadrature oscillator based on current-feedback operational amplifiers. *Sensors* **2020**, *20*, 6681. [CrossRef] [PubMed]

- Kumngern, M.; Aupithak, N.; Khateb, F.; Kulej, T. 0.5 V Fifth-Order Butterworth Low-Pass Filter Using Multiple-Input OTA for ECG Applications. Sensors 2020, 20, 7343. [CrossRef]

- 7. Prommee, P.; Wongprommoon, N.; Kumngern, M.; Jaikla, W. Low-voltage low-pass and band-pass elliptic filters based on log-domain approach suitable for biosensors. *Sensors* **2019**, *19*, 5581. [CrossRef]

- 8. Alpaslan, H.; Yuce, E. DVCC+ based multifunction and universal filters with the high input impedance features. *Analog Integr. Circuits Signal Process.* **2020**, *103*, 325–335. [CrossRef]

- 9. Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. A new low-voltage low-power dual-mode VCII-based simo universal filter. *Electronics* **2019**, *8*, 765. [CrossRef]

- 10. Psychalinos, C.; Kasimis, C.; Khateb, F. Multiple-input single-output universal biquad filter using single output operational transconductance amplifiers. *AEU Int. J. Electron. Commun.* **2018**, 93, 360–367. [CrossRef]

- 11. Pandey, N.; Nand, D.; Khan, Z. Single-Input Four-Output Current Mode Filter Using Operational Floating Current Conveyor. *Act. Passiv. Electron. Compon.* **2013**, 2013, 318560. [CrossRef]

- 12. Minaei, S.; Yuce, E. All-Grounded Passive Elements Voltage-Mode DVCC-Based Universal Filters. *Circuits Syst. Signal Process.* **2010**, 29, 295–309. [CrossRef]

- Koton, J.; Herencsar, N.; Vrba, K.; Metin, B. The VDDDA in multifunction filter with mutually independent Q and ω0 control feature. In Proceedings of the 8th International Conference on Electrical and Electronics Engineering, Bursa, Turkey, 28–30 November 2013; pp. 53–56.

- 14. Koton, J.; Herencsar, N.; Vrba, K.; Metin, B. Voltage-mode multifunction filter with mutually independent Q and control feature using VDDDAs. *Analog Integr. Circuits Signal Process.* **2014**, *81*, 53–60. [CrossRef]

- Soisang, S.; Jirasereemomkul, K.; Jaikla, W.; Higuchi, K. Voltage-Mode Multifunctional Biquadratic Filter Using VDDDA. Appl. Mech. Mater. 2015, 781, 155–159. [CrossRef]

Sensors **2021**, 21, 1683 22 of 22

16. Siripongdee, S.; Jaikla, W. Single VDDDA-based voltage-mode multifunction second order filter for analog signal processing. In Proceedings of the International Conference on Intelligent Informatics and Biomedical Sciences (ICIIBMS), Okinawa, Japan, 28–30 November 2015; pp. 39–42.

- 17. Chaimongkol, S.; Jaikla, W. A Voltage-Mode VDDDA-Based Universal Filter. In Proceedings of the International Symposium on Multimedia and Communication Technology, Ayutthaya, Thailand, 23–25 September 2015.

- 18. Chaichana, A.; Sangyaem, S.; Jaikla, W. Multifunction Voltage-Mode Filter Using Single Voltage Differencing Differential Difference Amplifier. In Proceedings of the International Conference on Mechatronics and Mechanical Engineering, Kuala Lumpur, Malaysia, 28–30 November 2017.

- 19. Sangyaem, S.; Siripongdee, S.; Jaikla, W.; Khateb, F. Five-inputs single-output voltage mode universal filter with high input and low output impedance using VDDDAs. *Optik* **2017**, *128*, 14–25. [CrossRef]

- 20. Tuntrakool, S.; Kumngern, M.; Sotner, R.; Herencsar, N.; Suwanjan, P.; Jaikla, W. High input impedance voltage-mode universal filter and its modification as quadrature oscillator using VDDDAs. *Indian J. Pure Appl. Phys.* **2017**, *55*, 324–332.

- 21. Supavarasuwat, P.; Kumngern, M.; Sangyaem, S.; Jaikla, W.; Khateb, F. Cascadable independently and electronically tunable voltage-mode universal filter with grounded passive components. *AEU Int. J. Electron. Commun.* **2018**, *84*, 290–299. [CrossRef]

- 22. Huaihongthong, P.; Chaichana, A.; Suwanjan, P.; Siripongdee, S.; Sunthonkanokpong, W.; Supavarasuwat, P.; Jaikla, W.; Khateb, F. Single-input multiple-output voltage-mode shadow filter based on VDDDAs. *AEU Int. J. Electron. Commun.* **2019**, 103, 13–23. [CrossRef]

- 23. Kulapong, W.; Siripongdee, S.; Jaikla, W. Design of Second Order Lowpass and Bandpass Filter Using Single VDDDA and Its Modification as Sinusoidal Oscillator. In Proceedings of the World Symposium on Communication Engineering (WSCE), Nagoya, Japan, 20–23 December 2019; pp. 152–156.

- 24. Thinthaworn, K.; Jaikla, W.; Suwanjan, P.; Adhan, S.; Srichaiya, N.; Kwawsibsame, A.; Khateb, F. A Compact Electronically Controllable Biquad Filter Synthesizing from Parallel Passive RLC Configuration. In Proceedings of the Annual Conference of the Society of Instrument and Control Engineers of Japan (SICE), Chiang Mai, Thailand, 23–26 September 2020; pp. 903–907.

- 25. Chen, H.P.; Hwang, Y.S.; Ku, Y.T.; Lin, T.J. Voltage-mode biquadratic filters using single DDCCTA. *AEU Int. J. Electron. Commun.* **2016**, *70*, 1403–1411. [CrossRef]

- 26. Phatsornsiri, P.; Kumngern, M.; Lamun, P. A Voltage-Mode Universal Biquadratic Filter Using DDCCTA. *J. Circuits Syst. Comput.* **2016**, 25, 1650034. [CrossRef]

- 27. Channumsin, O.; Pukkalanun, T.; Tangsrirat, W. Voltage-mode universal filter with one input and five outputs using DDCCTAs and all-grounded passive components. *Microelectron. J.* **2012**, *43*, 555–561. [CrossRef]

- 28. Khateb, F.; Kulej, T.; Kumngern, M.; Psychalinos, C. Multiple-input bulk-driven MOS transistor for low-voltage low-frequency applications. *Circuits Syst. Signal Process.* **2019**, *38*, 2829–2845. [CrossRef]

- 29. Khateb, F.; Kulej, T.; Veldandi, H.; Jaikla, W. Multiple-input bulk-driven quasi-floating-gate MOS transistor for low-voltage low-power integrated circuits. *AEU Int. J. Electron. Commun.* **2019**, 100, 32–38. [CrossRef]

- 30. Khateb, F.; Kulej, T.; Kumngern, K.; Jaikla, W.; Ranjan, R.K. Comparative performance study of multiple-input Bulk-driven and multiple-input Bulk-driven Quasi-floating-gate DDCCs. AEU Int. J. Electron. Commun. 2019, 108, 19–28. [CrossRef]

- 31. Kumngern, M.; Khateb, F.; Kulej, T. Extremely low-voltage low-power differential difference current conveyor using multiple-input bulk-driven technique. *AEU Int. J. Electron. Commun.* **2020**, *123*, 153310. [CrossRef]

- 32. Kumngern, M.; Khateb, F.; Kulej, T. 0.3 V Differential Difference Current Conveyor Using Multiple-Input Bulk-Driven Technique. *Circuits Syst. Signal Process.* **2020**, *39*, 3189–3205. [CrossRef]

- 33. Khateb, F.; Kumngern, M.; Kulej, T.; Psychalinos, C. 0.5 V Universal Filter Based on Multiple-Input FDDAs. *Circuits Syst. Signal Process.* **2019**, *38*, 5896–5907. [CrossRef]

- 34. Kumngern, M.; Kulej, T.; Khateb, F.; Stopjakova, V.; Ranjan, R.K. Nanopower multiple-input DTMOS OTA and its applications to high-order filters for biomedical systems. *AEU Int. J. Electron. Commun.* **2021**, *130*, 153576. [CrossRef]

- 35. Kumngern, M.; Kulej, T.; Stopjakova, V.; Khateb, F. 0.5 V Sixth-order Chebyshev band-pass filter based on multiple-input bulk-driven OTA. *AEU Int. J. Electron. Commun.* **2019**, *111*, 152930. [CrossRef]

- 36. Jaikla, W.; Khateb, F.; Kumngern, M.; Kulej, T.; Ranjan, R.K.; Suwanjan, P. 0.5 V Fully Differential Universal Filter Based on Multiple Input OTAs. *IEEE Access* **2020**, *8*, 187832–187839. [CrossRef]

- 37. Wyszynski, A.; Schaumann, R. Using multiple-input transconductors to reduce number of components in OTA-C filter design. *Electron. Lett.* **1992**, *28*, 217–220. [CrossRef]

- 38. Gopinathan, V.; Tsividis, Y.P.; Tan, K.-S.; Hester, R.K. Design considerations for high-frequency continuous-time filters and implementation of an antialiasing filter for digital video. *IEEE J. Solid State Circuits* **1990**, 25, 1368–1378. [CrossRef]

- 39. Lopez-Martin, A.J.; Ramirez-Angulo, J.; Carvajal, R.G.; Acosta, L. CMOS Transconductors With Continuous Tuning Using FGMOS Balanced Output Current Scaling. *IEEE J. Solid State Circuits* **2008**, *43*, 1313–1323. [CrossRef]

- 40. Rico-Aniles, H.D.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G. 360 nW Gate-Driven Ultra-Low Voltage CMOS Linear Transconductor with 1 MHz Bandwidth and Wide Input Range. *IEEE Trans. Circuits Syst. II Express Briefs* **2020**, 67, 2332–2336. [CrossRef]

- 41. Khateb, F.; Biolek, D. Bulk-Driven Current Differencing Transconductance Amplifier. *Circuits Syst. Signal Process.* **2011**, *30*, 1071–1089. [CrossRef]

- 42. Jaikla, W.; Sotner, R.; Khateb, F. Design and analysis of floating inductance simulators using VDDDAs and their applications. *AEU Int. J. Electron. Commun.* **2019**, *112*, 152937. [CrossRef]