Received February 17, 2021, accepted February 18, 2021, date of publication February 22, 2021, date of current version March 2, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3060939

# **Voltage-Mode Elliptic Band-Pass Filter Based on Multiple-Input Transconductor**

PIPAT PROMMEE<sup>®1</sup>, (Senior Member, IEEE), KHUNANON KARAWANICH<sup>1</sup>, FABIAN KHATEB<sup>®2,3</sup>, AND TOMASZ KULEJ<sup>®4</sup>

<sup>1</sup>Department of Telecommunications Engineering, School of Engineering, King Mongkut's Institute of Technology Ladkrabang, Bangkok 10520, Thailand

Corresponding author: Pipat Prommee (pipat.pr@kmitl.ac.th)

This work was supported by the School of Engineering, King Mongkut's Institute of Technology Ladkrabang.

**ABSTRACT** This paper presents a new voltage-mode elliptic band-pass filter based on a multiple-input transconductor (MI-OTA). The MI-OTA's structure employs the multiple-input MOS transistor technique that simply enables to increase the number of OTA's inputs without increasing the number of current branches or the differential pairs. The MI-OTA features high linearity over a wide input range with a compact and simple CMOS structure. From the advantage of multiple inputs, it enables to construct the arbitrarily summing and subtracting under the proposed voltage-mode filter design procedure. The filter is designed and simulated in Cadence environment using 0.18  $\mu$ m TSMC CMOS technology. The filter offers 72.9 dB dynamic range for 2 % total harmonic distortion (THD) for sine input signal of 0.5 Vpp @ 1kHz with voltage supply  $\pm$  0.9V. The simulation results of the filter are in agreement with the RLC prototype. The experimental results using commercially available IC are also included to confirm the proposed filter that are in good agreement with the simulation results.

**INDEX TERMS** Elliptic filter, band-pass filter, transconductor, multiple-input OTA.

# I. INTRODUCTION

The elliptic filter is an efficient type of a filtering circuit, which can find many applications in telecommunication, medical and other kinds of electronic systems. In the past, high-order ladder elliptic filters were always realized based on passive elements. Nowadays, such filters are realized rather in integrated form. Integrated filters should be electronically tunable to compensate for possible process, temperature and supply voltage (PVT) variations. Precise operation can be achieved using switched-capacitor (SC) realization, however, SC elliptic filters are rather complex, operate in discrete time and need floating capacitors [1], [2]. In 1992, Nauta [3] introduced an elliptic LPF using a simple linear transconductor, adjusted by its supply voltage. This realization was less complex than its SC counterparts, but the filter still required floating capacitors, as well as, precise controlling of supply voltage, that increased the overall complexity and power consumption. Over the next period, researchers presented elliptic LPFs using dual-output OTAs and the same

The associate editor coordinating the review of this manuscript and approving it for publication was Yong Chen .

design methods as in previous research [4]–[7]. These filters were relatively simple, but they still required floating capacitors and they could not be tuned [8]. Multiple feedback loop technique is another way to design active integrated filters [9]. Even though such filters use only grounded capacitors, their structures are rather complex and difficult to be tuned. There are also some other methods to design elliptic active filters in microelectronic technology, based on frequency dependent negative resistors (FDNR) [10], or combinations of OTAs and current conveyors [11]-[13], but they still show the disadvantages of the structures mentioned previously. The source follower-based biquad LPF [14], and its modification by capacitors feedback [15], were introduced but the frequency response cannot be tuned. The transistorized third-order LPF relied on RLC ladder prototype was presented but the electronically tunability cannot be achieved [16]. The two compact structures of LPF were presented with electronic tunability feature. The first LPF, floating emulated inductor and floating capacitors are required [17]. The second LPF, Chebyshev-II is introduced by adding floating capacitors to the core filter circuit [18]. The fourth-order LPF based on two cascaded second-order LPF cells was presented [19]. The

<sup>&</sup>lt;sup>2</sup>Department of Microelectronics, Brno University of Technology, 60190 Brno, Czech Republic

<sup>&</sup>lt;sup>3</sup>Faculty of Biomedical Engineering, Czech Technical University in Prague, 16636 Kladno, Czech Republic

<sup>&</sup>lt;sup>4</sup>Department of Electrical Engineering, Technical University of Czestochowa, 42-201 Częstochowa, Poland

| TABLE 1  | The comparison | of recent Elliptic BPF | with proposed | Ellintic DDE  |

|----------|----------------|------------------------|---------------|---------------|

| IABLE I. | ine comparison | of recent Elliptic BPF | with brobosea | EIIIDTIC BPF. |

|          | Technology              | VM/CM | Design<br>Technique           | Floating capacitors | Frequency<br>tuning | No. Active Element     | Complexity<br>Level (1-10) |

|----------|-------------------------|-------|-------------------------------|---------------------|---------------------|------------------------|----------------------------|

| [21]     | CMOS OA &<br>Switch Cap | VM    | SFG                           | Y                   | N                   | 7 OA +<br>80 MOS SW.   | 10                         |

| [22]     | CMOS<br>Transconductor  | VM    | Complexificatio n State space | Y                   | N                   | 24 OTA                 | 9                          |

| [23]     | MCDTA                   | CM    | Cascade 3<br>biquads          | N                   | Bias current        | 6 MCDTA+<br>Gain       | 8                          |

| [24]     | VDTA                    | VM    | GIC Network                   | Y                   | N                   | 5 VDTA                 | 8                          |

| [25]     | CMOS integrator         | CM    | SFG                           | N                   | Bias current        | 7 Integrators + Gain   | 8                          |

| [26]     | CMOS MO-OTA             | CM    | Multiple<br>Feedback Loop     | N                   | N                   | 7 OTA and 1 MO-<br>OTA | 8                          |

| [27]     | BJT/log-domain          | CM    | SFG                           | N                   | Bias current        | 8 log-cell             | 8                          |

| [28]     | CMOS MO-OTA             | CM    | SFG                           | N                   | Bias current        | 10 MO-OTA              | 7                          |

| Proposed | CMOS-MI-OTA             | VM    | SFG                           | N                   | R-Bias              | 9 MI-OTA               | 6                          |

floating capacitors were required and the frequency tunable had not reported. The second-order BPF using CMOS source feedback (SFB) was introduced with low-complex structure but not practically tuned the frequency response [20].

In this work we propose a new approach to design elliptic band-pass filters (BPF). In order to point out the advantages of the proposed approach, we compare our circuit with some previous works in Table 1. The significant advantage of the proposed approach, compared with other designs, is its smaller complexity. For example, in SC realizations, an external clock signal is required [21]. The OTA-C circuit in [22] is very complex and needs floating capacitors. In [23] a cascade of 3 biquad filters based on modified current differencing transconductance amplifier (MCDTA) and capacitors was applied. This realization requires a large number of transistors. In addition, the notch filter requires the adjustability of the current gain, which makes the circuit large, complex, and cumbersome to tune. Both, V/I and I/V converters are also required due to the current-mode approach.

In [24], inductor emulators are used with voltage differencing transconductance amplifier (VDTA) (internally consisting of 2 OTAs) to replace passive inductors. The circuit still uses many floating capacitors and provides no tuning. In [25] the integrator circuits are designed with signal flow graphs (SFG). Although the circuit operates at high frequency, it is highly complex due to many biasing current sources. In addition, both, V/I and I/V converters are required due to the current-mode operation. The multiple feedback loop realization in [26] is rather complex, because of a complex realization of the tuning function. The circuit operates in current-mode as well. The realization in [27] is based on log-domain integrators and differentiators. It requires a large number of bias currents and consume high power due to the bipolar technology used in this design. Similar techniques are applied with 10 MO-OTAs operated in current-mode [28]. Although this reduces the complexity, the V/I and I/V conversion circuits are required as well.

This article presents a new solution for an elliptic BPF, which is less complex than competitive designs. The circuit is based on multiple-input OTAs (MI-OTA), operating as integrators or differentiators, and uses only grounded

capacitors. The frequency response can be tuned with regulating the transconductance of MI-OTA. Relatively low number of active components was achieved thanks to the use of the summing function of MI-OTA. The circuit operates in a voltage-mode.

The paper is organized as follows: Sections 2 describes the multiple-input transconductance stage. Section 3 presents the voltage-mode band-pass elliptic filter application. Section 4 and 5 include the simulation and experimental results, respectively. Finally, section 6 concludes the paper.

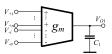

## II. THE MULTIPLE-INPUT TRANSCONDUCTANCE STAGE

Voltage-to-current converter known as a transconductor or OTA is a basic building block for analog signal processing systems [29]-[31]. One of the effective linearization techniques for this block is the use of a voltage follower (VF), created by a negative feedback connection, linear resistor (R) connected to the output of the VF and a current mirror at the output stage of the VF [34]–[39]. This linearization technique provides a wide range of transconductance tuning without degrading other parameters like input range and linearity [34]–[39]. Although this technique had been used previously in several works, the CMOS structures could be further improved in order to reduce the count of transistors, chip area, and power consumption without degrading the circuit's performances. The transconductor in [32] offers only single input that limits its applications. The transconductors in [33]-[39] offer differential input, however, these CMOS structures are constructed by two voltage to current (V-I) conversion units (VF or current conveyor) that increase the chip area and the total power consumption. The transconductor in [40] offers differential input with single V-I conversion unit based on promising structure of differential difference current conveyor (DDCC). Although this transconductor use one V-I conversion unit its CMOS structure use two differential pairs that increase the number of current branches, power consumption and the chip area. Therefore, the presented transconductor has a differential input with one multiple-input V-I conversion unit and one differential pair (instead of conventional two pairs) by using the multipleinput MOS transistor technique [41]-[47].

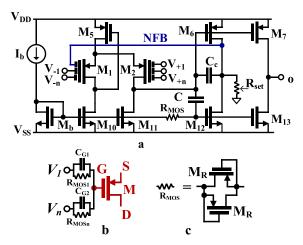

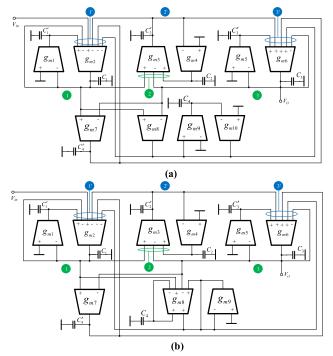

FIGURE 1. a) The CMOS structure of the multiple-input transconductor, b) realization of the MI transistor, and c) realization of the R<sub>MOS</sub> resistor.

The compact and innovative structure of the OTA is shown in Fig. 1 (a). The structure is based on a two-stage OTA with a negative feedback connection (NFB) that convey the differential input voltage  $(V_{id} = (V_{+1} + ... V_{+n}) - (V_{-1} + ... V_{-n}))$  to the output which is connected to a linear resistor  $(R_{set})$ . This  $R_{set}$  performs the V-I conversion where  $I_{Rset} = V_{id}/R_{set}$ . The output current of the linear resistor  $I_{Rset}$  is copied to the output (o) of the OTA using simple current mirrors  $(M_6-M_7)$  and  $M_{12}-M_{13}$ . The transconductance value of the transconductor is then given by [32]:

$$G_{mset} = \frac{g_m}{1 + g_m R_{set}} \tag{1}$$

where  $g_m$  is the internal transconductance of the transconductance. For  $R_{set} \gg 1/g_m$ , the transconductance  $G_{mset}$  can be approximated as follows:

$$G_{mset} \approx 1/R_{set}$$

(2)

Note, that there are several ways to achieve electric tuning for this OTA, for example using a resistor divider to split the resistor current [37], using digitally programmable resistor to adjust the current attenuation [40] or simply using an MOS transistor operating in a triode region [32].

The MI-OTA in Fig. 1 (a) has one differential stage  $M_1$ ,  $M_2$ ,  $M_5$ ,  $M_{10}$ ,  $M_{11}$ . The differential pair  $M_1$ ,  $M_2$  is based on multiple-input technique. The realization of this MI MOS transistor is shown in Fig. 1 (b) where the input gate "G" of transistor M is connected to arbitrary n number of inputs by n number of couples of capacitor  $C_G$  and a high resistance MOS resistor  $R_{MOS}$  realized by two transistors  $M_R$  operating in a cut-off region as shown in Fig. 1 (c). The first and second output stages of the OTA is created by  $M_6$ ,  $M_{12}$  and  $M_7$ ,  $M_{13}$ , respectively. The  $R_{set}$  is connected to the first output stage and set the value of the OTA's transconductance. The output current is obtained from the second stage of the OTA. The capacitor C along with  $R_{MOS}$  create a simple class AB output stage [39]. The compensation capacitor  $C_c$  is used to ensure the stability of the transconductor. The bias current  $I_b$  and

transistor  $M_b$  set the currents of the circuits. Note, that the multiple-input technique gives a freedom to simply increase the number of inputs without increasing the number of current branches or the differential pairs, hence the circuit structure is kept as simple as possible.

# III. THE VOLTAGE-MODE BAND-PASS ELLIPTIC FILTER APPLICATION

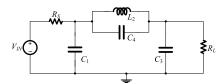

The design of the proposed BPF is based on an LPF RLC prototype shown in Fig. 2. The network transformation method, and signal flow graph technique are used to form an active BPF circuit operating in a voltage-mode. Finally, the branches of SFG are replaced by MI-OTA circuits. The good performances, and the tunability of frequency response can be achieved with low-complexity structure.

FIGURE 2. RLC elliptic LPF prototype.

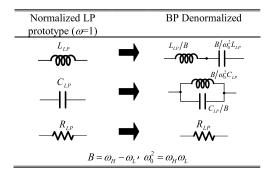

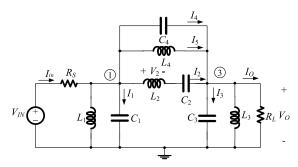

According to the network transformation method [48], the elements of the LPF prototype are replaced with elements of a BPF prototype as illustrated in Table 2. The transformed RLC elliptic BPF is shown in Fig. 3.

**TABLE 2.** Network transformation between LPF and BPF.

FIGURE 3. Transformed RLC elliptic BPF using LPF prototype.

Using KCL in Fig. 3, the currents and voltage relationship of each designated node or branch can be written as (3)-(12)

$$\frac{V_{in} - V_1}{R_S} = I_{in} \tag{3}$$

$$V_1 = \frac{I_1}{sC_1} \tag{4}$$

$$I_1 = \frac{(V_{in} - V_1)}{R_S} - I_2 - I_4 - I_5 - \frac{V_1}{sL_1}$$

(5)

$$V_2 = V_1 - V_3 - \frac{I_2}{sC_2} \tag{6}$$

$$I_2 = \frac{V_2}{sL_2} \tag{7}$$

$$I_3 = I_2 + I_4 + I_5 - \frac{V_3}{sI_2} - \frac{V_3}{R_I}$$

(8)

$$V_3 = \frac{I_3}{sC_3} \tag{9}$$

$$I_4 = \frac{V_1 - V_3}{sL_4} \tag{10}$$

$$I_5 = (V_1 - V_3)sC_4 (11)$$

$$I_4 + I_5 = (V_1 - V_3) \left(\frac{1}{sL_4} + sC_4\right)$$

(12)

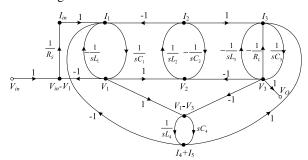

From (3)-(12), the first signal flow graph can be created as shown in Fig. 4. Some nodes of this graph represent current variables, while we need voltage variables for a voltage-mode circuit. Suppose that, the doubly terminated resistors are equal to each other  $(R_S = R_L = R)$  and the transconductance of OTA is assumed to be  $g_m = 1/R$ . The current variables can be transformed into voltage variables by incorporating the transconductance  $(g_m)$  in suitable branches, thus achieving a new graph, with voltage variables only. The new graph is shown in Fig. 5.

FIGURE 4. First signal flow graph using RLC based elliptic BPF.

FIGURE 5. Voltage-mode signal flow graph of elliptic BPF.

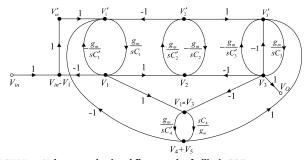

# A. OTA-BASED VOLTAGE-MODE MULTIPLE-INPUT INTEGRATOR

The voltage-mode integrator used in this design is a lossless integrator. It can easily be created by using OTA and a

FIGURE 6. OTA-based multiple-input lossless integrator.

FIGURE 7. OTA-based multiple-input lossless integrator.

grounded capacitor as shown in Fig. 6. The output voltage of the multiple-input lossless integrator can be expressed by:

$$V_{O1} = \sum_{i=1}^{n} (V_{+i} - V_{-i}) \frac{g_m}{sC_1}$$

(13)

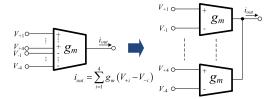

### B. OTA-BASED VOLTAGE-MODE DIFFERENTIATORS

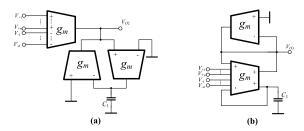

The voltage-mode lossless differentiator used in this design can be realized in two ways. Type 1 can be realized using 3 OTAs, while Type 2 can be realized using 2 OTAs and a grounded capacitor, as shown in Fig. 7 (a) and (b), respectively. The output voltage of both circuits can be expressed as:

$$V_{O2} = V_{O3} = \sum_{i=1}^{n} (V_{+i} - V_{-i}) \frac{sC_1}{g_m}$$

(14)

# C. REALIZATION OF A VOLTAGE-MODE ELLIPTIC BPF USING MI-OTA

Using the SFG in Fig. 5, the voltage-mode elliptic BPF can be realized with the integrators and differentiators discussed in sections 3.1 and 3.2. The summations and subtractions can be obtained by using the multiple inputs of OTA, which simplifies the overall design. Based on the type 1 differentiator, the elliptic BPF can be realized using 10 MI-OTAs and 8 capacitors as shown in Fig.8 (a). From Fig. 8, the maximum of four inputs (n=4) of MI-OTA are required. Note that, the unused inputs are grounded. The number of the used MI-OTAs can be decreased if one of the used MI-OTAs has dual positive output. Based on the type 2 differentiator, the elliptic BPF type 2 is realized with 9 MI-OTAs and 8 capacitors as shown in Fig. 8 (b).

## **IV. SIMULATION RESULTS**

The circuit was simulated and designed in Cadence environment using 0.18 $\mu$ m TSMC technology. The transistors aspect ratio in Fig. 1 are: M<sub>1</sub>, M<sub>2</sub> = 90 $\mu$ m/3 $\mu$ m, M<sub>5</sub>, M<sub>6</sub>, M<sub>7</sub> = 2 × 90 $\mu$ m /3 $\mu$ m, M<sub>10</sub>, M<sub>11</sub>, M<sub>b</sub> = 30  $\mu$ m /3  $\mu$ m, M<sub>12</sub>, M<sub>13</sub> = 2×30 $\mu$ m /3 $\mu$ m, M<sub>R</sub> = 4 $\mu$ m/5 $\mu$ m. The value of

FIGURE 8. Multiple OTA-C based elliptic BPF (a) Type 1 (b) Type 2.

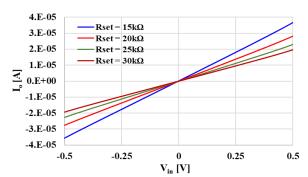

FIGURE 9. The transfer characteristic of the MI-OTA for different R<sub>set</sub>.

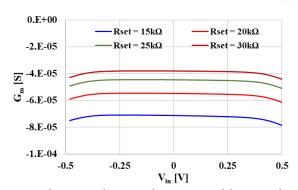

FIGURE 10. The transconductance value versus  $\mathbf{V}_{in}$  of the MI-OTA for different  $\mathbf{R}_{set}$ .

capacitors are:  $C_c$ , C=2.6 pF,  $C_{in}=0.5$ pF. The bias current  $I_b=50~\mu A$  and the total power consumption is  $630\mu W$  for one-output OTA and  $810~\mu W$  for two-output OTA.

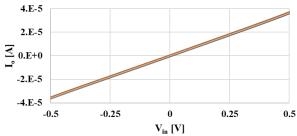

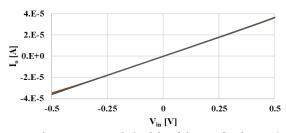

Figs. 9 and 10 show the transfer characteristic and the transconductance value versus Vin of the MI-OTA for different  $R_{set}$  (15k $\Omega$ , 20 k $\Omega$ , 25 k $\Omega$ , 30 k $\Omega$ ). The MI-OTA shows good tunability and linearity in the range of -0.5 to 0.5V. The

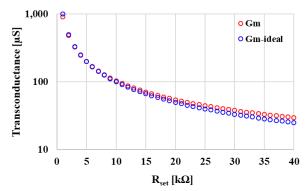

FIGURE 11. The transconductance value of the simulated and ideal OTA versus  $\mathbf{R}_{\text{set}}.$

FIGURE 12. The Monte Carlo analysis of the transfer characteristic of the MI-OTA for  $R_{set}=15k\Omega.$

FIGURE 13. The PVT corner analysis of the of the transfer characteristic of the MI-OTA for  $R_{set}=15k\Omega.$

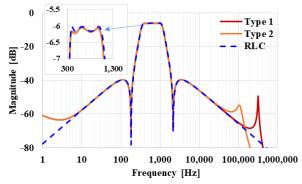

FIGURE 14. The frequency characteristics for the filters and RLC.

relation of the simulated and ideal transconductance versus  $R_{set}$  is shown in Fig. 11, where the curves match for lower value of  $R_{set}$ .

The Monte Carlo (MC) analysis with 200 runs and the process, voltage, temperature corners are shown in Figs. 12 and 13, respectively. The process corner for the MOS transistor are (ss, sf, fs, ff), for capacitors (fast, slow), for voltage supply ( $V_{DD} = -V_{SS} = 890 \text{mV}$ , 910 mV), for

FIGURE 15. The tunability of the 2 types filters for different R<sub>set</sub>.

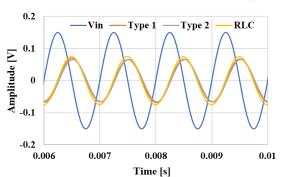

FIGURE 16. The transient characteristic of the filters with input sine wave of 300mVpp @1 kHz.

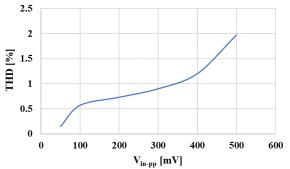

FIGURE 17. The THD versus peak-to-peak input signal @ 1 kHz.

temperature ( $-10^{\circ}$ C,  $70^{\circ}$ C). As it is shown, the deviation is in acceptable range.

Using the values of passive elements as in Table 3, the frequency characteristics of the proposed BPF filter and its RLC prototype are shown in Fig. 14. For Type 1 the bandwidth (BW)=844.2Hz, mid band gain = -0.605dB, for Type 2 the BW=845.2Hz, mid band gain = -0.605dB, for RLC the

FIGURE 18. Four-input MI-OTA realized with four single-input OTAs.

FIGURE 19. Experimental setup of the proposed elliptic band-pass filer.

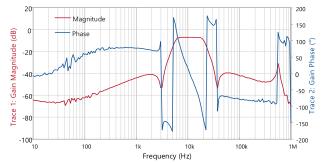

FIGURE 20. Magnitude and phase response of proposed elliptic band-pass filer for  $I_B=60\,\mu\text{A}$ .

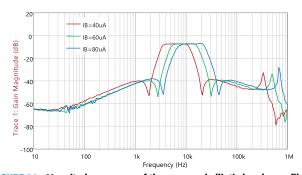

**FIGURE 21.** Magnitude response of the proposed elliptic band-pass filer for  $I_B=40,60$  and  $80\mu A$ .

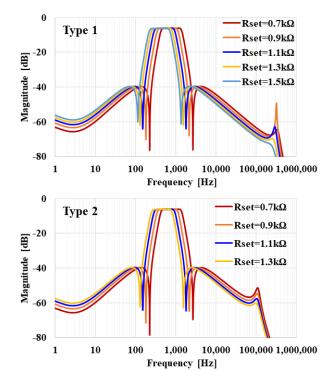

BW=858.3Hz, mid band gain = -0.602dB. The -3dB band pass is around 334 Hz - 1.1 kHz. The tunability of the filters for different  $R_{set} = 0.7$ kΩ, 0.9 kΩ, 1.1 kΩ, 1.3 kΩ, 1.5 kΩ is shown in Fig. 15.

The transient characteristic of the filters with input sine wave of 300mVpp @1 kHz is shown in Fig. 16, the total harmonic distortion (THD) was 0.9%. The THD versus the input peak-to-peak signal is shown in Fig. 17. The simulated value of the output noise was  $40\mu Vrms$  hence the dynamic range of the filter was 72.9 dB for 2% THD.

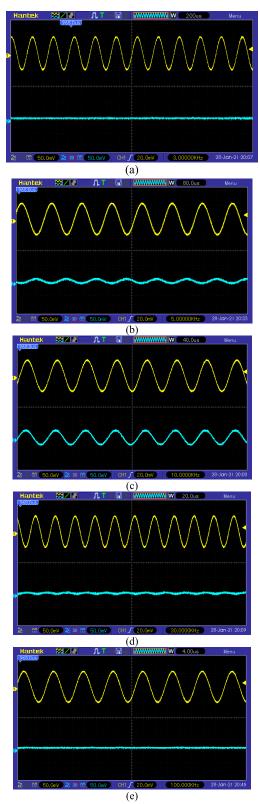

**FIGURE 22.** Output and input signals of the proposed elliptic BPF at  $I_B=60\mu \text{A}$  ( $I_0=10 \text{kHz}$ ) for different frequencies (input is upper trace and output is lower trace) (a) 3kHz, (b) 5kHz (c) 10kHz (d) 30kHz (e) 100kHz.

# V. EXPERIMENTAL RESULTS

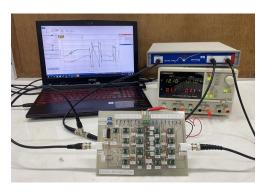

In addition, to confirm practical operation of the proposed BPF, the experiment was conducted using commercially

TABLE 3. The Passive Elements used in the elliptic BPF.

| Prototype                     | MI-OTA*                    | LT1228*                  |

|-------------------------------|----------------------------|--------------------------|

| $C_1 = C_2 = C_3 = 250 \mu F$ | $C_1 = C_2 = C_3 = 250 nF$ | $C_1 = C_2 = C_3 = 10nF$ |

| $L_1 = L_2 = L_3 = 250 \mu H$ | $C'_1=C'_2=C'_3=250nF$     | $C'_1=C'_2=C'_3=10nF$    |

| $C_4=25\mu F$                 | $C_4=25nF$                 | $C_4=1nF$                |

| $L_4 = 2.5 \text{mH}$         | C' <sub>4</sub> =2500nF    | C' <sub>4</sub> =100nF   |

\*For OTA, possible to use the same scaled factor  $(1/k_m)$  with every passive elements of prototype (for example  $k_m$ =100)

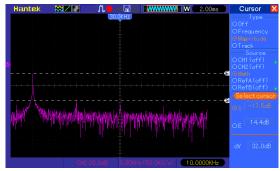

FIGURE 23. Output spectrum of the elliptic BPF when input applied 100mVpp/10kHz with  $I_B=60\mu A$ .

available OTA (LT1228) with  $\pm 12V$  power supply. The values of the used capacitors were  $C_1 = C_2 = C_3 = C_1' = C_2' = C_3' = 10$ nF,  $C_4 = 1$ nF,  $C_4' = 10$ 0nF. The four-input MI-OTA was implemented using four OTAs, as shown in Fig. 18. The experimental setup is shown in Fig. 19. For measurement of the frequency characteristics, the Bode 100 vector network analyzer has been used.

Fig. 20 shows the magnitude and phase response at  $I_B = 60\mu\text{A}$ . The center frequency  $(f_0)$  was around 10kHz, -40dB stop-band and 15kHz bandwidth agree well with simulations. The phase shift was around  $10^{\circ}$  at f = 10kHz. The filter tunability was verified by adjusting the bias current between  $40\mu\text{A}$  and  $80\mu\text{A}$  as shown in Fig. 21. The magnitude response of the proposed elliptic band-pass filer, for different  $I_B$ , was in agreement with simulation results.

The transient response of the filter was verified by applying an input sine-wave signal with 100mVpp amplitude and five different frequencies (1kHz, 3kHz, 10kHz, 30kHz and 100kHz), with  $I_B = 60\mu$ A. From Fig. 22, the filter can provide the sinusoidal output signal at passband frequency ( $f_0 = 10$ kHz), while other frequencies cannot be passed to the output. The results of transient response agreed well with the magnitude and phase response in Fig. 20.

Given the bias current  $I_B = 60\mu A$  for  $f_0 = 10 kHz$ , the sinusoidal signal with amplitude of 100 mVpp was applied at the input of the proposed filter. The filter provides an output sine-wave signal as shown in Fig. 22(c) and its spectrum is shown in Fig. 23. The measured  $HD_2$ ,  $HD_3$  and  $HD_4$  harmonic distortions compared to the fundamental frequency (10 kHz) were equal to -32 dB, -36 dB and -38 dB, respectively. Thus, the calculated THD was 3.2%.

### VI. CONCLUSION

This paper presents a new voltage-mode elliptic Band-pass Filter based on multiple-input transconductor. As it was

shown, the MI-OTA facilitates filter's construction with less count of active elements and with reduced complexity, compared with other solutions presented in literature. Thanks to the unity gain negative feedback and the capacitive divider, the linearity of the OTA is increased. The proposed circuit was designed in Cadence environment using 0.18  $\mu$ m TSMC CMOS technology. Intensive simulation results including Monte Carlo and PVT analysis are presented. The simulation and experimental results prove the advantages of the proposed filter

# **REFERENCES**

- M. Banu and Y. Tsividis, "An elliptic continuous-time CMOS filter with on-chip automatic tuning," *IEEE J. Solid-State Circuits*, vol. 20, no. 6, pp. 1114–1121, Dec. 1985, doi: 10.1109/jssc.1985.1052448.

- [2] M.S. Tawfik and P. Senn, "A 3.6-MHz cutoff frequency CMOS elliptic low-pass switched-capacitor ladder filter for video communication," *IEEE J. Solid-State Circuits*, vol. 22, no. 3, pp. 378–384, Jun. 1987, doi: 10.1109/jssc.1987.1052735.

- [3] B. Nauta, "A CMOS transconductance-C filter technique for very high frequencies," *IEEE J. Solid-State Circuits*, vol. 27, no. 2, pp. 142–153, Feb. 1992. doi: 10.1109/4.127337.

- [4] W. R. Daasch, M. Wedlake, and R. Schaumann, "Automatic generation of CMOS continuous-time elliptic filters," *Electron. Lett.*, vol. 28, no. 24, pp. 2215–2216, Nov. 1992, doi: 10.1049/el:19921423.

- [5] S. Lindfors, K. Halonen, and M. Ismail, "A 2.7-V elliptical MOSFET-only gmC-OTA filter," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 47, no. 2, pp. 89–95, Feb. 2000, doi: 10.1109/82.821548.

- [6] T. K. Nguyen and S. Lee, "Low voltage, low power CMOS fifth order Elliptic low pass gm-c filter for direct conversion receiver," in *Proc. Asia–Pacific Microw. Conf.*, 2003, pp. 1–4.

- [7] J. F. Fernandez-Bootello, M. Delgado-Restituto, and A. Rodriguez-Vazquez, "A 0.18-\(\mu\)m CMOS low-noise highly linear continuous-time seventh-order Elliptic low-pass filter," *Proc. SPIE*, vol. 5837, pp. 148–157, Jun. 2005, doi: 10.1117/12.608294.

- [8] Y. Lu, R. Krithivasan, W. L. Kuo, X. Li, J. D. Cressler, H. Gustat, and B. Heinemann, "A 70 MHz-4.1 GHz 5th-order elliptic GM-C low-pass filter in complementary SiGe technology," in *Proc. Bipolar/BiCMOS Circuits Technol. Meeting*, Oct. 2006, pp. 1–4, doi: 10.1109/BIPOL.2006.311118.

- [9] X. Zhu, Y. Sun, and J. Moritz, "Design of current-mode Gm-C MLF elliptic filters for wireless receivers," in *Proc. 15th IEEE Int. Conf. Electron.*, Circuits Syst., Sep. 2008, pp. 296–299, doi: 10.1109/icecs.2008.4674849.

- [10] F. Kaçar, "A new tunable floating CMOS FDNR and elliptic filter applications," *J. Circuits, Syst., Comput.*, vol. 19, no. 8, pp. 1641–1650, 2010, doi: 10.1142/S0218126610006967.

- [11] J. Bang, J. Song, I. Ryu, and S. Jo, "A CMOS 5th elliptic Gm-C filter using a new fully differential transconductor," *Int. J. Control Autom.*, vol. 6, no. 6, pp. 115–126, Dec. 2013, doi: 10.14257/IJCA.2013.6.6.12.

- [12] L. Sesnic, D. Jurisic, and B. Lutovac, "Elliptic biquadratic sections using second generation current conveyors (CCIIs)," in *Proc. 3rd Medit. Conf. Embedded Comput. (MECO)*, Budva, Montenegro, Jun. 2014, pp. 173–176, doi: 10.1109/MECO.2014.6862686.

- [13] S. Ghamari, G. Tasselli, C. Botteron, and P.-A. Farine, "A wide tuning range 4 th-order Gm-C elliptic filter for wideband multi-standards GNSS receivers," in *Proc. ESSCIRC Conf. 41st Eur. Solid-State Circuits Conf.* (ESSCIRC), Sep. 2015, pp. 40–43, doi: 10.1109/esscirc.2015.7313823.

- [14] S. D'Amico, M. Conta, and A. Baschirotto, "A 4.1-mW 10-MHz fourth-order source-follower-based continuous-time filter with 79-dB DR," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2713–2719, Dec. 2006, doi: 10.1109/JSSC.2006.884191.

- [15] Y. Chen, P.-I. Mak, and Y. Zhou, "Source-follower-based bi-quad cell for continuous-time zero-pole type filters," in *Proc. IEEE Int. Symp. Circuits* Syst., May 2010, pp. 3629–3632, doi: 10.1109/ISCAS.2010.5537781.

- [16] Y. Chen, P.-I. Mak, L. Zhang, H. Qian, and Y. Wang, "A fifth-order 20-MHz transistorized-LC -ladder LPF with 58.2-dB SFDR, 68-μW/Pole/MHz efficiency, and 0.13-mm² die size in 90-nm CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 60, no. 1, pp. 11–15, Jan. 2013, doi: 10.1109/TCSII.2012.2234894.

- [17] Y. Chen, P. Mak, L. Zhang, H. Qian, and Y. Wang, "0.013 mm 2, kHz-to-GHz-bandwidth, third-order all-pole lowpass filter with 0.52-to-1.11 pW/pole/Hz efficiency," *Electron. Lett.*, vol. 49, no. 21, pp. 1340–1342, Oct. 2013, doi: 10.1049/el.2013.2670.

- [18] Y. Chen, P. I. Mak, S. D'Amico, L. Zhang, H. Qian, and Y. Wang, "A single-branch third-order pole-zero low-pass filter with 0.014-mm<sup>2</sup> die size and 0.8-kHz (1.25-nW) to 0.94-GHz (3.99-mW) bandwidth-power scalability mixed-integrator biquad for continuous-time filters," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 60, no. 11, pp. 761–765, Jan. 2013, doi: 10.1109/TCSII.2013.2281717.

- [19] Y. Chen, P.-I. Mak, and Y. Zhou, "Mixed-integrator biquad for continuoustime filters," *Electron. Lett.*, vol. 46, no. 8, p. 561, Apr. 2010, doi: 10.1049/el.2010.0544.

- [20] Y. Chen, P.-I. Mak, L. Zhang, and Y. Wang, "0.07 mm2, 2 mW, 75 MHz-IF, fourth-order BPF using source-follower-based resonator in 90 nm CMOS," *Electron. Lett.*, vol. 48, no. 10, p. 552, 2012, doi: 10.1049/el.2012.0579.

- [21] T. C. Choi, R. T. Kaneshiro, R. W. Brodersen, P. R. Gray, W. B. Jett, and M. Wilcox, "High-frequency CMOS switched-capacitor filters for communications application," *IEEE J. Solid-State Circuits*, vol. 18, no. 6, pp. 652–664, Dec. 1983, doi: 10.1109/JSSC.1983.1052015.

- [22] J. Mahattanakul and P. Khumsat, "Structure of complex elliptic Gm-C filters suitable for fully differential implementation," *IET Circuits*, *Devices Syst.*, vol. 1, no. 4, pp. 275–282, Aug. 2007, doi: 10.1049/iet-cds:20060344.

- [23] Y. Li, "Current-mode sixth-order elliptic band-pass filter using MCDTAs," Radioengineering, vol. 20, no. 3, p. 645, Sep. 2011.

- [24] A. A. M. Shkir, "10kHz, low power, 8th order Elliptic band-pass filter employing CMOS VDTA," *Int. J. Enhanced Res. Sci. Technol. Eng.*, vol. 2, no. 4, pp. 162–168, 2013.

- [25] E. Saising, T. Pattanathadapong, and P. Prommee, "CMOS-based current-mode elliptic ladder band-pass filter," *Appl. Mech. Mater.*, vol. 781, pp. 168–171, Aug. 2015, doi: 10.4028/www.scientific.net/amm.781.168.

- [26] K. Ghosh and B. N. Ray, "Design of high-order Elliptic filter from a versatile mode generic OTA-C structure," *Int. J. Electron.*, vol. 102, no. 3, pp. 392–406, 2015, doi: 10.1080/00207217.2014.896423.

- [27] P. Prommee, N. Wongprommoon, M. Kumngern, and W. Jaikla, "Low-voltage low-pass and band-pass elliptic filters based on log-domain approach suitable for biosensors," *Sensors*, vol. 19, no. 24, p. 5581, Dec. 2019, doi: 10.3390/s19245581.

- [28] P. Prommee, N. Wongprommoon, F. Khateb, and N. Manositthichai, "Simple structure OTA-C elliptic band-pass filter," in *Proc. 16th Int. Conf. Electr. Eng./Electron., Comput., Telecommun. Inf. Technol. (ECTI-CON)*, Jul. 2019, pp. 729–732, doi: 10.1109/ecti-con47248.2019.8955258.

- [29] M. Renteria-Pinon, J. Ramirez-Angulo, and A. Diaz-Sanchez, "Simple scheme for the implementation of low voltage fully differential amplifiers without output common-mode feedback network," *J. Low Power Electron. Appl.*, vol. 10, no. 4, p. 34, Oct. 2020, doi: 10.3390/jlpea10040034.

- [30] A. Richelli, L. Colalongo, Z. Kovacs-Vajna, G. Calvetti, D. Ferrari, M. Finanzini, S. Pinetti, E. Prevosti, J. Savoldelli, and S. Scarlassara, "A survey of low voltage and low power amplifier topologies," *J. Low Power Electron. Appl.*, vol. 8, no. 3, p. 22, Jun. 2018, doi: 10.3390/jlpea8030022.

- [31] E. Bharucha, H. Sepehrian, and B. Gosselin, "A survey of neural front end amplifiers and their requirements toward practical neural interfaces," *J. Low Power Electron. Appl.*, vol. 4, no. 4, pp. 268–291, Nov. 2014, doi: 10.3390/jlpea4040268.

- [32] F. Khateb and D. Biolek, "Bulk-driven current differencing transconductance amplifier," *Circuits, Syst., Signal Process.*, vol. 30, no. 5, pp. 1071–1089, 2011, doi: 10.1007/s00034-010-9254-9.

- [33] H. D. Rico-Aniles, J. Ramirez-Angulo, A. J. Lopez-Martin, and R. G. Carvajal, "360 nW gate-driven ultra-low voltage CMOS linear transconductor with 1 MHz bandwidth and wide input range," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 11, pp. 2332–2336, Nov. 2020, doi: 10.1109/TCSII.2020.2968246.

- [34] A. J. López-Martín, J. Ramírez-Angulo, C. Durbha, and R. G. Carvajal, "A CMOS transconductor with multidecade tuning using balanced current scaling in moderate inversion," *IEEE J. Solid-State Circuits*, vol. 40, no. 5, pp. 1078–1083, May 2005, doi: 10.1109/JSSC.2005.845980.

- [35] A. J. Lopez-Martin, J. Ramirez-Angulo, R. G. Carvajal, and L. Acosta, "CMOS transconductors with continuous tuning using FGMOS balanced output current scaling," *IEEE J. Solid-State Circuits*, vol. 43, no. 5, pp. 1313–1323, May 2008, doi: 10.1109/JSSC.2008.920333.

- [36] J. M. A. Miguel, A. J. Lopez-Martin, L. Acosta, J. Ramirez-Angulo, and R. G. Carvajal, "Using floating gate and quasi-floating gate techniques for rail-to-rail tunable CMOS transconductor design," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 7, pp. 1604–1614, Jul. 2011, doi: 10.1109/TCSI.2011.2157782.

- [37] J. M. Algueta, A. J. Lopez-Martin, J. Ramirez-Angulo, and R. G. Carvajal, "Improved technique for continuous tuning of CMOS transconductor," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2013, pp. 1288–1291, doi: 10.1109/ISCAS.2013.6572089.

- [38] A. J. Lopez-Martin, J. Ramirez-Angulo, and R. G. Carvajal, "Highly accurate CMOS second generation current conveyor and transconductor," in *Proc. IEEE EUROCON Int. Conf. Comput. Tool (EUROCON)*, Sep. 2015, pp. 1–4, doi: 10.1109/EUROCON.2015.7313765.

- [39] A. Carlos, M. P. Garde, and A. Lopez-Martin, "Super class AB transconductor with slew-rate enhancement using QFG MOS techniques," in *Proc. Eur. Conf. Circuit Theory Design (ECCTD)*, Sep. 2017, pp. 1–4, doi: 10.1109/ECCTD.2017.8093308.

- [40] F. Khateb, A. Lahiri, C. Psychalinos, M. Kumngern, and T. Kulej, "Digitally programmable low-voltage highly linear transconductor based on promising CMOS structure of differential difference current conveyor," AEU Int. J. Electron. Commun., vol. 69, no. 7, pp. 1010–1017, Jul. 2015, doi: 10.1016/j.aeue.2015.03.005.

- [41] F. Khateb, T. Kulej, M. Kumngern, and C. Psychalinos, "Multiple-input bulk-driven MOS transistor for low-voltage low-frequency applications," *Circuits, Syst., Signal Process.*, vol. 38, no. 6, pp. 2829–2845, Jun. 2019, doi: 10.1007/s00034-018-0999-x.

- [42] F. Khateb, T. Kulej, H. Veldandi, and W. Jaikla, "Multiple-input bulk-driven quasi-floating-gate MOS transistor for low-voltage low-power integrated circuits," AEU Int. J. Electron. Commun., vol. 100, pp. 32–38, Feb. 2019, doi: 10.1016/j.aeue.2018.12.023.

- [43] F. Khateb, T. Kulej, M. Kumngern, W. Jaikla, and R. K. Ranjan, "Comparative performance study of multiple-input bulk-driven and multiple-input bulk-driven quasi-floating-gate DDCCs," AEU Int. J. Electron. Commun., vol. 108, pp. 19–28, Aug. 2019, doi: 10.1016/j.aeue.2019.06.003.

- [44] M. Kumngern, T. Kulej, V. Stopjakova, and F. Khateb, "0.5 v sixth-order chebyshev band-pass filter based on multiple-input bulk-driven OTA," AEU Int. J. Electron. Commun., vol. 111, Nov. 2019, Art. no. 152930, doi: 10.1016/j.aeue.2019.152930.

- [45] M. Kumngern, T. Kulej, F. Khateb, V. Stopjakova, and R. K. Ranjan, "Nanopower multiple-input DTMOS OTA and its applications to highorder filters for biomedical systems," AEU-Int. J. Electron. Commun., vol. 130, Feb. 2021, Art. no. 153576, doi: 10.1016/j.aeue.2020.153576.

- [46] M. Kumngern, N. Aupithak, F. Khateb, and T. Kulej, "0.5V fifth-order butterworth low-pass filter using multiple-input OTA for ECG applications," *Sensors*, vol. 20, no. 24, p. 7343, 2020, doi: 10.3390/s20247343.

- [47] W. Jaikla, F. Khateb, M. Kumngern, T. Kulej, R. K. Ranjan, and P. Suwanjan, "0.5 v fully differential universal filter based on multiple input OTAs," *IEEE Access*, vol. 8, pp. 187832–187839, 2020, doi: 10.1109/ACCESS.2020.3030239.

- [48] L. P. Huelsman, Active and Analog Filter Design. New York, NY, USA: McGraw-Hill, 1993.

**PIPAT PROMMEE** (Senior Member, IEEE) received the M.Eng. and D.Eng. degrees in electrical engineering from the Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok, Thailand, in 1995 and 2002, respectively. He was a Senior Engineer with CAT Telecom Plc., from 1992 to 2003. Since 2003, he has been a Faculty Member with KMITL. He is currently an Associate Professor with the Department of Telecommunications Engineering,

KMITL. He is the author or the coauthor of more than 80 publications in journals and proceedings of international conferences. His research interests include analog signal processing, analog filter design, fractional-order systems, and CMOS analog integrated circuit design. He is a Committee Member of the Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology Association of Thailand (ECTI), Thailand. He served as a Guest Editor for the Special Issue on Selected Papers from the 17th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON 2020) of an AEÜ—International Journal of Electronics and Communications.

KHUNANON KARAWANICH received the B.Eng. degree in electrical engineering from the Faculty of Engineering, Silpakorn University, Thailand, in 2018. He is currently pursuing the M.Eng. degree in telecommunications engineering with KMITL. His research interests include communication circuits and systems, analog signal processing, and chaotic system designs.

**FABIAN KHATEB** received the M.Sc. and Ph.D. degrees in electrical engineering and communication and also in business and management from the Brno University of Technology, Czech Republic, in 2002, 2003, 2005, and 2007, respectively. He is currently a Professor with the Department of Microelectronics, Faculty of Electrical Engineering and Communication, Brno University of Technology, and the Department of Information and Communication Technology in Medicine, Faculty

of Biomedical Engineering, Czech Technical University in Prague. He has expertise in new principles of designing low-voltage low-power analog circuits, particularly biomedical applications. He holds five patents. He has authored or coauthored over 100 publications in journals and proceedings of international conferences. He is a member of the Editorial Board of Microelectronics Journal, Sensors, Electronics, and Journal of Low Power Electronics and Applications. He is also an Associate Editor of IEEE Access, Circuits, Systems and Signal Processing, IET Circuits, Devices and Systems, and International Journal of Electronics. He was a Lead Guest Editor for the Special Issues on Low Voltage Integrated Circuits and Systems on Circuits, Systems and Signal Processing in 2017, IET Circuits, Devices and Systems in 2018, and Microelectronics Journal in 2019. He was also a Guest Editor for the Special Issue on Current-Mode Circuits and Systems; Recent Advances, Design and Applications of International Journal of Electronics and Communications in 2017.

**TOMASZ KULEJ** received the M.Sc. and Ph.D. degrees (Hons.) from the Gdańsk University of Technology, Gdańsk, Poland, in 1990 and 1996, respectively. He was a Senior Design Analysis Engineer with Polish branch of Chipworks Inc., Ottawa, Canada. He is currently an Associate Professor with the Department of Electrical Engineering, Częstochowa University of Technology, Poland, where he conducts lectures on electronics fundamentals, analog circuits, and computer aided

design. He has authored or coauthored over 80 publications in peer-reviewed journals and conferences. He holds three patents. His recent research interests include analog integrated circuits in CMOS technology, with emphasis to low-voltage and low-power solutions. He serves as an Associate Editor for Circuits, Systems and Signal Processing and IET Circuits, Devices and Systems. He was a Guest Editor for the Special Issues on Low Voltage Integrated Circuits on Circuits Systems and Signal Processing in 2017, IET Circuits, Devices and Systems in 2018, and Microelectronics Journal in 2019.

. .